CAT1021, CAT1022, CAT1023

www.onsemi.com

11

Page Write

The CAT1021/22/23 writes up to 16 bytes of data in a

single write cycle, using the Page Write operation. The page

write operation is initiated in the same manner as the byte

write operation, however instead of terminating after the

initial byte is transmitted, the Master is allowed to send up

to 15 additional bytes. After each byte has been transmitted,

the CAT1021/22/23 will respond with an acknowledge and

internally increment the lower order address bits by one. The

high order bits remain unchanged.

If the Master transmits more than 16 bytes before sending

the STOP condition, the address counter ‘wraps around,’

and previously transmitted data will be overwritten.

When all 16 bytes are received, and the STOP condition

has been sent by the Master, the internal programming cycle

begins. At this point, all received data is written to the

CAT1021/22/23 in a single write cycle.

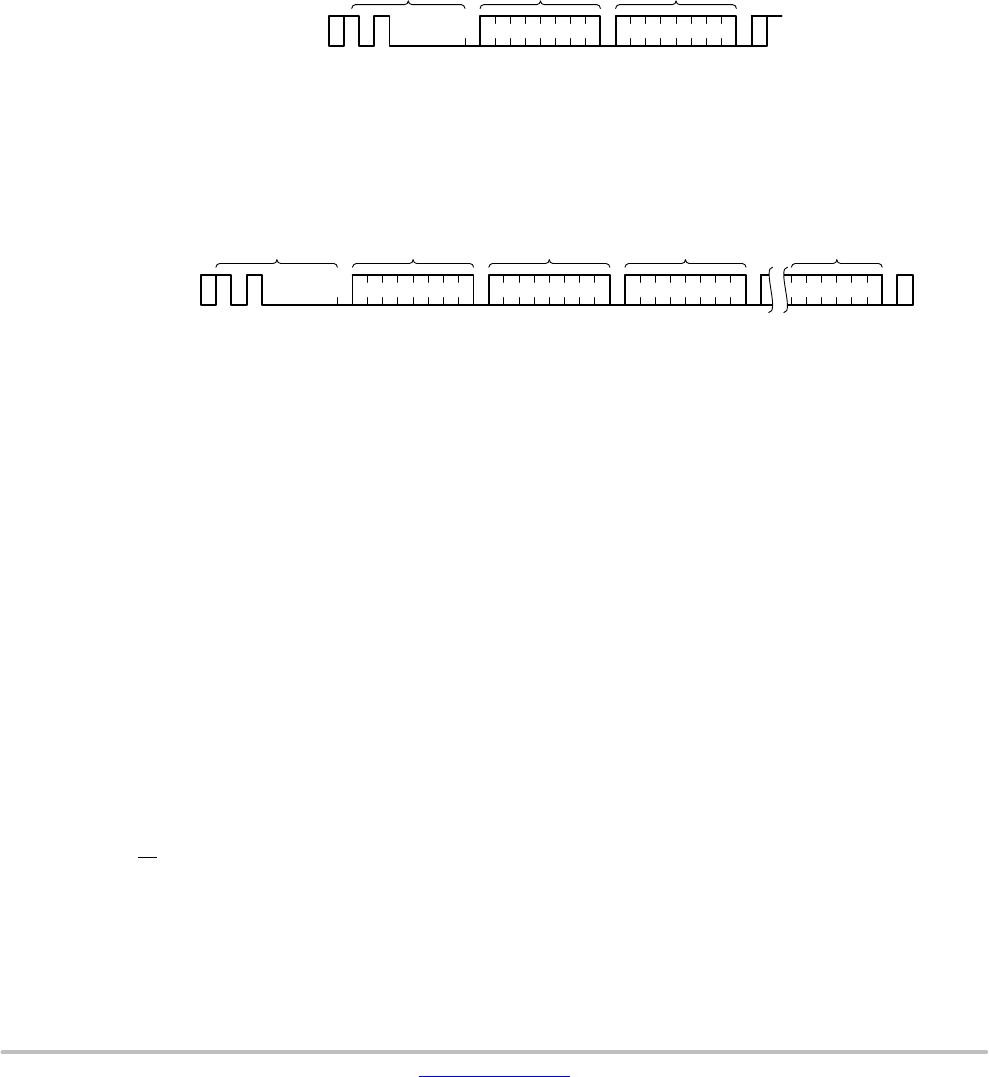

Figure 8. Byte Write Timing

BYTE

ADDRESS

SLAVE

ADDRESS

S

A

C

K

A

C

K

DATA

A

C

K

S

T

O

P

P

BUS ACTIVITY:

MASTER

SDA LINE

S

T

A

R

T

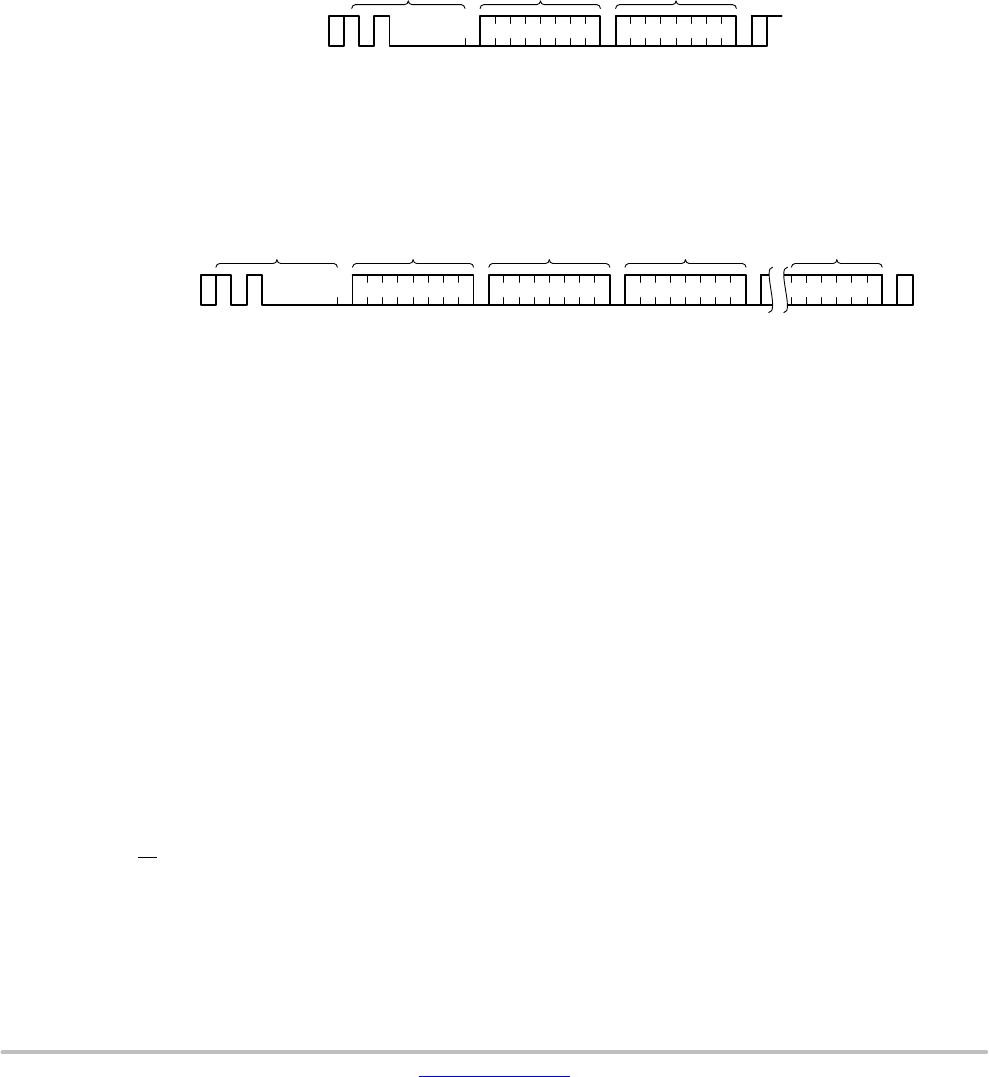

Figure 9. Page Write Timing

BUS ACTIVITY:

MASTER

SDA LINE

DATA n+15

BYTE

ADDRESS (n)

A

C

K

A

C

K

DATA n

A

C

K

S

T

O

P

S

A

C

K

DATA n+1

A

C

K

S

T

A

R

T

P

SLAVE

ADDRESS

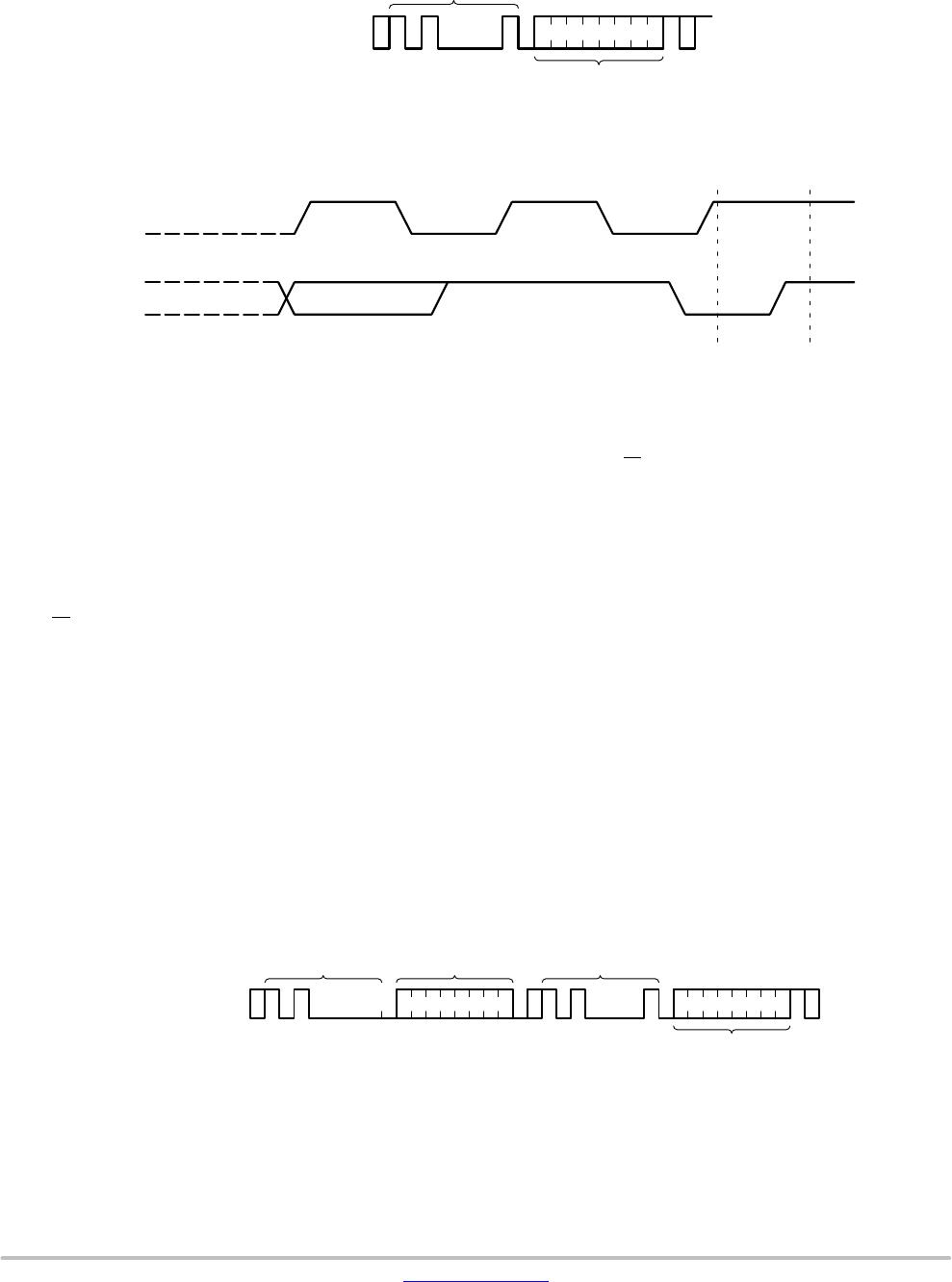

Acknowledge Polling

Disabling of the inputs can be used to take advantage of

the typical write cycle time. Once the stop condition is issued

to indicate the end of the host’s write opration, the

CAT1021/22/23 initiates the internal write cycle. ACK

polling can be initiated immediately. This involves issuing

the start condition followed by the slave address for a write

operation. If the device is still busy with the write operation,

no ACK will be returned. If a write operation has completed,

an ACK will be returned and the host can then proceed with

the next read or write operation.

WRITE PROTECTION PIN (WP)

The Write Protection feature (CAT1021 only) allows the

user to protect against inadvertent memory array

programming. If the WP pin is tied to V

CC, the entire

memory array is protected and becomes read only. The

CAT1021 will accept both slave and byte addresses, but the

memory location accessed is protected from programming

by the device’s failure to send an acknowledge after the first

byte of data is received.

READ OPERATIONS

The READ operation for the CAT1021/22/23 is initiated

in the same manner as the write operation with one

exception, the R/W

bit is set to one. Three different READ

operations are possible: Immediate/Current Address

READ, Selective/Random READ and Sequential READ.