AD830

Rev. C | Page 13 of 20

10

0%

100

90

1V 1V

00881-030

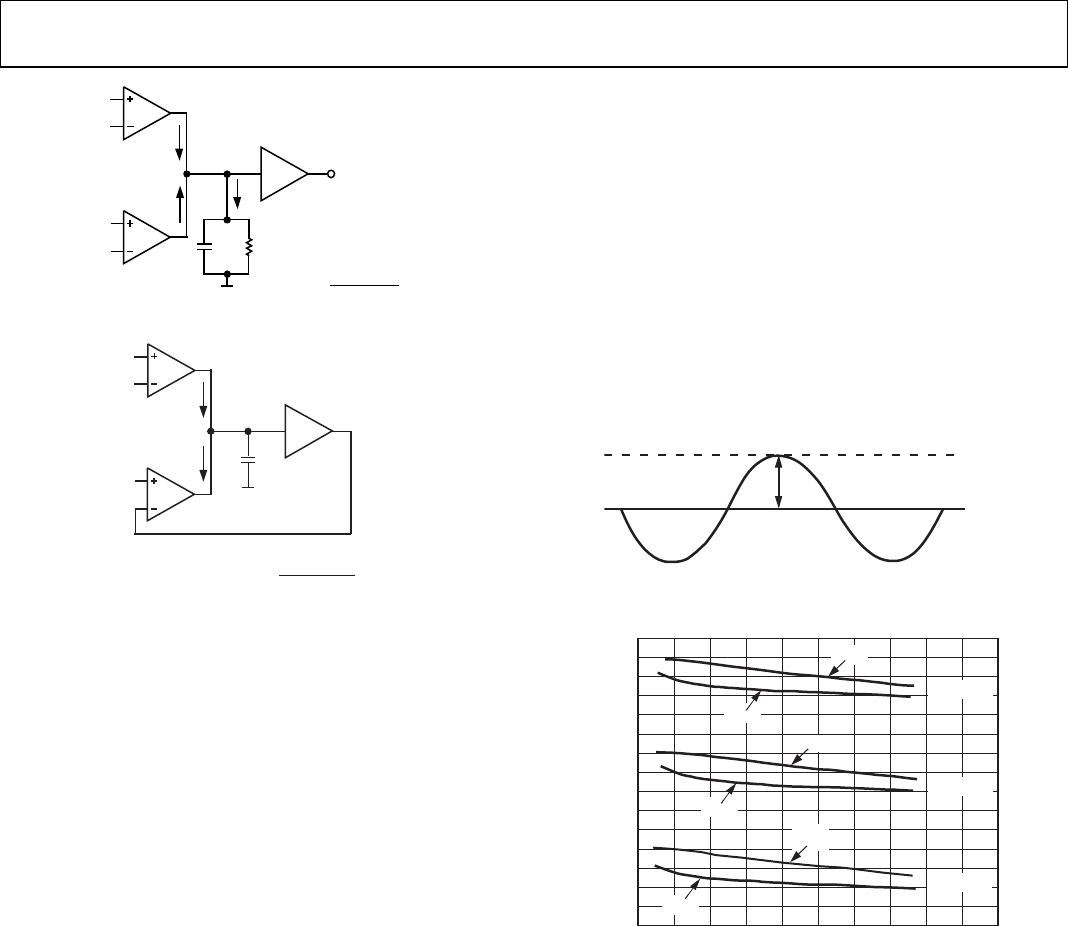

Figure 30. Clipping Behavior

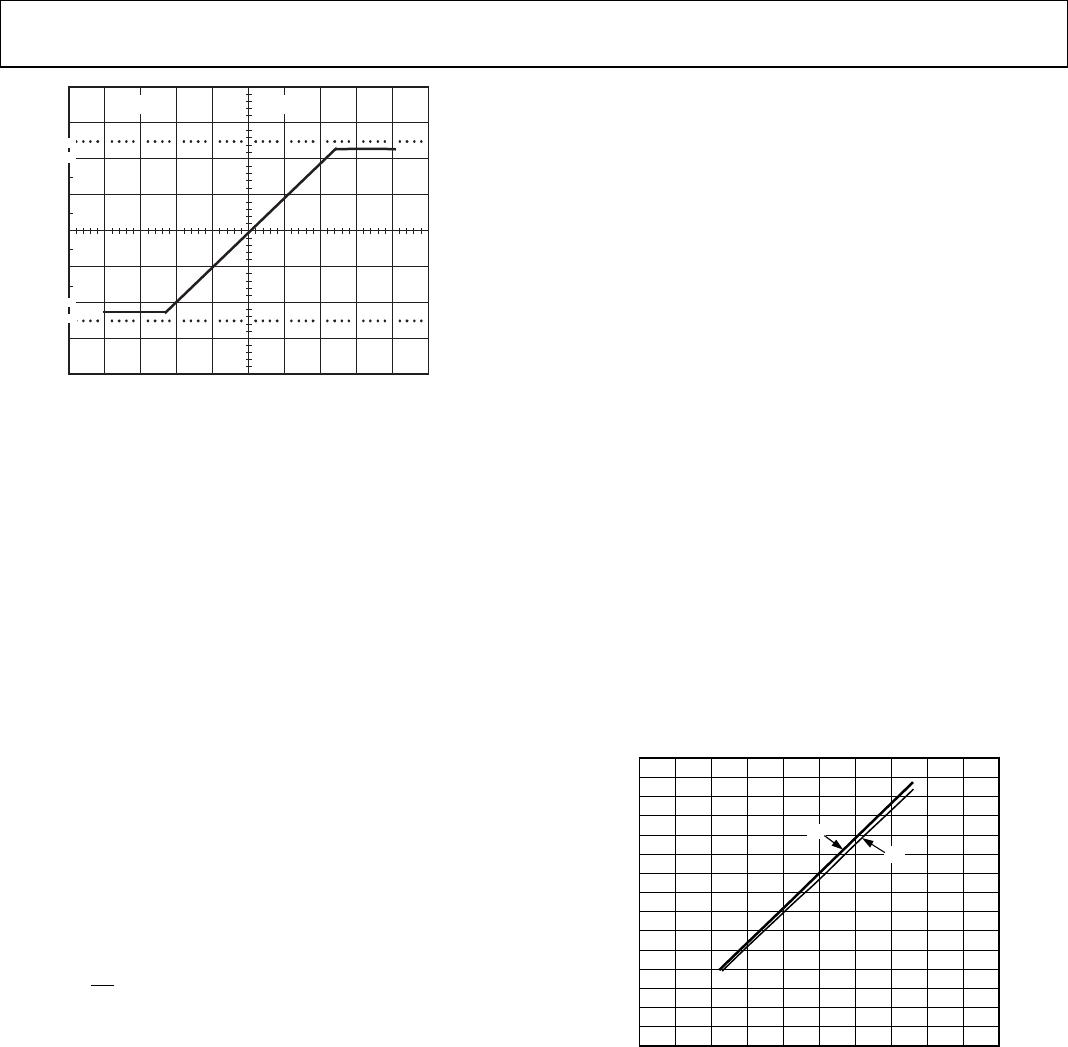

Choice of Polarity

The sign of the gain is easily selected by choosing the polarity

of the connections to the + and − inputs of the X G

M

stage.

Swapping between inverting and noninverting gain is possible

simply by reversing the input connections. The response of the

amplifier is identical in either connection, except for the sign

change.

The bandwidth, high impedance, and transient behavior of the

AD830 is symmetrical for both polarities of gain. This is very

advantageous and unlike an op amp.

Input Impedance

The relatively high input impedance of the AD830, for a

differential receiver amplifier, permits connections to modest

impedance sources without much loading or loss of common-

mode rejection. The nominal input resistance is 300 k. The

real limit to the upper value of the source resistance is in its

effect on common-mode rejection and bandwidth. If the source

resistance is in only one input, then the low frequency

common-mode rejection is lowered to ≈ R

IN

/R

S

. The source

resistance/input capacitance pole limits the bandwidth. Refer to

the following equation:

⎟

⎠

⎞

⎜

⎝

⎛

××

π

=

IN

S

CRf

2

1

Furthermore, the high frequency common-mode rejection is

additionally lowered by the difference in the frequency response

caused by the R

S

× C

IN

pole. Therefore, to maintain good low

and high frequency common-mode rejection, it is recommended

that the source resistances of the + and − inputs be matched and

of modest value (≤10 k).

Handling Bias Currents

The bias currents are typically 4 A flowing into each pin of the

G

M

stages of the AD830. Because all applications possess some

finite source resistance, the bias current through this resistor

creates a voltage drop (I

BIAS

× R

S

). The relatively high input

impedance of the AD830 permits modest values of R

S

, typically

≤10 k. If the source resistance is in only one terminal, then an

objectionable offset voltage may result, for example, 4 A × 5

k = 20 mV. Placement of an equal value resistor in series with

mismatches in the resistances, a residual offset remains and is

likely to be greater than the bias current (offset current)

mismatches.

Applying Fee

the other input cancels the offset to first order. However, due to

dback

for use with gains from 1 to 100. Gains

hat

y

830 is defined by the differential

n

ge

e

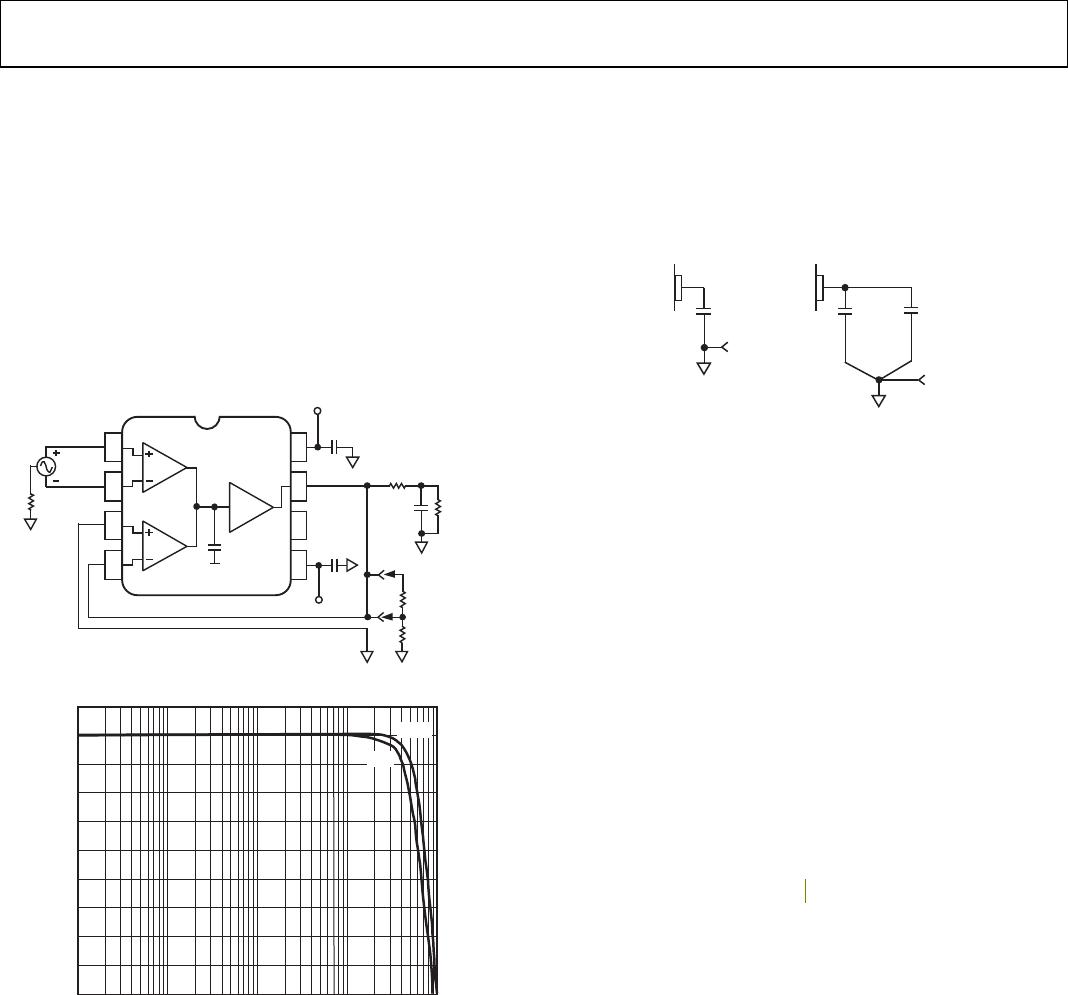

The AD830 is intended

greater than one are simply set by a pair of resistors connected

as shown in the difference amplifier (Figure 40) with gain >1.

The value of the bottom resistor, R

2

, should be kept less than

1 k to ensure that the pole formed by C

IN

and the parallel

connection of R

1

and R

2

is sufficiently high in frequency so t

it does not introduce excessive phase shift around the loop and

destabilize the amplifier. A compensating resistor, equal to the

parallel combination of R

1

and R

2

, should be placed in series

with the other Y G

M

stage input to preserve the high frequenc

common-mode rejection and to lower the offset voltage

induced by the input bias current.

Output Common Mode

The output swing of the AD

input voltage, the gain, and the output common. Depending o

the anticipated signal span, the output common (or ground)

may be set anywhere between the allowable peak output volta

in a manner similar to that described for input voltage common

mode. A plot of the peak output voltage versus the supply is

shown in Figure 31. A prediction of the common-mode rang

versus the peak output differential voltage can be easily derived

from the maximum output swing as V

OCM

= V

MAX

− V

PEAK

.

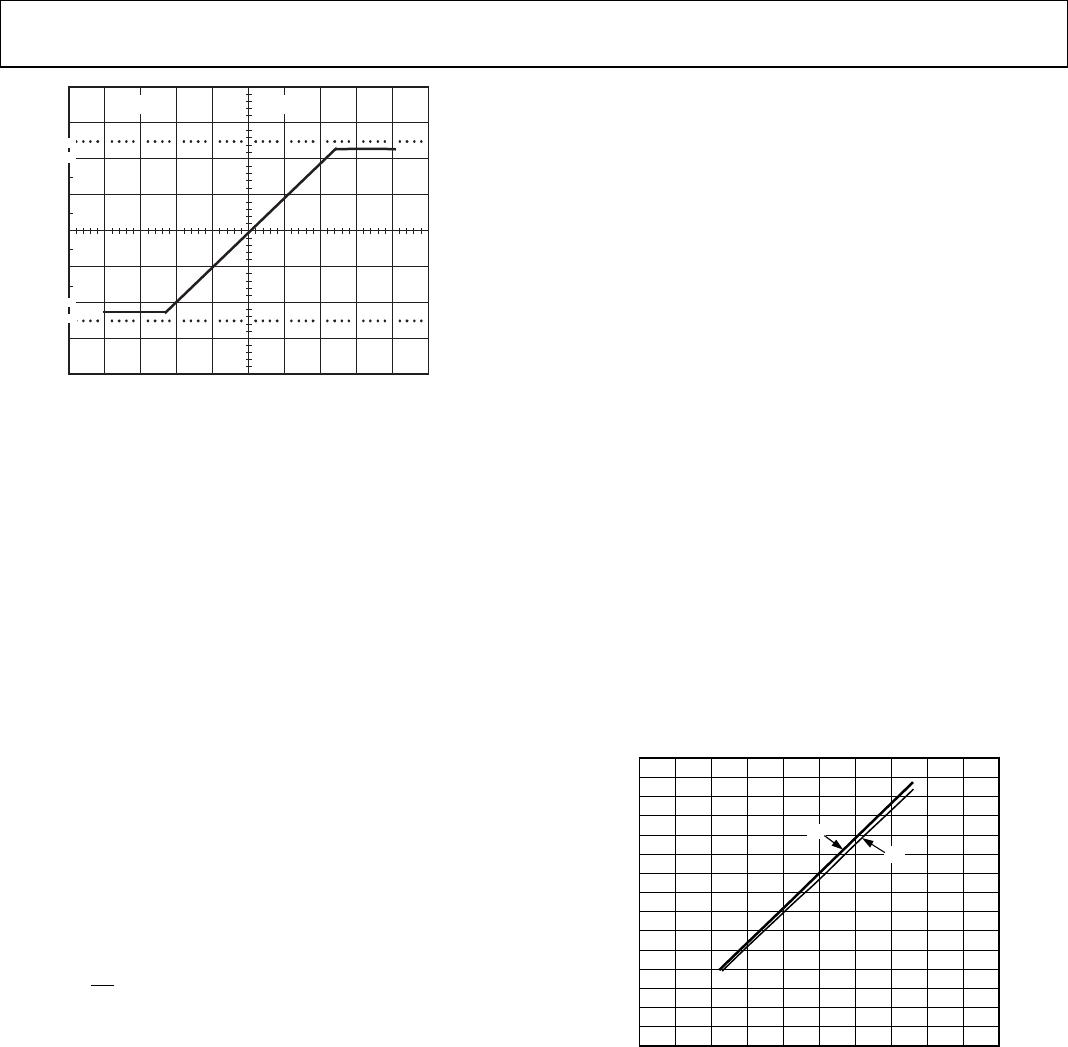

SUPPLY VOLTAGE (V)

15

0

200

MAXIMUM OUTPUT SWING (±V)

481216

6

3

12

9

V

P

V

N

00881-031

Figure 31. Maximum Output Swing vs. Supply

Output Cur

output current is set by the short-circuit

nto

rent

The absolute peak

current limiting, typically greater than 60 mA. The maximum

drive capability is rated at 50 mA but without a guarantee of

distortion performance. Best distortion performance is obtained

by keeping the output current ≤20 mA. Attempting to drive

large voltages into low valued resistances, for example, 10 V i

150 causes an apparent lowering of the limit for output signal

swing but is just the current limiting behavior.