1-Wire Signaling

The DS1990R requires strict protocols to ensure data

integrity. The protocol consists of four types of signaling

on one line: reset sequence with reset pulse and pres-

ence pulse, write-zero, write-one, and read-data.

Except for the presence pulse, the bus master initiates

all these signals.

To get from idle to active, the voltage on the 1-Wire line

needs to fall from V

PUP

to below V

ILMAX

. To get from

active to idle, the voltage needs to rise from V

ILMAX

to

above V

IHMIN

. The time it takes for the voltage to make

this rise, referenced as ε in Figure 6, depends on the

value of the pullup resistor (R

PUP

) and capacitance of

the 1-Wire network attached.

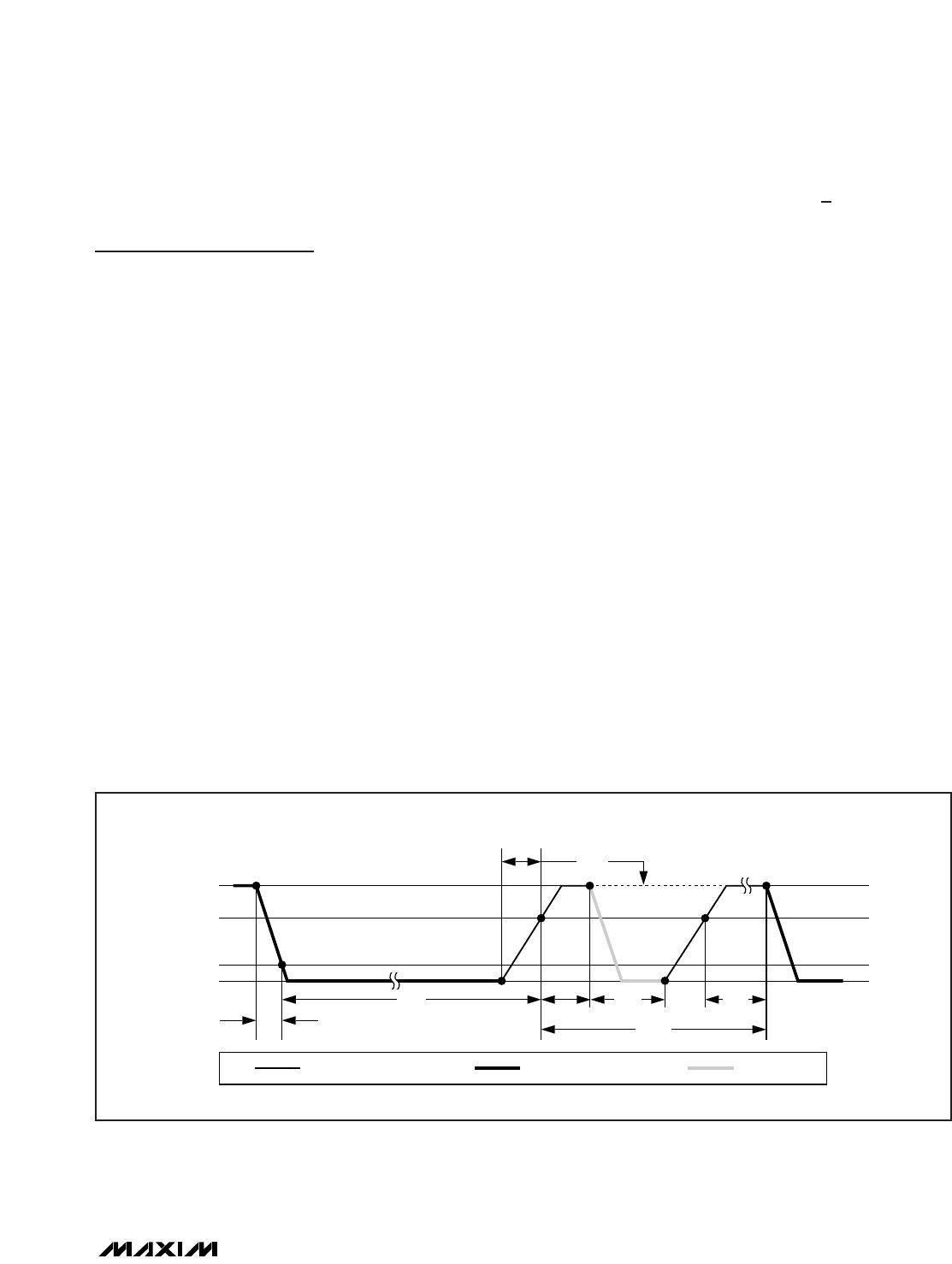

The initialization sequence required to begin any com-

munication with the DS1990R is shown in Figure 6. A

reset pulse followed by a presence pulse indicates that

the DS1990R is ready to receive a ROM function com-

mand. If the bus master uses slew-rate control on the

falling edge, it must pull down the line for t

RSTL

+ t

F

to

compensate for the edge.

After the bus master has released the line, it goes into

receive mode (Rx). Now the 1-Wire bus is pulled to

V

PUP

through the pullup resistor or, in the case of a

DS2480B driver, by active circuitry. When the V

IHMIN

is

crossed, the DS1990R waits for t

PDH

and then transmits

a presence pulse by pulling the line low for t

PDL

. To

detect a presence pulse, the master must test the logi-

cal state of the 1-Wire line at t

MSP

.

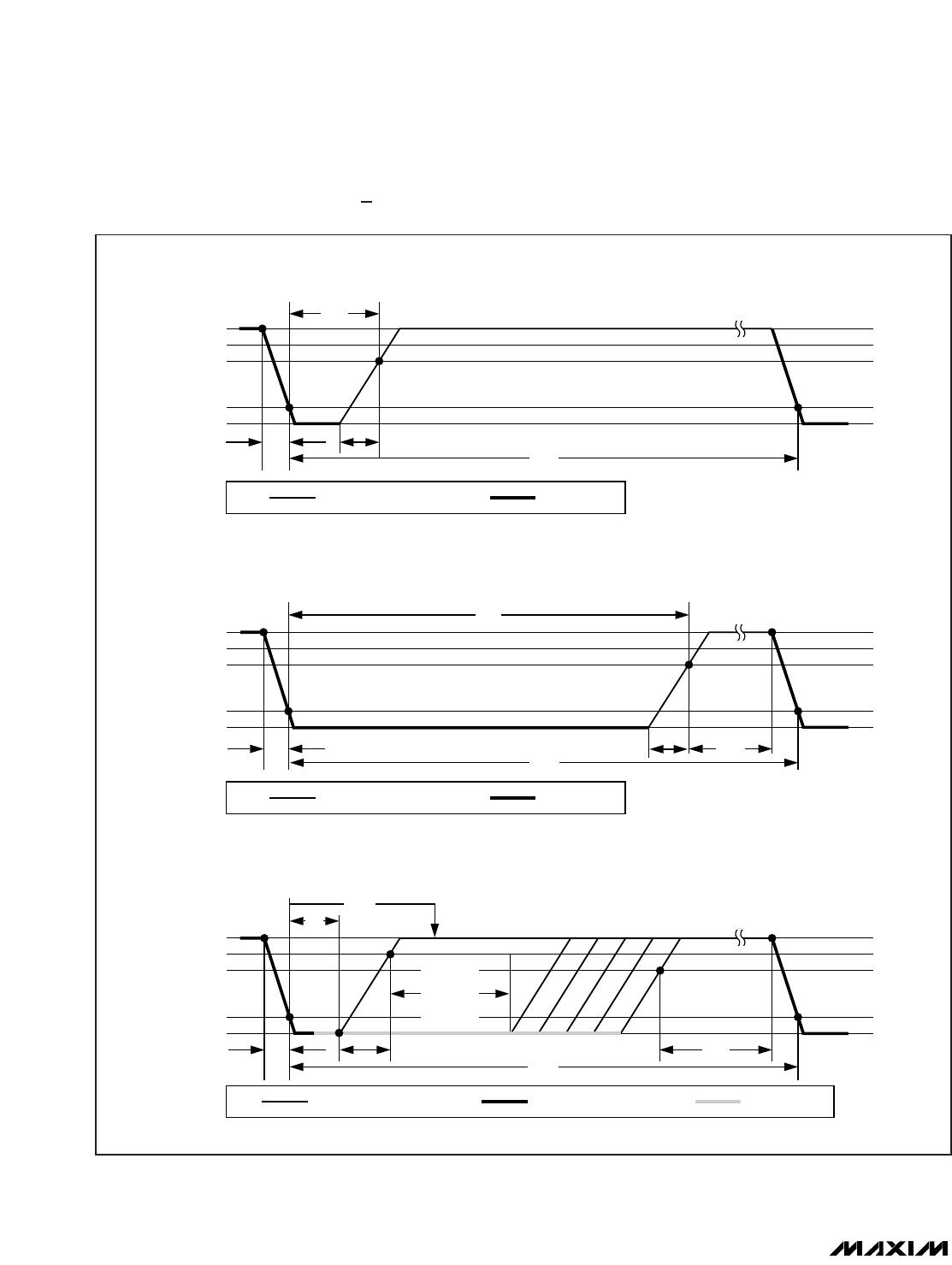

Read/Write Time Slots

Data communication with the DS1990R takes place in

time slots that carry a single bit each. Write time slots

transport data from bus master to slave. Read time

slots transfer data from slave to master. The definitions

of the write and read time slots are illustrated in

Figure 7.

All communication begins with the master pulling the

data line low. As the voltage on the 1-Wire line falls

below V

ILMAX

, the DS1990R starts its internal timing

generator that determines when the data line is sam-

pled during a write time slot and how long data is valid

during a read time slot.

Master-to-Slave

For a write-one time slot, the voltage on the data line

must have risen above V

IHMIN

after the write-one low

time t

W1LMAX

is expired. For a write-zero time slot, the

voltage on the data line must stay below V

ILMAX

until

the write-zero low time t

W0LMIN

is expired. For most reli-

able communication, the voltage on the data line

should not exceed V

ILMAX

during the entire t

W0L

win-

dow. After the voltage has risen above V

IHMIN

, the

DS1990R needs a recovery time t

REC

before it is ready

for the next time slot.

DS1990R

Serial Number i

Button

_______________________________________________________________________________________ 7