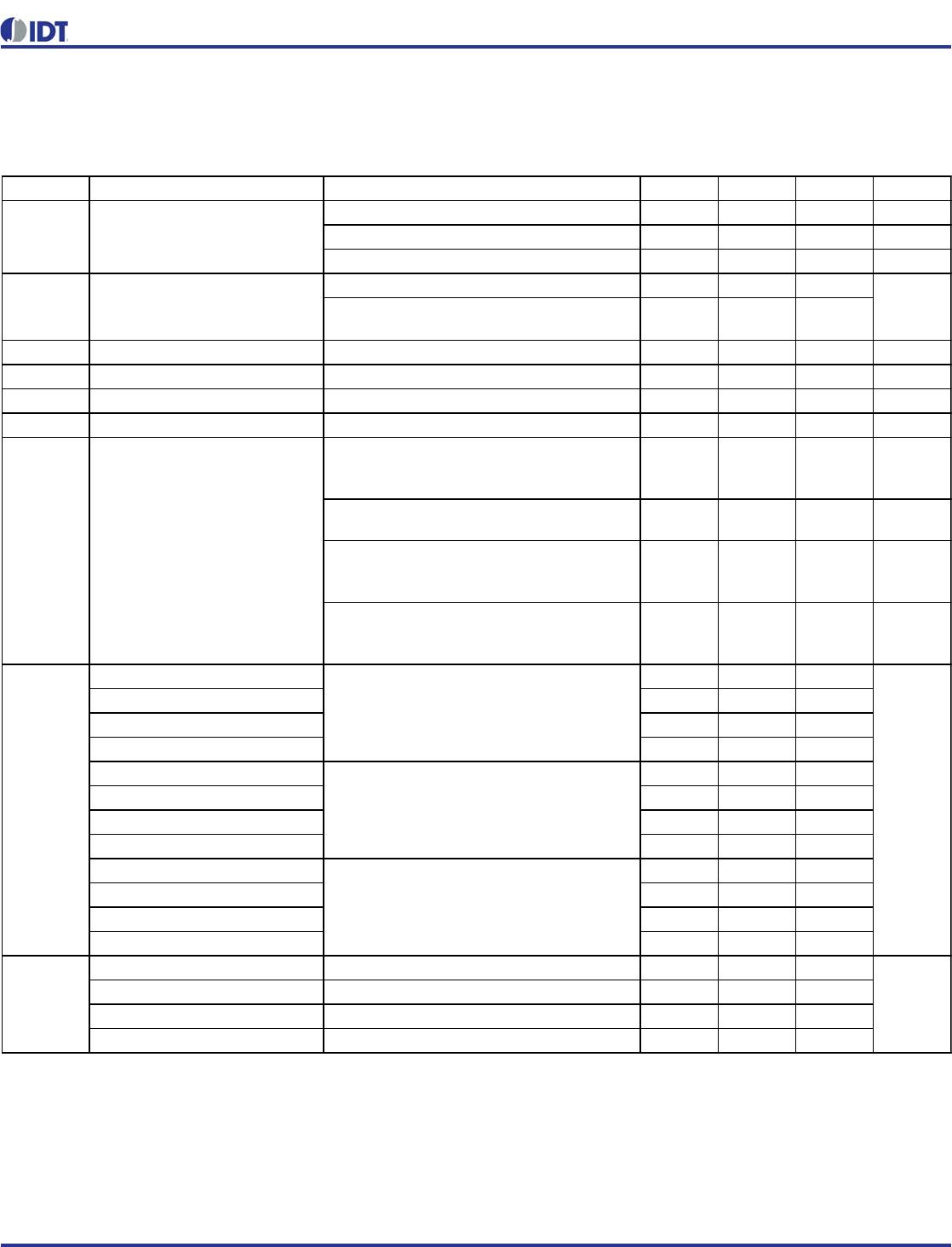

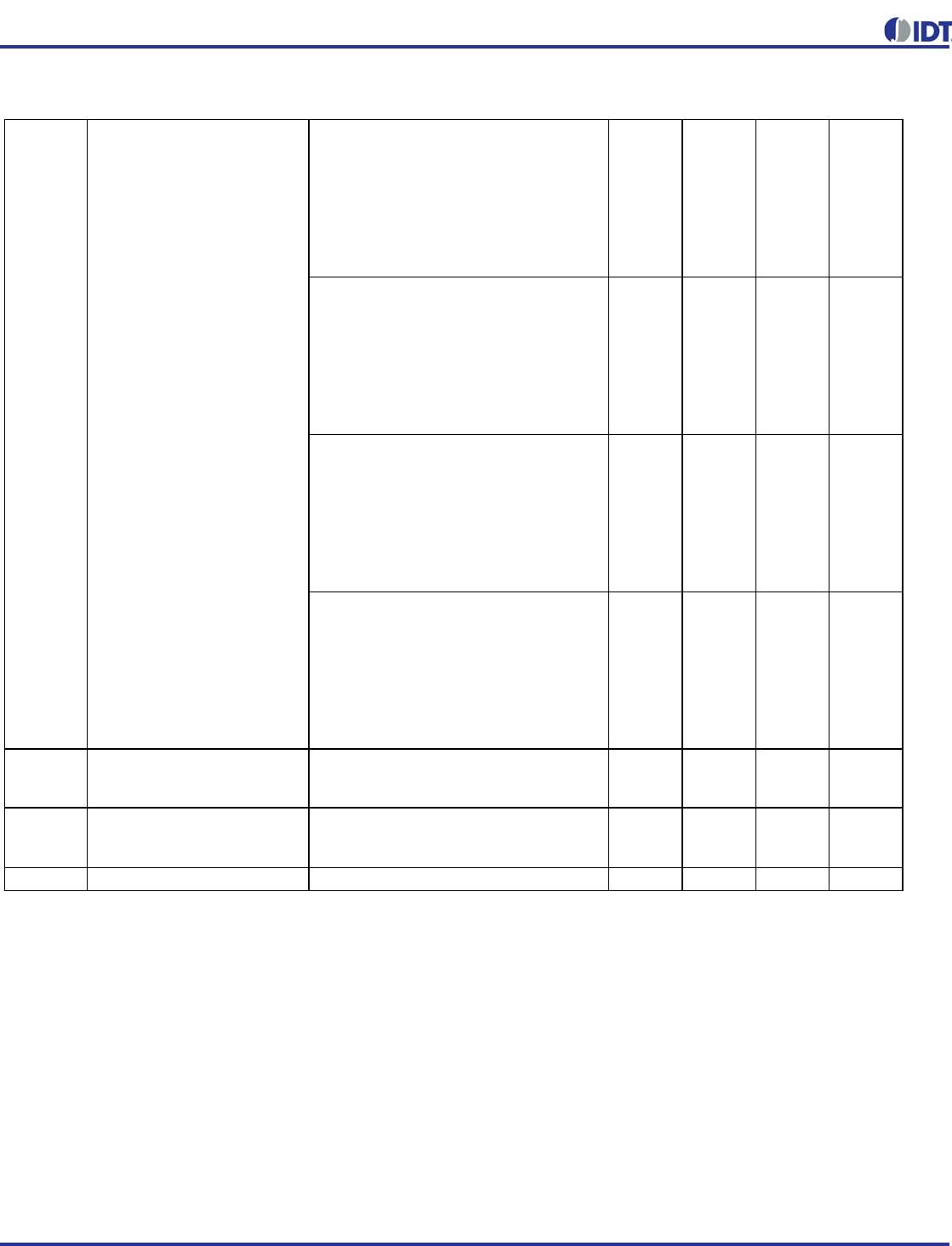

LVDS/HCSL)

1350

fVCO VCO Frequency

VCO operating frequency range

2500 2900 MHz

fPFD PFD Frequency

PFD operating frequency range 1

1

150 MHz

fBW Loop Bandwidth Input frequency = 25MHz 0.06 0.9 MHz

t2 Input Duty Cycle

Duty Cycle

45 50 55 %

Measured at VDD/2, all outputs except

Reference output OUT0, VDDOX= 2.5V or

3.3V

45 50 55 %

Measured at VDD/2, all outputs except

Reference output OUT0, VDDOX=1.8V

40 50 60 %

Measured at VDD/2, Reference output

OUT0 (5MHz - 120MHz) with 50% duty

cycle input

40 50 60 %

Measured at VDD/2, Reference output

OUT0 (150.1MHz - 200MHz) with 50% duty

cycle input

30 50 70 %

Slew Rate, SLEW[1:0] = 00

1.0

2.2

Slew Rate, SLEW[1:0] = 01

1.2

2.3

Slew Rate, SLEW[1:0] = 10

1.3

2.4

Slew Rate, SLEW[1:0] = 11

1.7

2.7

Slew Rate, SLEW[1:0] = 00

0.6

1.3

Slew Rate, SLEW[1:0] = 01

0.7

1.4

Slew Rate, SLEW[1:0] = 10

0.6

1.4

Slew Rate, SLEW[1:0] = 11

1.0

1.7

Slew Rate, SLEW[1:0] = 00

0.3

0.7

Slew Rate, SLEW[1:0] = 01

0.4

0.8

Slew Rate, SLEW[1:0] = 10

0.4

0.9

Slew Rate, SLEW[1:0] = 11

0.7

1.2

Rise Times

LVDS, 20% to 80%

300

Fall Times

LVDS, 80% to 20%

300

Rise Times

LVPECL, 20% to 80%

400

Fall Times

LVPECL, 80% to 20%

400

t4

2

t5 ps

Output Duty Cycle

Single-ended 2.5V LVCMOS output clock

rise and fall time, 20% to 80% of VDDO

(Output Load = 5 pF) VDDOX=2.5V

Single-ended 1.8V LVCMOS output clock

rise and fall time, 20% to 80% of VDDO

(Output Load = 5 pF) VDDOX=1.8V

V/ns

Single-ended 3.3V LVCMOS output clock

rise and fall time, 20% to 80% of VDDO

(Output Load = 5 pF) VDDOX=3.3V

fIN

1

Input Frequency

fOUT Output Frequency

t3

5

MHz