MC14013B

http://onsemi.com

6

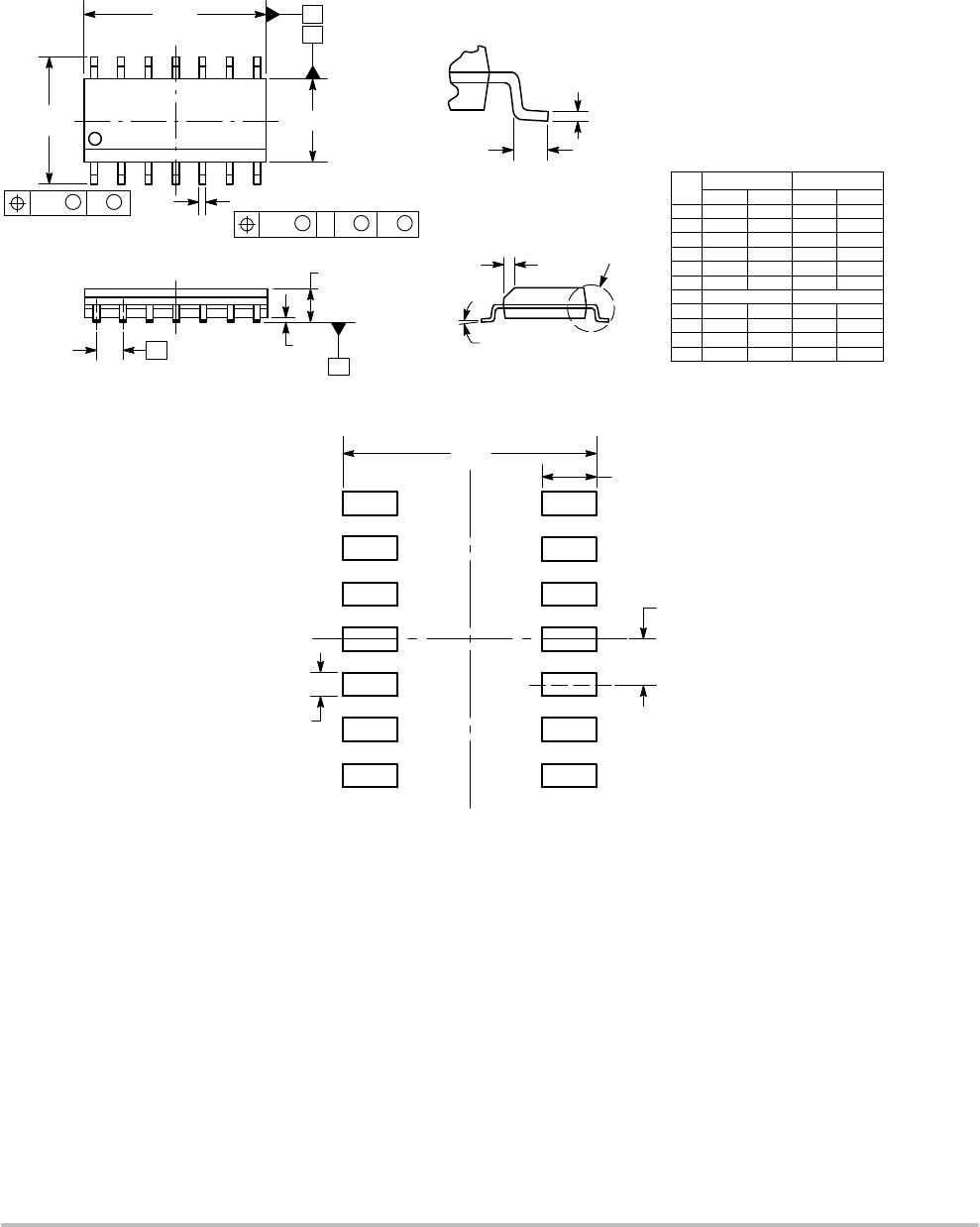

PACKAGE DIMENSIONS

SOIC−14 NB

CASE 751A−03

ISSUE K

NOTES:

1. DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE PROTRUSION

SHALL BE 0.13 TOTAL IN EXCESS OF AT

MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE

MOLD PROTRUSIONS.

5. MAXIMUM MOLD PROTRUSION 0.15 PER

SIDE.

H

14

8

71

M

0.25 B

M

C

h

X 45

SEATING

PLANE

A1

A

M

_

S

A

M

0.25 B

S

C

b

13X

B

A

E

D

e

DETAIL A

L

A3

DETAIL A

DIM MIN MAX MIN MAX

INCHESMILLIMETERS

D 8.55 8.75 0.337 0.344

E 3.80 4.00 0.150 0.157

A 1.35 1.75 0.054 0.068

b 0.35 0.49 0.014 0.019

L 0.40 1.25 0.016 0.049

e 1.27 BSC 0.050 BSC

A3 0.19 0.25 0.008 0.010

A1 0.10 0.25 0.004 0.010

M 0 7 0 7

H 5.80 6.20 0.228 0.244

h 0.25 0.50 0.010 0.019

__ __

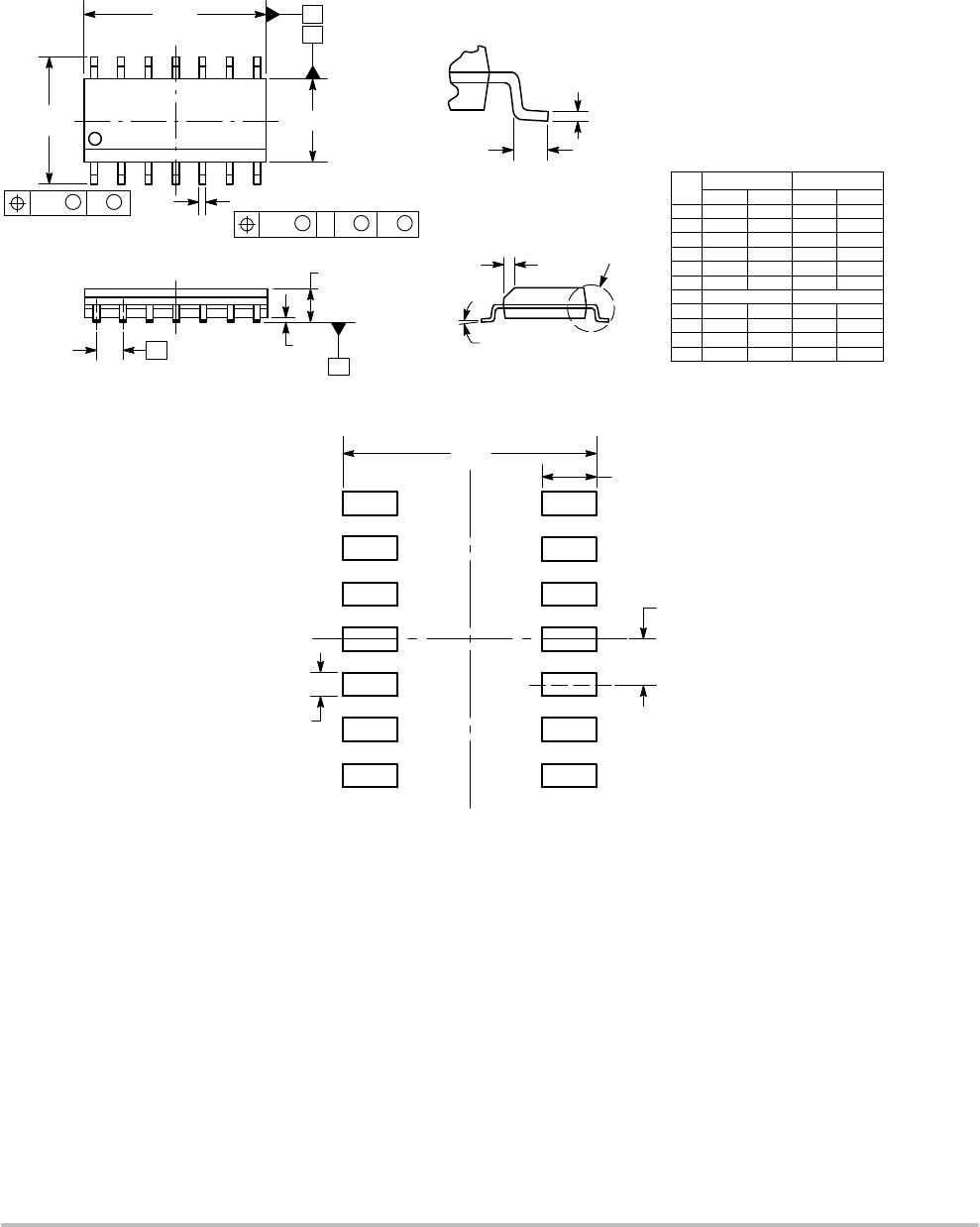

6.50

14X

0.58

14X

1.18

1.27

DIMENSIONS: MILLIMETERS

1

PITCH

SOLDERING FOOTPRINT*

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.