Data Sheet AD8000

Rev. C | Page 5 of 17

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage 12.6 V

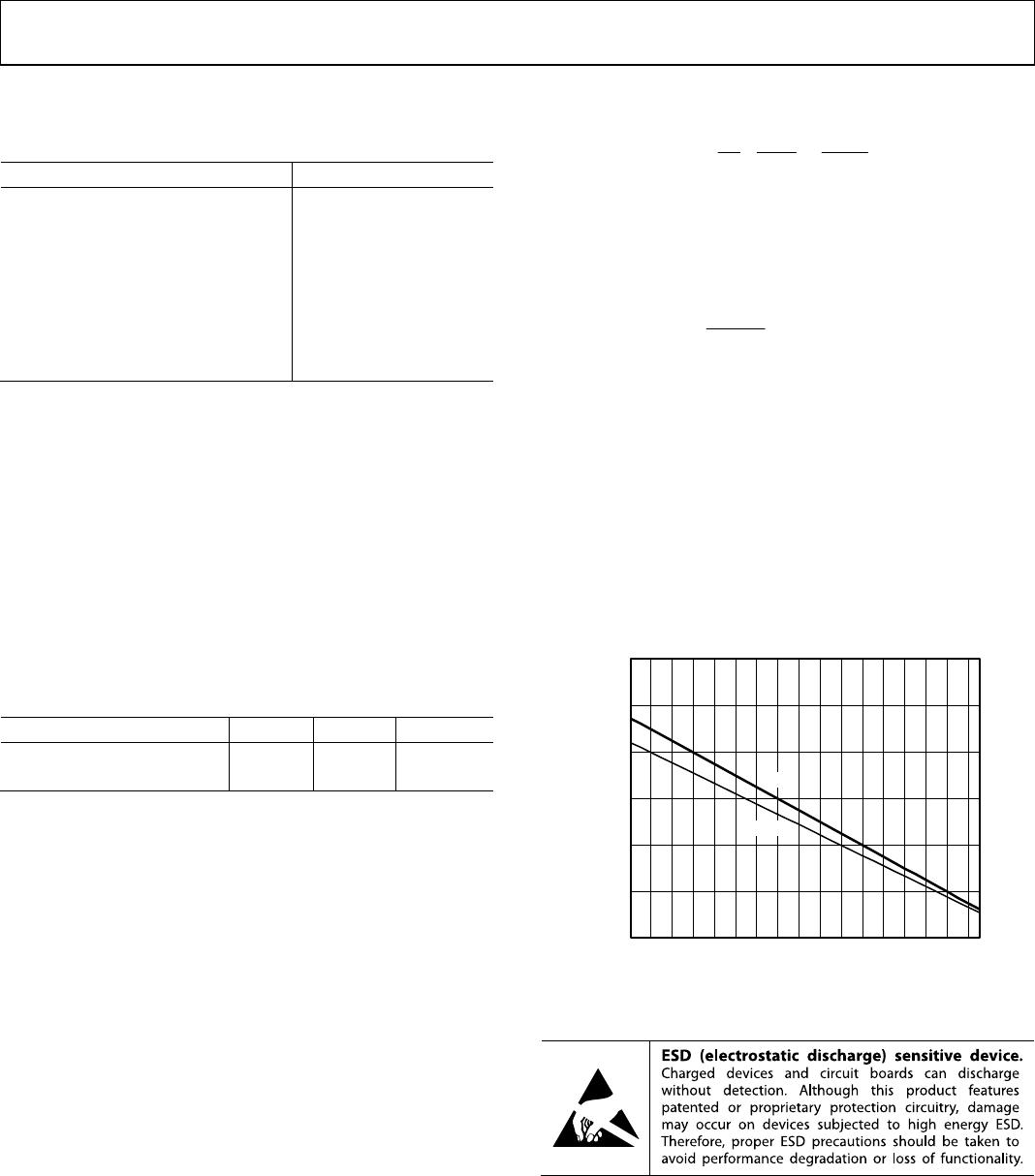

Power Dissipation See Figure 4

Common-Mode Input Voltage Range −V

S

− 0.7 V to +V

S

+ 0.7 V

Differential Input Voltage

V

S

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +125°C

Lead Temperature (Soldering, 10 sec) 300°C

Junction Temperature 150°C

Stresses at or above those listed under Absolute Maximum Ratings

may cause permanent damage to the product. This is a stress

rating only; functional operation of the product at these or any

other conditions above those indicated in the operational section of

this specification is not implied. Operation beyond the maximum

operating conditions for extended periods may affect product

reliability.

THERMAL RESISTANCE

θ

JA

is specified for the worst-case conditions, that is, θ

JA

is speci-

fied for device soldered in the circuit board for surface-mount

packages.

Table 4. Thermal Resistance

Package Type θ

JA

θ

JC

Unit

8-Lead SOIC 80 30 °C/W

3 mm × 3 mm LFCSP 93 35 °C/W

MAXIMUM POWER DISSIPATION

The maximum safe power dissipation for the AD8000 is limited

by the associated rise in junction temperature (T

J

) on the die. At

approximately 150C, which is the glass transition temperature,

the properties of the plastic change. Even temporarily exceeding

this temperature limit can change the stresses that the package

exerts on the die, permanently shifting the parametric performance

of the AD8000. Exceeding a junction temperature of 175C for

an extended period of time can result in changes in silicon de-

vices, potentially causing degradation or loss of functionality.

The power dissipated in the package (P

D

) is the sum of the qui-

escent power dissipation and the power dissipated in the die

due to the AD8000 drive at the output. The quiescent power is

the voltage between the supply pins (V

S

) times the quiescent

current (I

S

).

P

D

= Quiescent Power + (Total Drive Power − Load Power)

L

2

OUT

L

OUTS

SS

D

R

V

–

R

V

2

V

IVP

Consider the RMS output voltages. If R

L

is referenced to −V

S

, as

in single-supply operation, the total drive power is V

S

× I

OUT

. If

the rms signal levels are indeterminate, consider the worst case,

when V

OUT

= V

S

/4 for R

L

to midsupply.

L

S

SS

D

R

/V

IVP

2

4

In single-supply operation with R

L

referenced to −V

S

, worst case

is V

OUT

= V

S

/2.

Airflow increases heat dissipation, effectively reducing θ

JA

. Also,

more metal directly in contact with the package leads and exposed

paddle from metal traces, through holes, ground, and power

planes reduces θ

JA

.

Figure 4 shows the maximum safe power dissipation in the

package vs. the ambient temperature for the exposed paddle

SOIC (80°C/W) and the LFCSP (93°C/W) package on a JEDEC

standard 4-layer board. θ

JA

values are approximations.

0

0.5

1.0

1.5

2.0

2.5

3.0

MAXIMUM POWER DISSIPATION (W)

05321-063

–30 –20 –10 0 10 20 40 8030 50 60 70 10090 120110

AMBIENT TEMPERATURE (C)

SOIC

LFCSP

–40

Figure 4. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

ESD CAUTION