11

LTC3410

3410fb

APPLICATIO S I FOR ATIO

WUUU

the junction temperature reaches approximately 150°C,

both power switches will be turned off and the SW node

will become high impedance.

To avoid the LTC3410 from exceeding the maximum

junction temperature, the user will need to do some

thermal analysis. The goal of the thermal analysis is to

determine whether the power dissipated exceeds the

maximum junction temperature of the part. The tempera-

ture rise is given by:

T

R

= (P

D

)(θ

JA

)

where P

D

is the power dissipated by the regulator and

θ

JA

is the thermal resistance from the junction of the die to

the ambient temperature.

The junction temperature, T

J

, is given by:

T

J

= T

A

+ T

R

where T

A

is the ambient temperature.

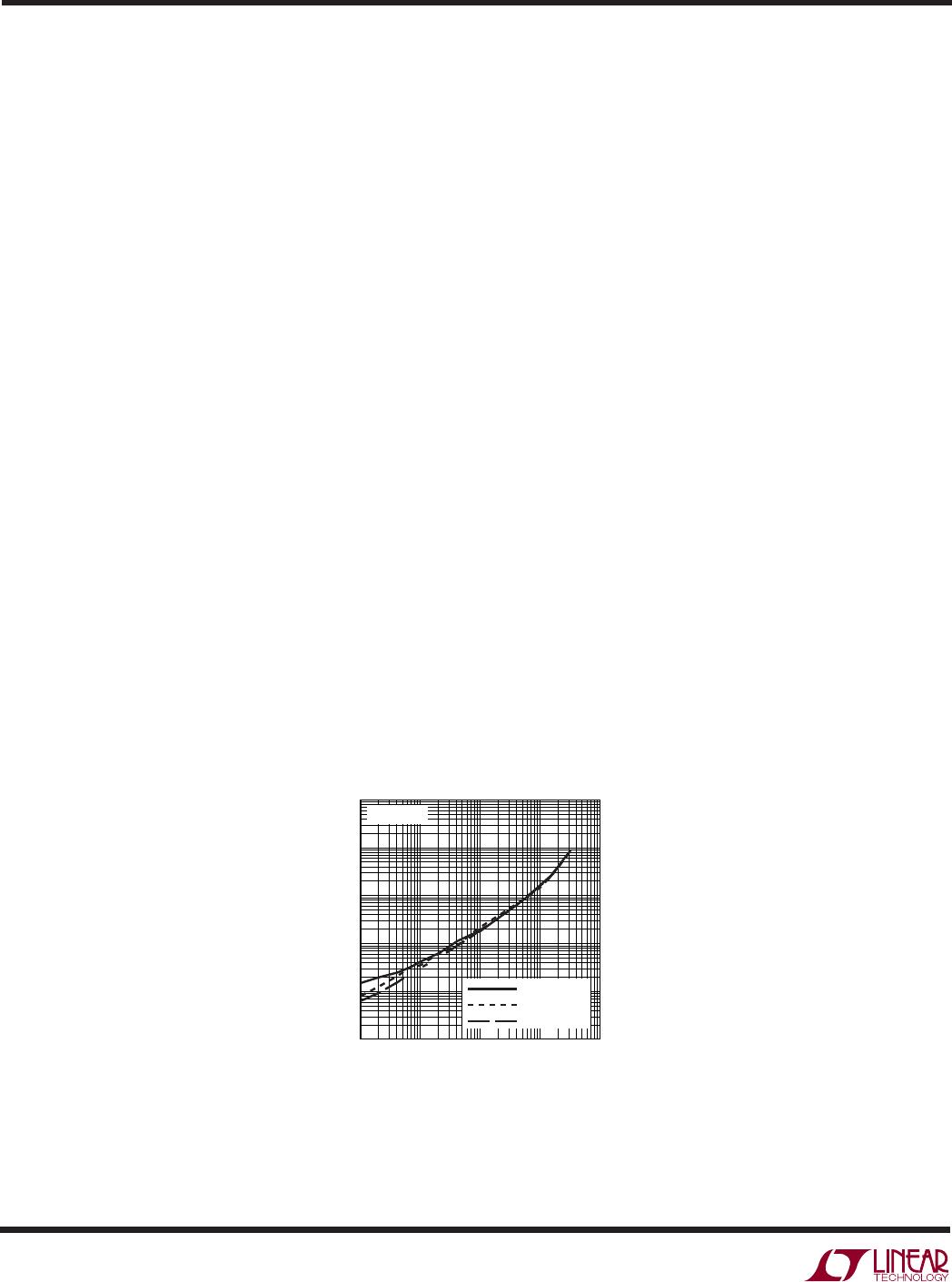

As an example, consider the LTC3410 in dropout at an

input voltage of 2.7V, a load current of 300mA and an

ambient temperature of 70°C. From the typical perfor-

mance graph of switch resistance, the R

DS(ON)

of the

P-channel switch at 70°C is approximately 1.0Ω.

Therefore, power dissipated by the part is:

P

D

= I

LOAD

2

• R

DS(ON)

= 90mW

For the SC70 package, the θ

JA

is 250°C/W. Thus, the

junction temperature of the regulator is:

T

J

= 70°C + (0.09)(250) = 92.5°C

which is well below the maximum junction temperature

of 125°C.

Note that at higher supply voltages, the junction tempera-

ture is lower due to reduced switch resistance (R

DS(ON)

).

Checking Transient Response

The regulator loop response can be checked by looking at

the load transient response. Switching regulators take

several cycles to respond to a step in load current. When

a load step occurs, V

OUT

immediately shifts by an amount

equal to (∆I

LOAD

• ESR), where ESR is the effective series

resistance of C

OUT

. ∆I

LOAD

also begins to charge or

discharge C

OUT

, which generates a feedback error signal.

The regulator loop then acts to return V

OUT

to its steady-

state value. During this recovery time V

OUT

can be moni-

tored for overshoot or ringing that would indicate a stability

problem. For a detailed explanation of switching control

loop theory, see Application Note 76.

A second, more severe transient is caused by switching in

loads with large (>1µF) supply bypass capacitors. The

discharged bypass capacitors are effectively put in parallel

with C

OUT

, causing a rapid drop in V

OUT

. No regulator can

deliver enough current to prevent this problem if the load

switch resistance is low and it is driven quickly. The only

solution is to limit the rise time of the switch drive so that

the load rise time is limited to approximately (25 • C

LOAD

).

Thus, a 10µF capacitor charging to 3.3V would require a

250µs rise time, limiting the charging current to about

130mA.

PC Board Layout Checklist

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation of the

LTC3410. These items are also illustrated graphically in

Figures 4 and 5. Check the following in your layout:

1. The power traces, consisting of the GND trace, the SW

trace and the V

IN

trace should be kept short, direct and

wide.