ADN4690E/ADN4692E/ADN4694E/ADN4695E Data Sheet

Rev. B | Page 12 of 20

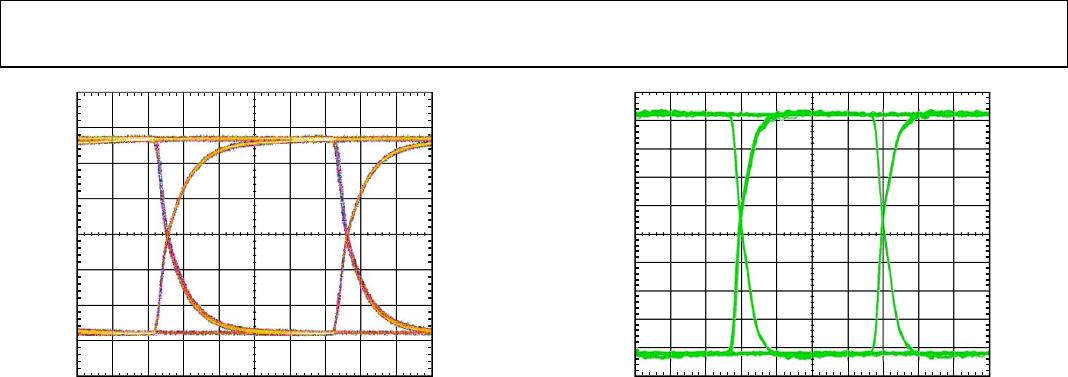

DRIVER TIMING MEASUREMENTS

DI

NOTES

1. C1, C2, AND C3

ARE 20% AND INCLUDE PROBE/STR

AY

CA

PACI

T

ANCE < 2cm FROM DUT

.

2. R1 IS 1%, MET

AL

FILM, SUR

FACE MOUN

T

,

<2cm FROM DUT.

OUT

C1

1pF

C3

0.5pF

C2

1pF

10471-022

R1

50Ω

A/Y

B/Z

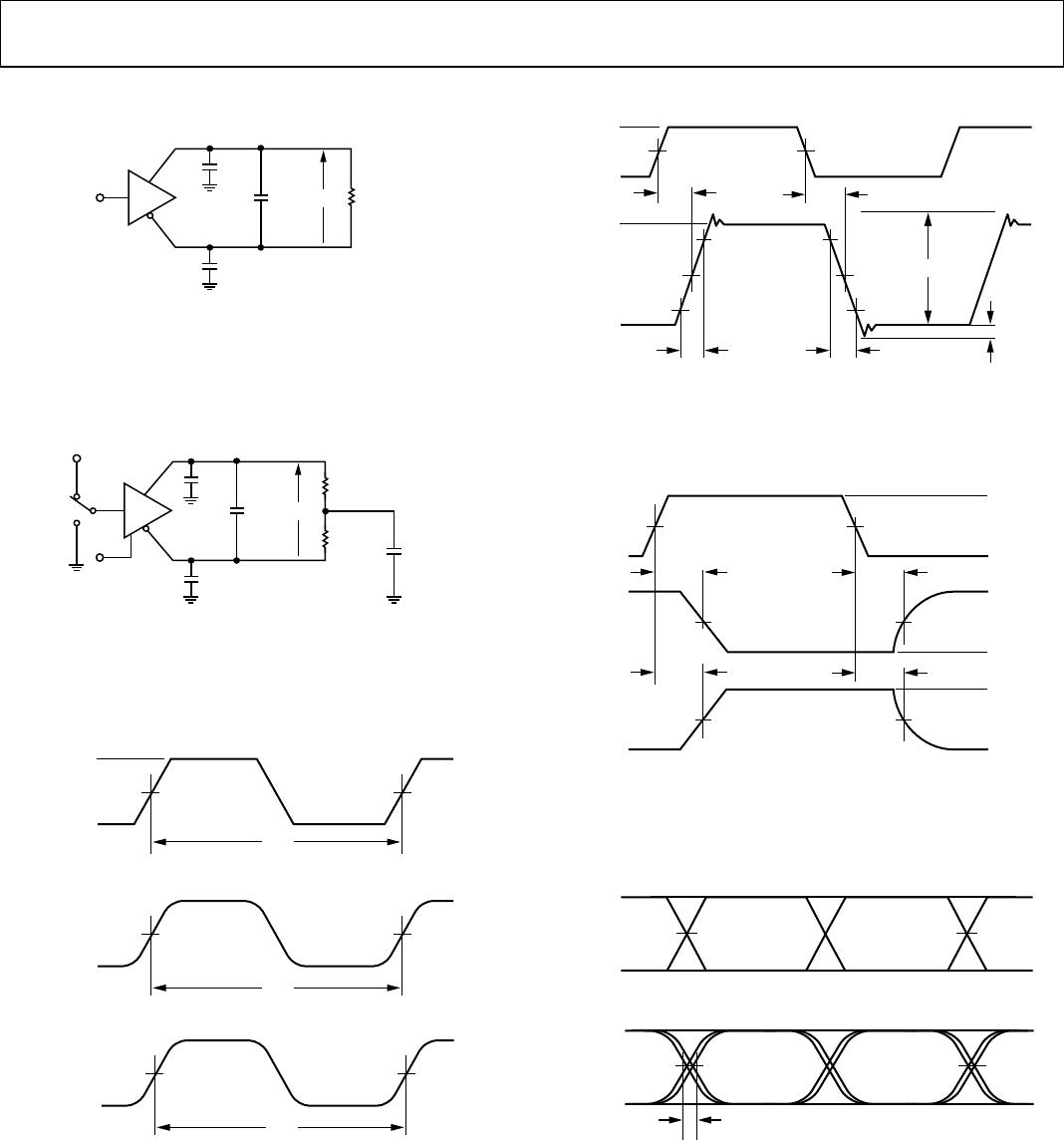

Figure 23. Driver Timing Measurement

DI

DE

S1

V

CC

NOTES

1. C1, C2, C3, AND C4 ARE 20% AND INCLUDE PROBE/STRAY

CAPACITANCE < 2cm FROM DUT.

2. R1 AND R2 ARE 1%, METAL FILM, SURFACE MOUNT,

<2cm FROM DUT.

R1

24.9Ω

C1

1pF

C2

1pF

C3

2.5pF

R2

24.9Ω

10471-023

C4

0.5pF

OUT

A/Y

B/Z

Figure 24. Driver Enable/Disable Time Test Circuit

NOTES

1. INPUT PULSE GENERATOR: AGILENT 8304A STIMULUS SYSTEM;

50MHz; 50% ± 1% DUTY CYCLE.

2. MEASURED USING TEK TDS6604 WITH TDSJIT3 SOFTWARE.

V

CC

/2 V

CC

/2

V

CC

0V

1/f0

INPUT

(CLOCK)

10471-024

0V 0V

1/f0

OUTPUT

V

A

– V

B

OR

V

Y

– V

Z

(IDEAL)

0V 0V

t

c(n)

t

J(PER)

= |

t

c(n)

– 1/f0|

OUTPUT

V

A

– V

B

OR

V

Y

– V

Z

(ACTUAL)

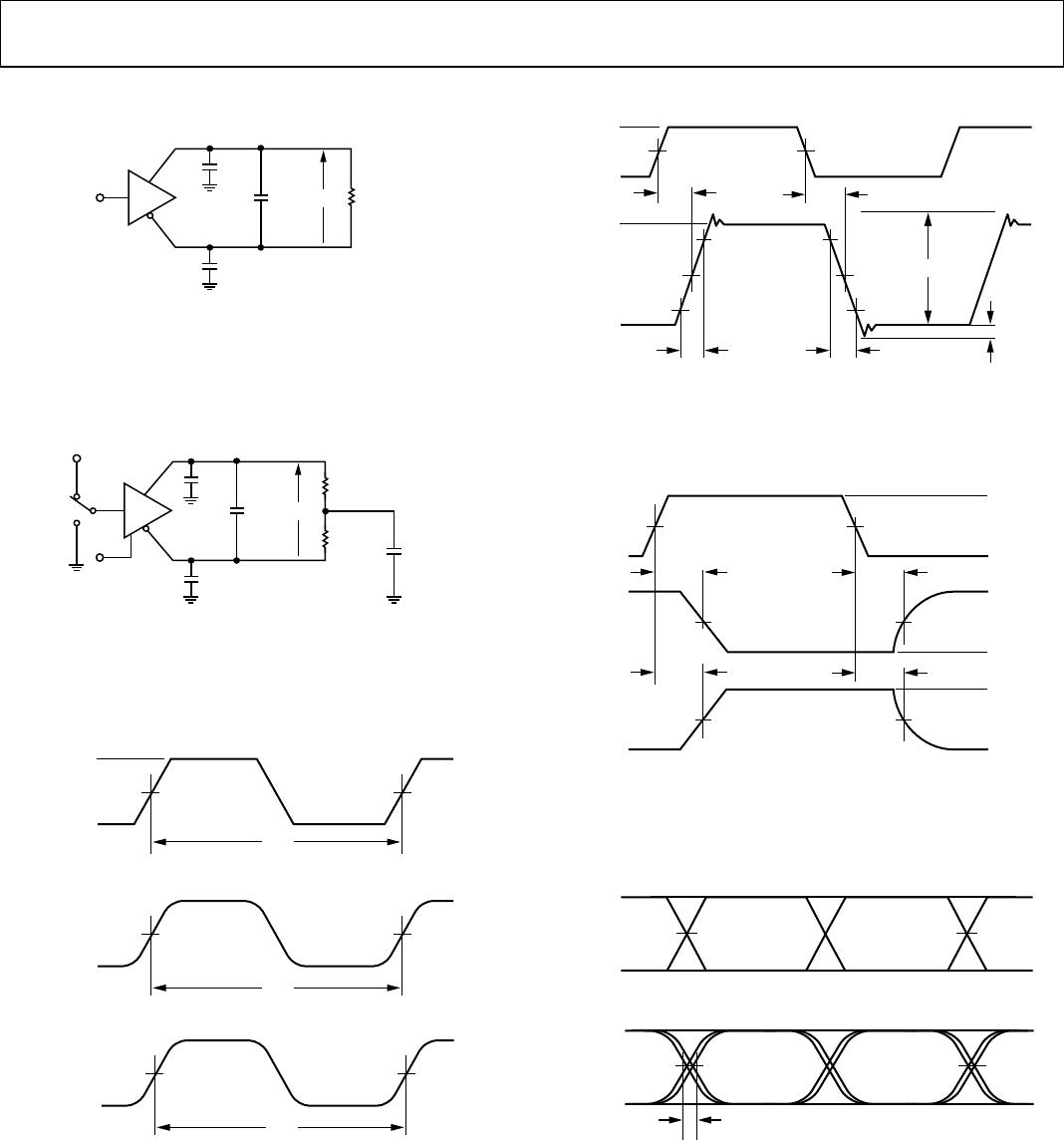

Figure 25. Driver Period Jitter Characteristics

NOTES

1. INPUT PULSE GENERATOR: 1MHz; 50% ± 5% DUTY CYCLE;

t

R

,

t

F

≤ 1ns.

2. MEASURED ON TEST EQUIPMENT WITH –3dB BANDWIDTH ≥ 1GHz.

t

PLH

t

R

t

F

t

PHL

V

CC

V

SS

V

PH

V

PL

0% V

SS

10% V

SS

90% V

SS

0V

0V 0V

OUT

DI

10471-025

10% V

SS

90% V

SS

V

CC

/2 V

CC

/2

Figure 26. Driver Propagation, Rise/Fall Times and Voltage Overshoot

0.5V

CC

0.5V

CC

V

CC

0V

0V

0V

~ –0.6V

~ +0.6V

–0.1V

0.1V

0.1V

DE

OUT

(DI = 0V)

OUT

(DI = V

CC

)

10471-026

t

PZH

t

PZ

L

–0.1V

t

PHZ

t

PLZ

NOTES

1. INPUT PULSE GENER

AT

OR: 1MHz; 50% ± 5% DUTY CYCLE;

t

R

,

t

F

≤ 1ns.

2. MEASURED ON TEST EQUIPMENT WITH –3dB BANDWIDTH ≥ 1GHz.

Figure 27. Driver Enable/Disable Times

NOTES

1. INPUT PULSE GENERATOR: AGILENT 8304A STIMULUS SYSTEM;

100Mbps; 2

15

– 1PRBS.

2. MEASURED USING TEK TDS6604 WITH TDSJIT3 SOFTWARE.

V

A

– V

B

OR

V

Y

– V

Z

V

A

– V

B

OR

V

Y

– V

Z

V

CC

OUTPUT

INPUT

(PRBS)

0V

V

CC

/2

t

J(PP)

0V 0V

V

CC

/2

10471-027

Figure 28. Driver Peak-to-Peak Jitter Characteristics