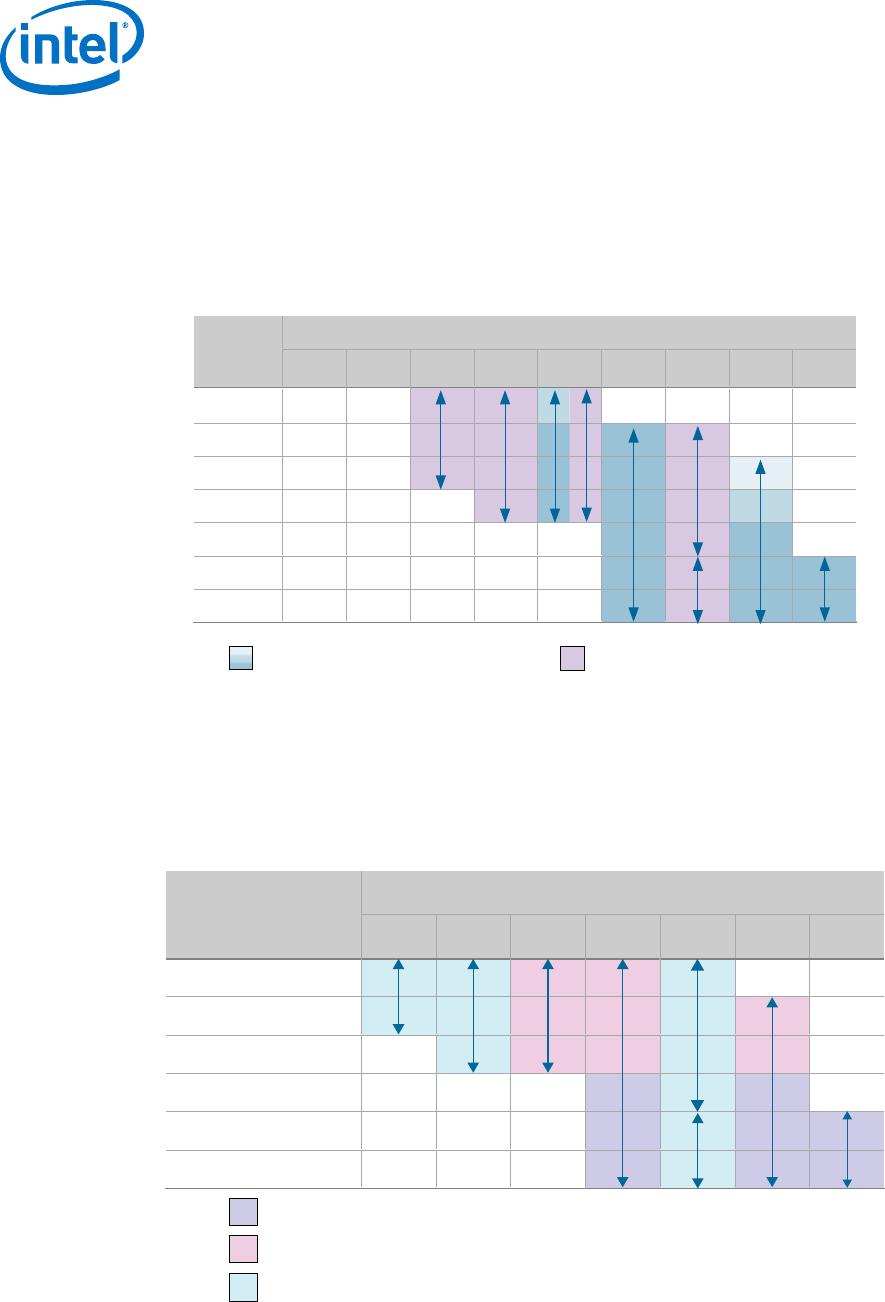

Table 7. Pin Migration Conditions for ADC Migration

Source Target Migratable Pins

Single ADC device Single ADC device You can migrate all ADC input pins

Dual ADC device Dual ADC device

Single ADC device Dual ADC device • One dedicated analog input pin.

• Eight dual function pins from the ADC1 block of the

source device to the ADC1 block of the target device.

Dual ADC device Single ADC device

Logic Elements and Logic Array Blocks

The LAB consists of 16 logic elements (LE) and a LAB-wide control block. An LE is the

smallest unit of logic in the Intel MAX 10 device architecture. Each LE has four inputs,

a four-input look-up table (LUT), a register, and output logic. The four-input LUT is a

function generator that can implement any function with four variables.

Figure 4. Intel MAX 10 Device Family LEs

Row, column, and

direct link routing

data 1

data 2

data 3

data 4

labclr1

labclr2

Chip-wide reset

(DEV_CLRn)

labclk1

labclk2

labclkena1

labclkena2

LE carry-in

LAB-wide

synchronous load

LAB-Wide

synchronous clear

Row, column, and

direct link routing

Local routing

Register chain output

Register bypass

Programmable register

Register chain routing

from previous LE

LE Carry-Out

Register feedback

Synchronous

Load and

Clear Logic

Carry

Chain

Look-Up Table

(LUT)

Asynchronous

Clear Logic

Clock and

Clock Enable

Select

D

Q

ENA

CLRN

Analog-to-Digital Converter

Intel MAX 10 devices feature up to two ADCs. You can use the ADCs to monitor many

different signals, including on-chip temperature.

Table 8. ADC Features

Feature Description

12-bit resolution • Translates analog signal to digital data for information processing, computing,

data transmission, and control systems

• Provides a 12-bit digital representation of the observed analog signal

Up to 1 MSPS sampling rate Monitors single-ended external inputs with a cumulative sampling rate of 25

kilosamples per second to 1 MSPS in normal mode

continued...

Intel

®

MAX

®

10 FPGA Device Overview

M10-OVERVIEW | 2017.12.15

Intel

®

MAX

®

10 FPGA Device Overview

9