5

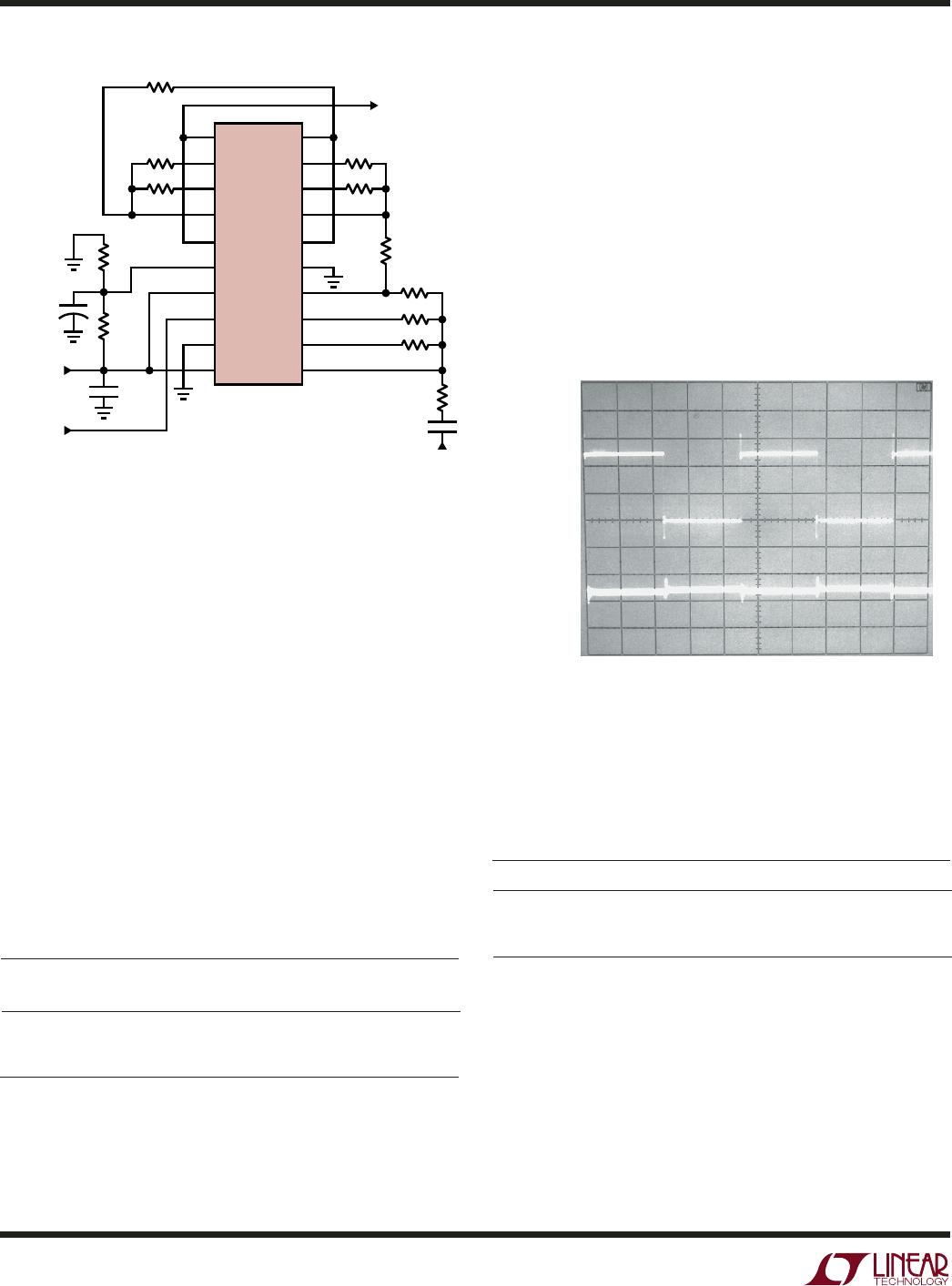

LTC1061

1061fe

DESCRIPTIO A D

U

PI

U

APPLICATIO

U

HI TS

UU

–

+

Σ

+

∫

Σ

LEVEL

SHIFT

LEVEL

SHIFT

LEVEL

SHIFT

CLOCK

GENERATOR

CLOCK

GENERATOR

CLOCK

GENERATOR

CLK

(8)

LEVEL SHIFT

(9)

TO FILTER A

TO FILTER B

TO FILTER C

+

∫

+

∫

+

∫

+

∫

+

∫

50/100/

HOLD

(7)

AGND

(6)

V

+

(10)

V

–

(15)

HP

C

(12)

S1

B

(16)

BP

C

(13)

LP

C

(14)

S1

A

(5)

NB

(18)

BP

B

(19)

LP

B

(20)

NA

(3)

BP

A

(2)

LP

A

(1)

INV

A

(4)

INV

B

(17)

INV

C

(11)

1061 BD

+

–

+

–

–

+

–

+

frequencies below 500kHz the clock “on” time can be as

low as 300ns. The maximum clock frequency for ±5V

supplies and above is 2.4MHz.

S1

A

, S1

B

(Pins 5, 16)

These are voltage input pins. If used, they should be driven

with a source impedance below 5kΩ. when they are not

used, they should be tied to the analog ground Pin 6.

AGND (Pin 6)

When the LTC1061 operates with dual supplies, Pin 6

should be tied to system ground. When the LTC1061

operates with a single positive supply, the analog ground

pin should be tied to 1/2 supply, Figure 1. The positive

input of all the internal op amps, as well as the common

reference of all the internal switches, are internally tied to

the analog ground pin. Because of this, a “clean” ground

is recommended.

Power Supplies (Pins 10, 15)

They should be bypassed with 0.1µF disc ceramic. Low

noise, nonswitching, power supplies are recommended.

The device operates with a single 5V supply, Figure 1, and

with dual supplies. The absolute maximum operating

power supply voltage is ±9V.

Clock and Level shift (Pins 8, 9)

When the LTC1061 operates with symmetrical dual sup-

plies the level shift Pin 9 should be tied to analog ground.

For single 5V supply operation, the level shift pin should be

tied to Pin 15 which will be the system ground. The typical

logic threshold levels of the clock pin are as follows: 1.65V

above the level shift pin for ±5V supply operation, 1.75V

for ±7.5V and above, and 1.4V for single 5V supply

operation. The logic threshold levels vary ±100mV over

the full military temperature range. The recommended

duty cycle of the input clock is 50% although for clock

BLOCK DIAGRA

W