12

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO

TM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

MARCH 2013

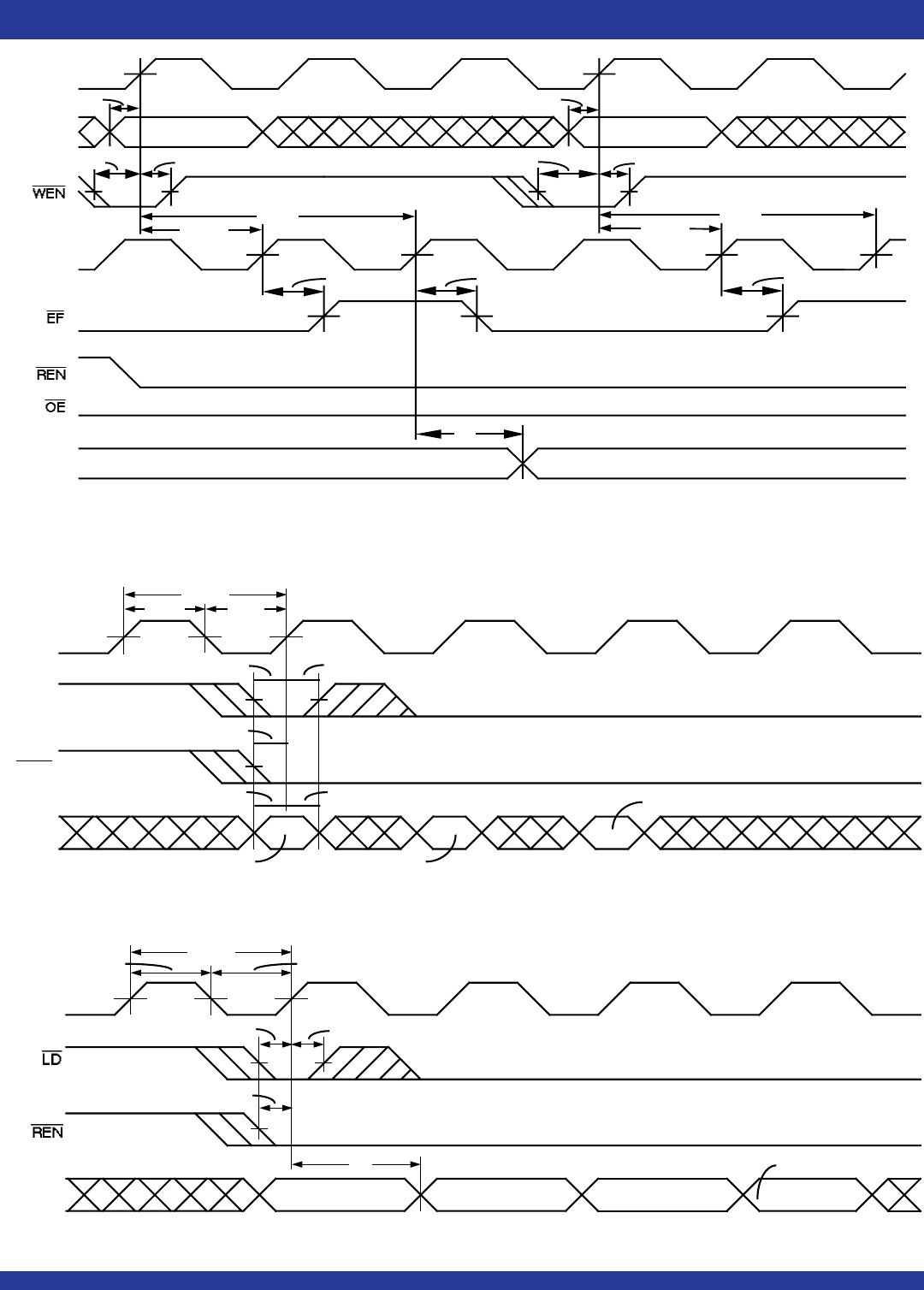

Figure 12. Programmable Almost-Empty Flag Timing

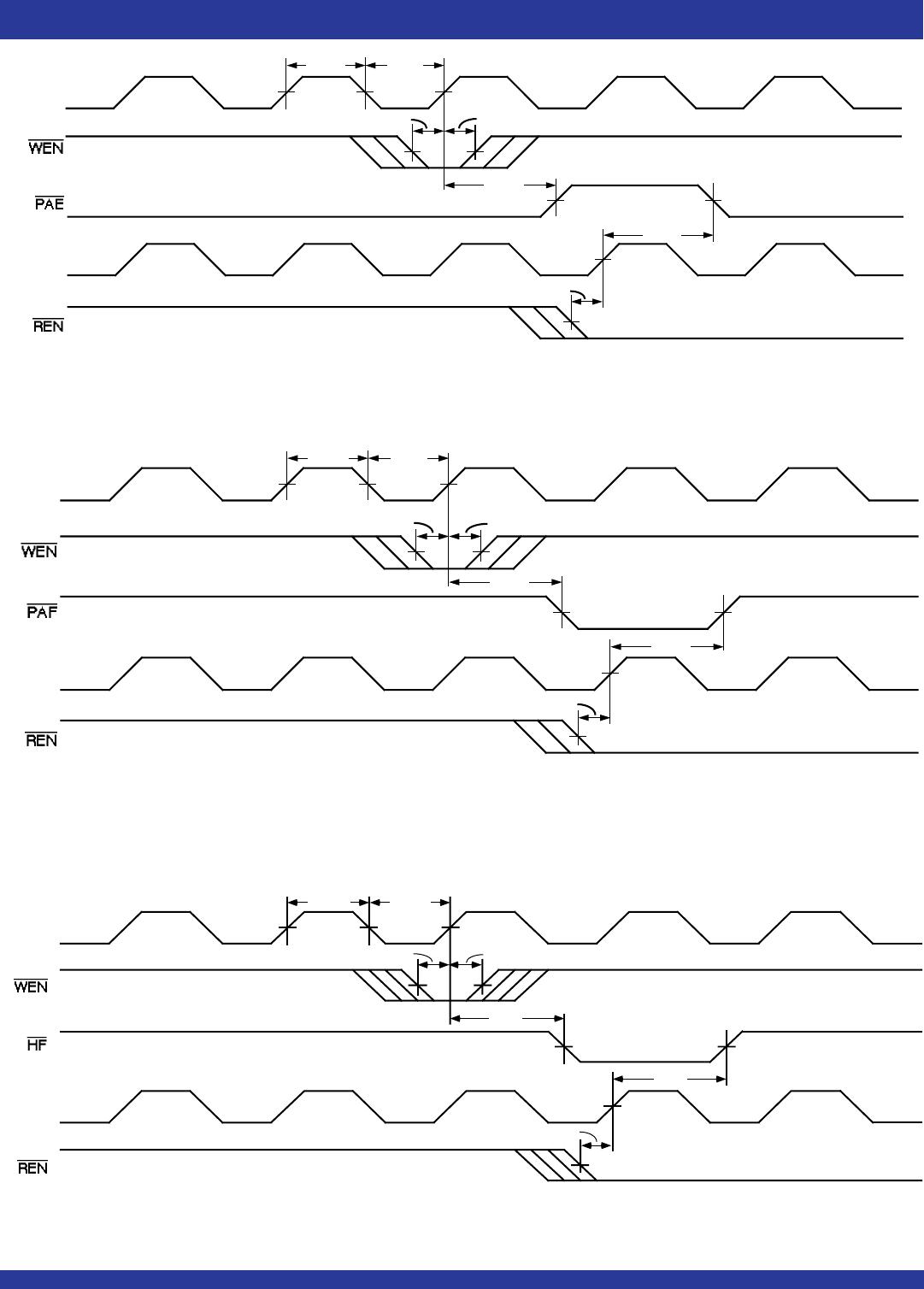

Figure 13. Programmable Almost-Full Flag Timing

WCLK

tCLKH tCLKL

tENS tENH

tENS

tPAE

n + 1 words in FIFO

n words in FIFO

RCLK

tPAE

2766 drw 14

WCLK

tCLKH

tCLKL

tENS

tENH

tENS

tPAF

D – m + 1 words

in FIFO memory

RCLK

tPAF

(1)

2766 drw 15

D – m words

in FIFO memory

(2)

(1)

D – m + 1 words in FIFO memory

(1)

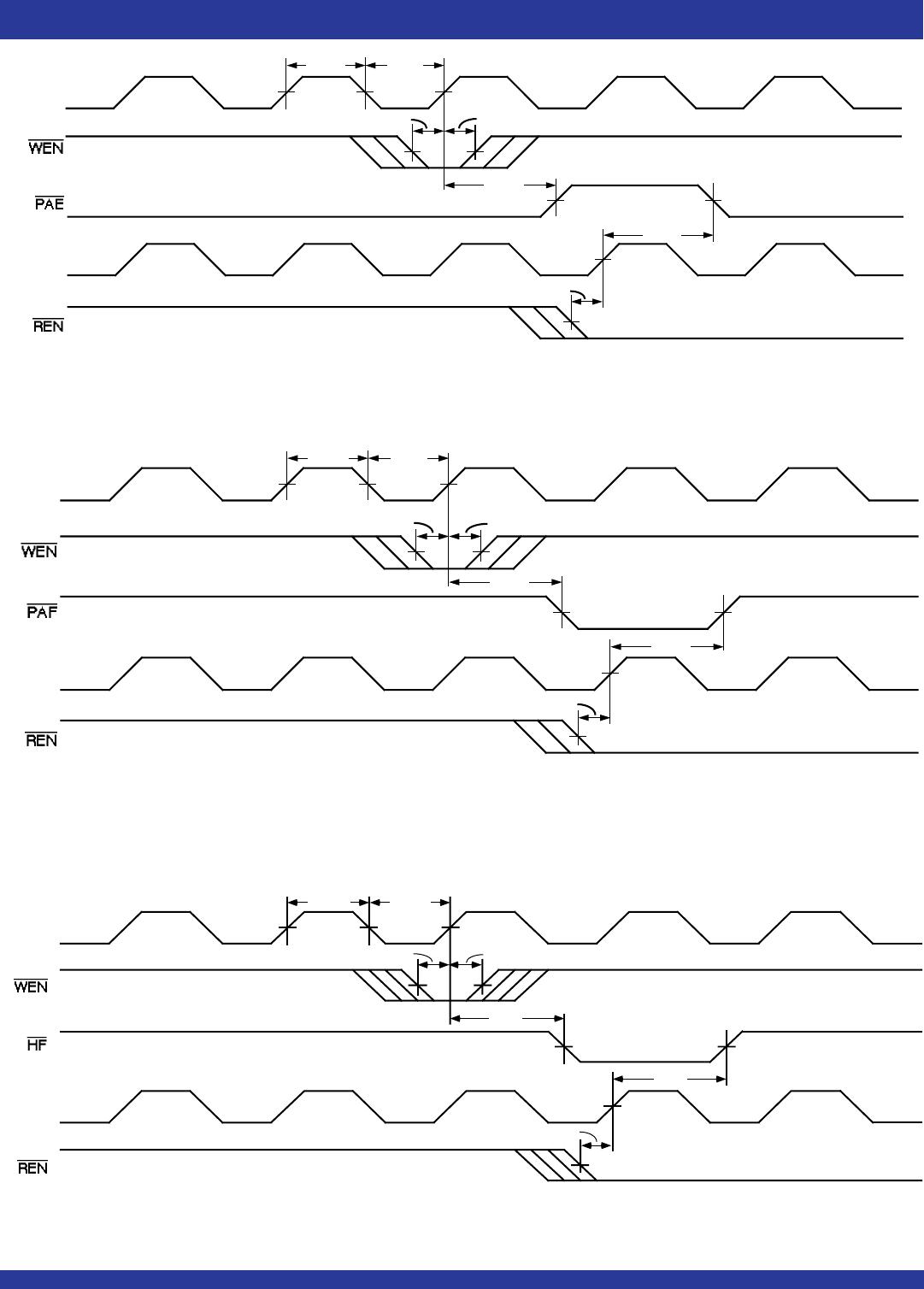

Figure 14. Half-Full Flag Timing

WCLK

t

ENS

t

ENH

t

ENS

t

HF

RCLK

t

HF

D/2 words in

FIFO memory

(1)

2766 drw 16

D/2 + 1 words in

FIFO memory

(2)

D/2 words in FIFO memory

(1)

t

CLKL

t

CLKH

NOTES:

1. D = maximum FIFO Depth =

256 words for the IDT72205LB, 512 words for the IDT72215LB, 1,024 words for the IDT72225LB, 2,048 words for the IDT72235LB and 4,096 words

for the IDT72245LB.

NOTE:

1. n = PAE offset. Number of data words written into FIFO already = n.

NOTES:

1. m = PAF offset. D = maximum FIFO Depth. Number of data words written into FIFO memory

= 256 - m + 1 for the IDT72205LB, 512 - m + 1 for the IDT72215LB,

1,024 - m + 1 for the IDT72225LB, 2,048 - (m + 1) for the IDT72235LB and 4,096 - (m + 1) for the IDT72245LB.

2.

256 - m words for the IDT72205LB, 512 - m words for the IDT72215LB, 1,024 - m words for the IDT72225LB, 2,048 - m words for the IDT72235LB and 4,096 - m words for

the IDT72245LB.