IDT

®

Six Output Differential Buffer for PCIe Gen3 1668F—10/20/16

9DB633

Six Output Differential Buffer for PCIe Gen3

9

Datasheet

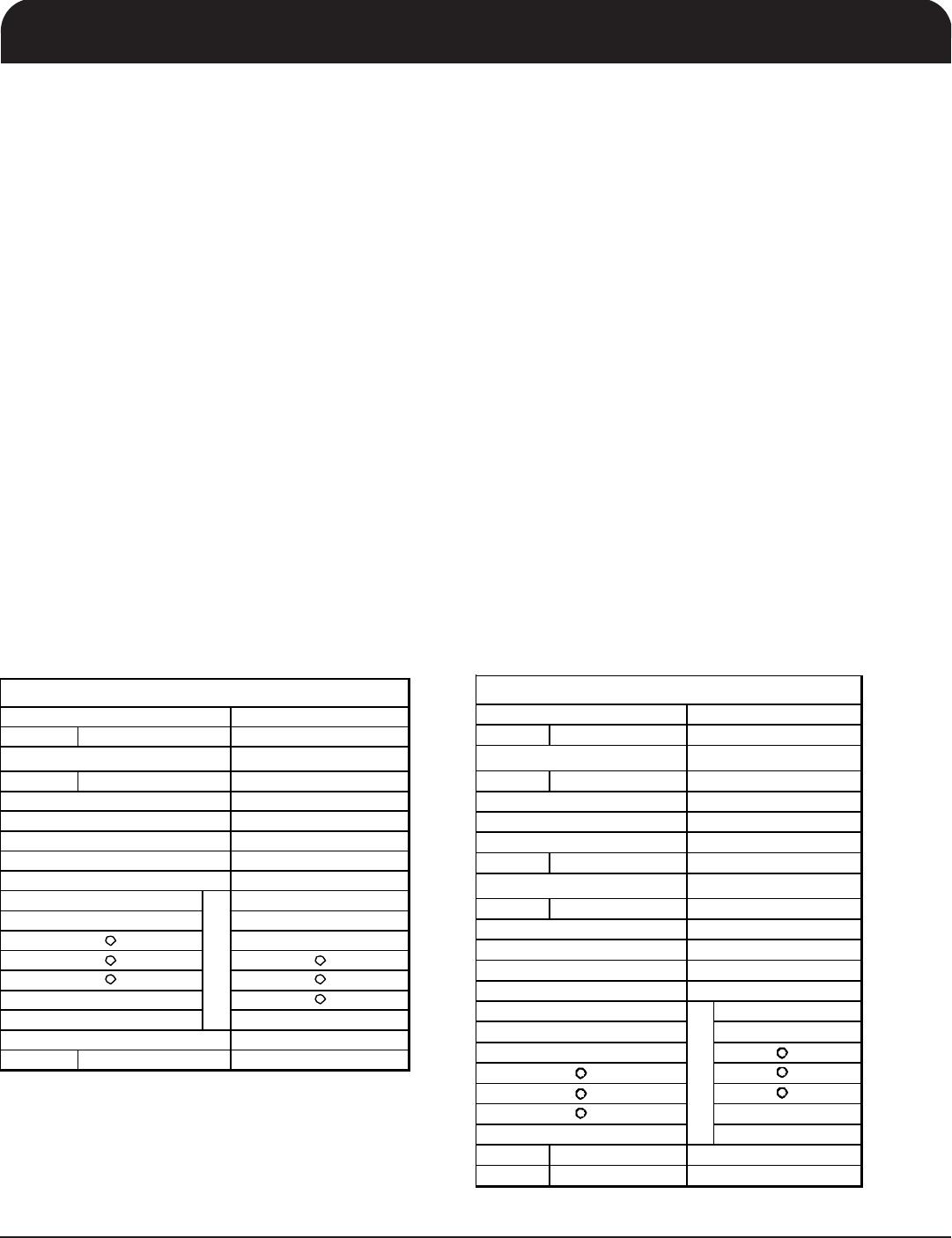

General SMBus serial interface information for the 9DB633

How to Write:

• Controller (host) sends a start bit.

• Controller (host) sends the write address D4

(H)

• ICS clock will

acknowledge

• Controller (host) sends the begining byte location = N

• ICS clock will

acknowledge

• Controller (host) sends the data byte count = X

• ICS clock will

acknowledge

• Controller (host) starts sending

Byte N through

Byte N + X -1

(see Note 2)

• ICS clock will

acknowledge

each byte

one at a time

• Controller (host) sends a Stop bit

How to Read:

• Controller (host) will send start bit.

• Controller (host) sends the write address D4

(H)

• ICS clock will

acknowledge

• Controller (host) sends the begining byte

location = N

• ICS clock will

acknowledge

• Controller (host) will send a separate start bit.

• Controller (host) sends the read address D5

(H)

• ICS clock will

acknowledge

• ICS clock will send the data byte count = X

• ICS clock sends

Byte N + X -1

• ICS clock sends

Byte 0 through byte X (if X

(H)

was written to byte 8)

.

• Controller (host) will need to acknowledge each byte

• Controllor (host) will send a not acknowledge bit

• Controller (host) will send a stop bit

ICS (Slave/Receiver)

T

WR

ACK

ACK

ACK

ACK

ACK

P

Byte N + X - 1

Data Byte Count = X

Beginning Byte N

stoP bit

X Byte

Index Block Write Operation

Slave Address D4

(H)

Beginning Byte = N

WRite

starT bit

Controller (Host)

TstarT bit

WR WRite

RT Repeat starT

RD ReaD

Beginning Byte N

Byte N + X - 1

N Not acknowledge

PstoP bit

Slave Address D5

(H)

Index Block Read Operation

Slave Address D4

(H)

Beginning Byte = N

ACK

ACK

Data Byte Count = X

ACK

ICS (Slave/Receiver)

Controller (Host)

X Byte

ACK

ACK