TCP−5056UB

www.onsemi.com

5

ASSEMBLY CONSIDERATIONS AND REFLOW PROFILE

The following assembly considerations should be observed:

Cleanliness

These chips should be handled in a clean environment.

Electro−static Sensitivity

ON Semiconductor’s PTICs are ESD Class 1B sensitive.

The proper ESD handling procedures should be used.

Mounting

The WLCSP PTIC is fabricated for Flip Chip solder

mounting. Connectivity to the RF and Bias terminations on

the PTIC die is established through SAC305 solder balls

with 90 mm nominal height (65 mm to 115 mm height

variation). The PTIC die is RoHS−compliant and

compatible with lead−free soldering profile.

Molding

The PTIC die is compatible for over−molding or

under−fill.

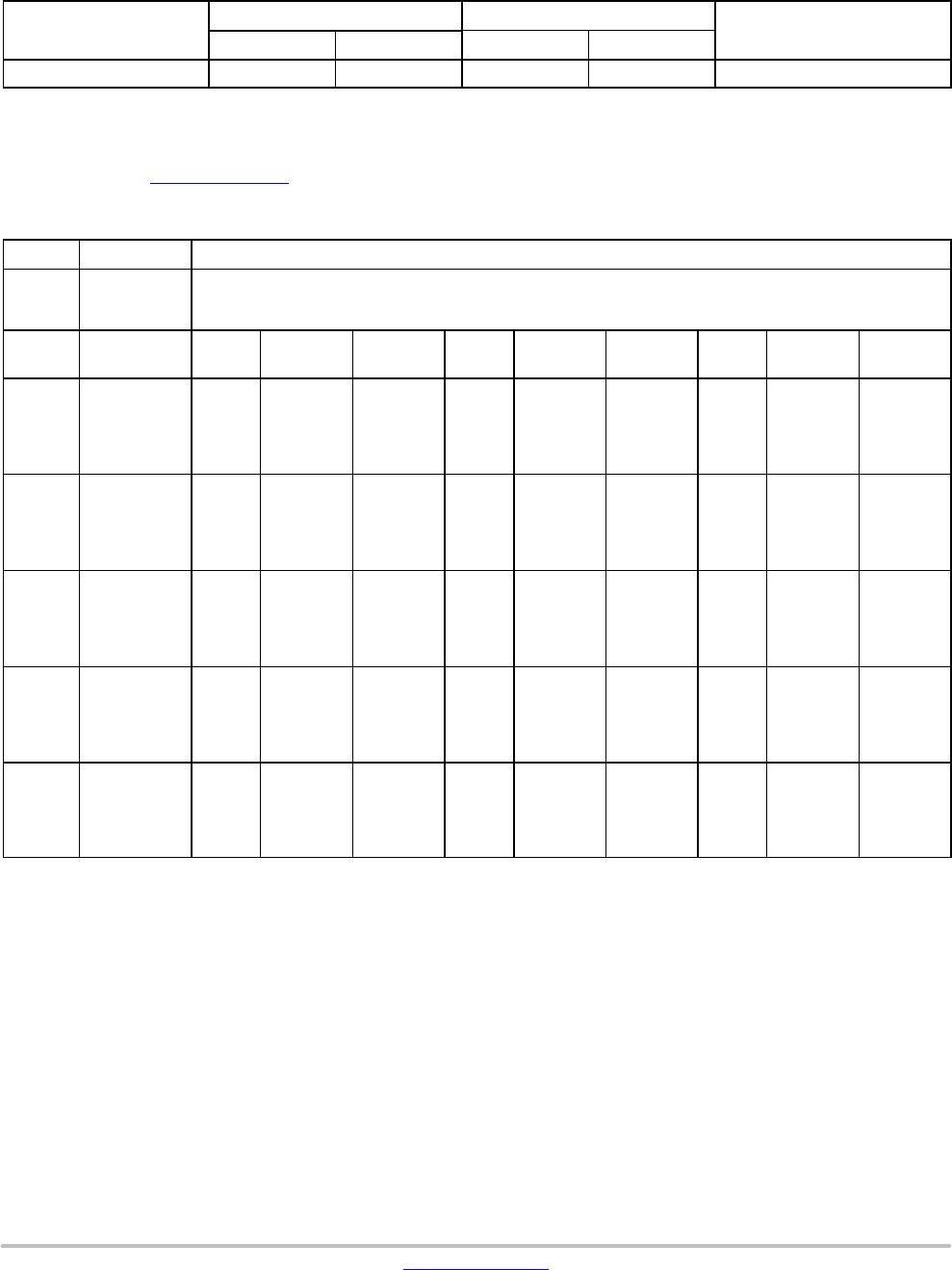

Figure 6. Reflow Profile

ORIENTATION OF THE PTIC FOR OPTIMUM LOSSES

When configuring the PTIC in your specific circuit

design, at least one of the RF terminals must be connected

to DC ground. If minimum transition times are required, DC

ground on both RF terminals is recommended. To minimize

losses, the PTIC should be oriented such that RF2

is at the

lower RF impedance of the two RF nodes. A shunt PTIC, for

example, should have RF2

connected to RF ground.

Figure 7. PTIC Orientation Functional Block

Diagram

Bias

RF ANT

RF1

(PTIC Pad)

RF2

(PTIC Pad)