REV. 0

ADM2209E

–10–

The ADM2209E is tested using both of the above-mentioned

test methods. All pins are tested with respect to all other pins as

per the MIL-STD-883B specification. In addition, all I-O pins

are tested as per the IEC test specification. The products were

tested under the following conditions:

(a) Power-On—Normal Operation

(b) Power-Off

There are four levels of compliance defined by IEC1000-4-2.

The ADM2209E meets the most stringent compliance level for

both contact and air-gap discharge. This means that the products

are able to withstand contact discharges in excess of 8 kV and air-

gap discharges in excess of 15 kV.

Table IV. IEC1000-4-2 Compliance Levels

Contact Discharge Air Discharge

Level kV kV

12 2

24 4

36 8

48 15

Table V. ADM2209E ESD Test Results

ESD Test Method I-O Pins Other Pins

MIL-STD-883B ±15 kV ±2.5 kV

IEC1000-4-2

Contact ±8 kV

Air ±15 kV

FAST TRANSIENT BURST TESTING (IEC1000-4-4)

IEC1000-4-4 (previously 801-4) covers electrical fast-transient/

burst (EFT) immunity. Electrical fast transients occur as a

result of arcing contacts in switches and relays. The tests simu-

late the interference generated when, for example, a power relay

disconnects an inductive load. A spark is generated due to the

well-known back EMF effect. In fact the spark consists of a burst

of sparks as the relay contacts separate. The voltage appearing

on the line, therefore, consists of a burst of extremely fast tran-

sient impulses. A similar effect occurs when switching on fluo-

rescent lights.

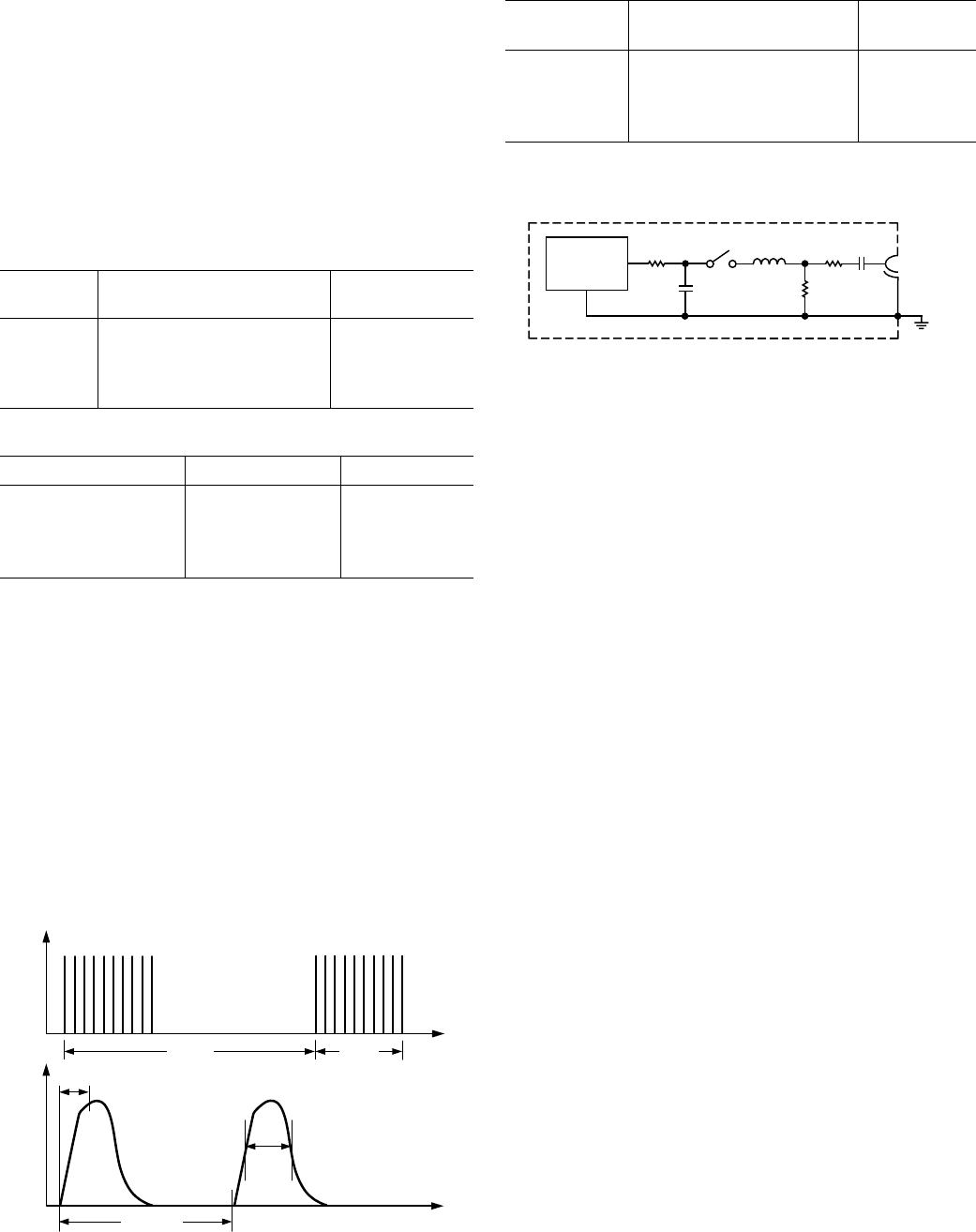

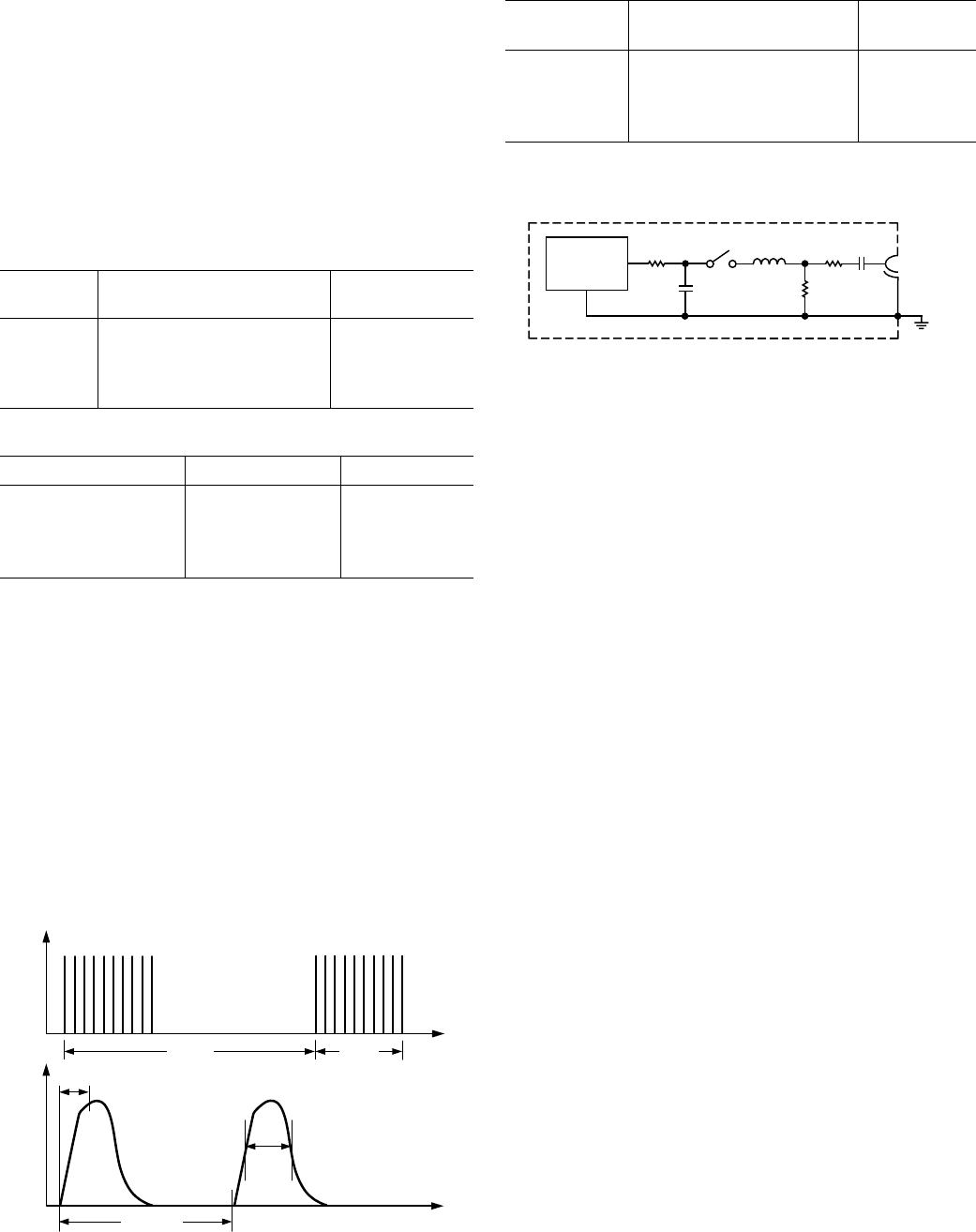

The fast transient burst test defined in IEC1000-4-4 simulates

this arcing and its waveform is illustrated in Figure 26. It con-

sists of a burst of 2.5 kHz to 5 kHz transients repeating at

300 ms intervals. It is specified for both power and data lines.

300ms 15ms

t

V

5ns

0.2/0.4ms

50ns

V

t

Figure 26. IEC1000-4-4 Fast Transient Waveform

Table VI.

V Peak (kV) V Peak (kV)

Level PSU I-O

1 0.5 0.25

2 1 0.5

321

442

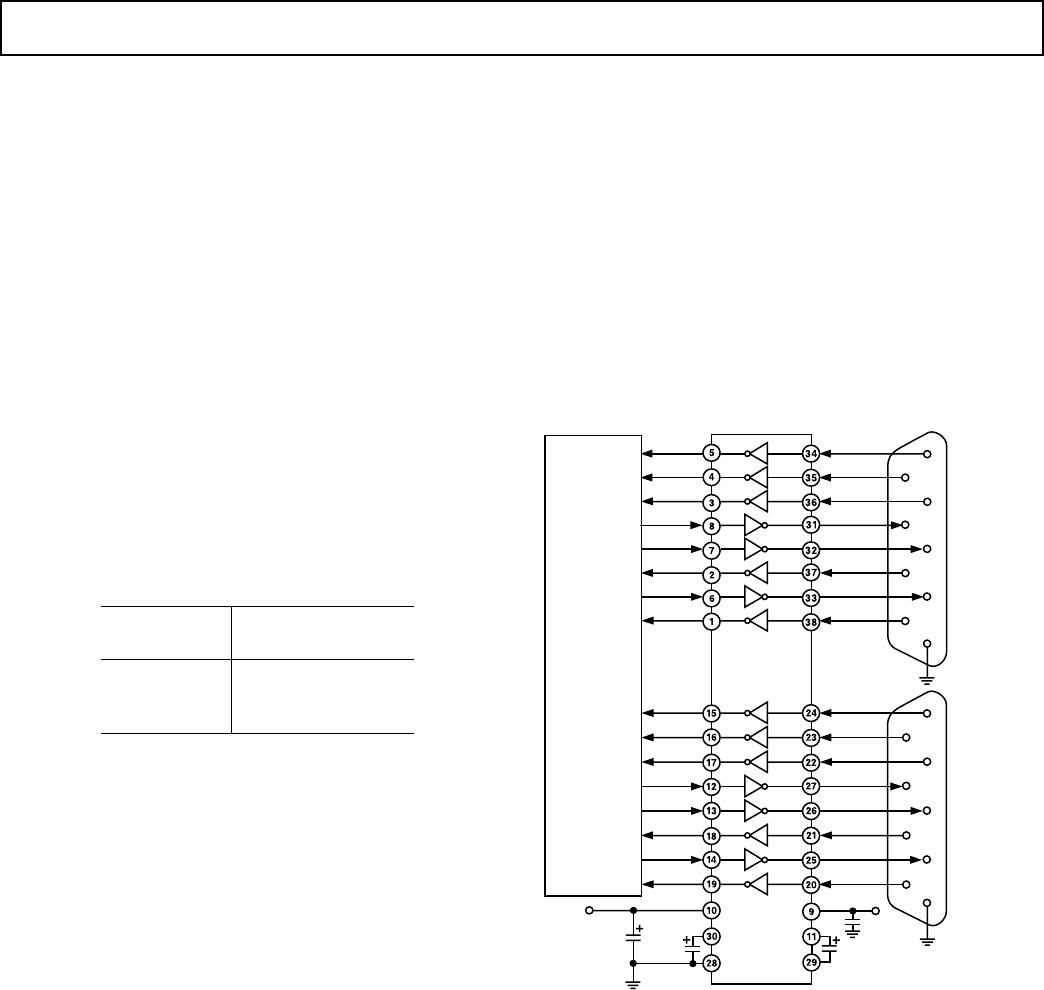

A simplified circuit diagram of the actual EFT generator is

illustrated in Figure 27.

R

C

R

M

C

C

HIGH

VOLTAGE

SOURCE

L

Z

S

C

D

50V

OUTPUT

Figure 27. IEC1000-4-4 Fast Transient Generator

The transients are coupled onto the signal lines using an EFT

coupling clamp. The clamp is 1 meter long and it completely

surrounds the cable, providing maximum coupling capacitance

(50 pF to 200 pF typ) between the clamp and the cable. High

energy transients are capacitively coupled onto the signal lines.

Fast rise times (5 ns) as specified by the standard result in very

effective coupling. This test is very severe since high voltages

are coupled onto the signal lines. The repetitive transients can

often cause problems where single pulses do not. Destructive

latch-up may be induced due to the high energy content of the

transients. Note that this stress is applied while the interface

products are powered up and transmitting data. The EFT test

applies hundreds of pulses with higher energy than ESD. Worst

case transient current on an I-O line can be as high as 40 A.

Test results are classified according to the following:

1. Normal performance within specification limits.

2. Temporary degradation or loss of performance which is self-

recoverable.

3. Temporary degradation or loss of function or performance

which requires operator intervention or system reset.

4. Degradation or loss of function which is not recoverable due

to damage.

The ADM2209E has been tested under worst case conditions

using unshielded cables and meets Classification 2. Data trans-

mission during the transient condition is corrupted, but it may

be resumed immediately following the EFT event without user

intervention.

IEC1000-4-3 RADIATED IMMUNITY

IEC1000-4-3 (previously IEC801-3) describes the measure-

ment method and defines the levels of immunity to radiated

electromagnetic fields. It was originally intended to simulate the

electromagnetic fields generated by portable radio transceivers

or any other device that generates continuous wave radiated

electromagnetic energy. Its scope has since been broadened to

include spurious EM energy which can be radiated from fluores-

cent lights, thyristor drives, inductive loads, etc.