Freescale, the Freescale logo and QorIQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm Off. CoreNet is a

trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and

service marks licensed by Power.org. © 2012 Freescale Semiconductor,Inc.

Document Number: P50405021FS REV 1

For more information, please visit freescale.com/QorIQ

P5040/P5021 Features List

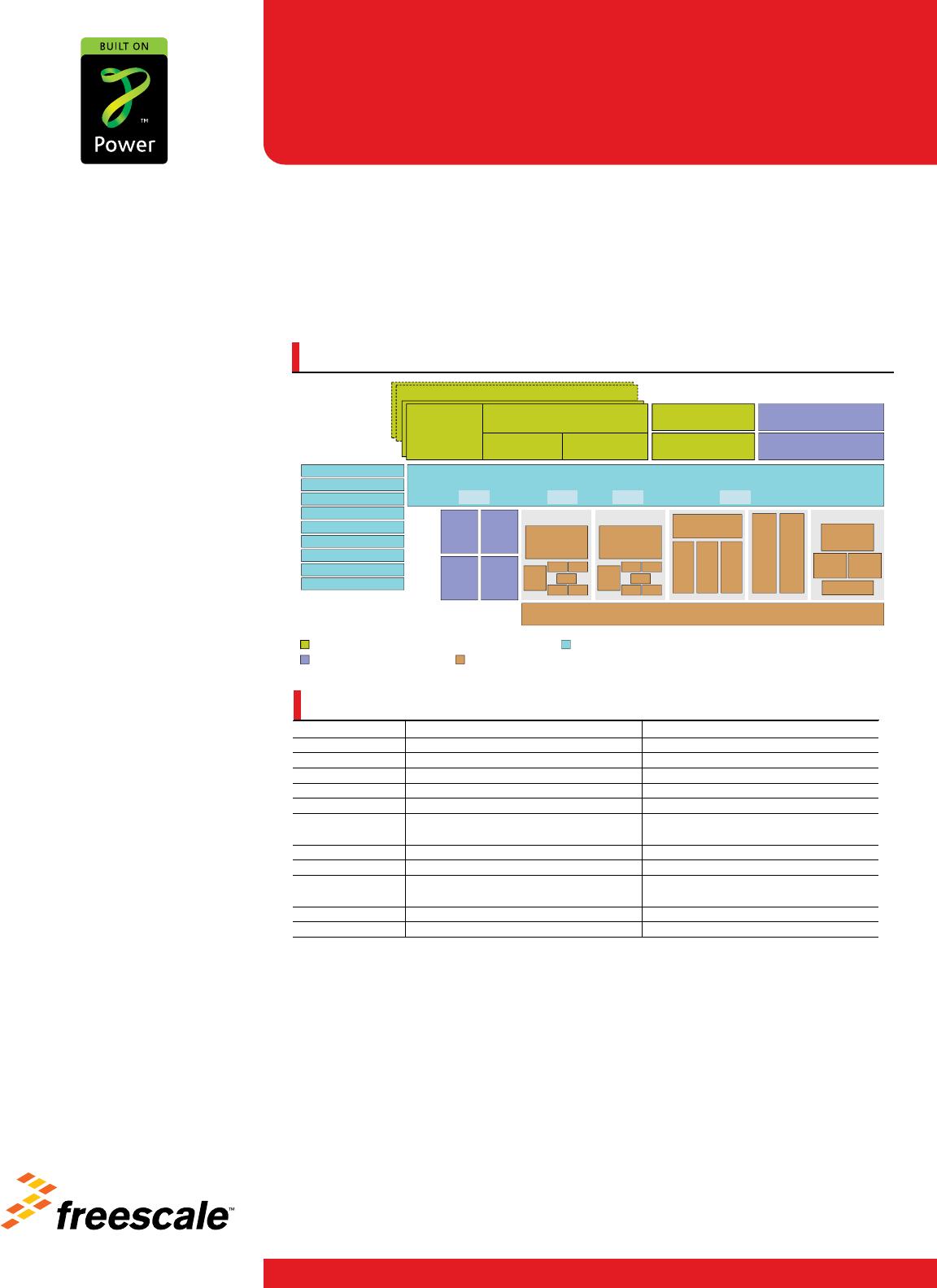

Four(P5040)ortwo(P5021)

single threaded e5500 cores

built on Power Architecture

®

technology

• Upto2.4GHzwith64-bitISAsupport(PowerArchitectureV2.06compliant)

• Threelevelsofinstruction:User,supervisor,hypervisor

• Hybrid32-bitmodetosupportlegacysoftwareandtransitionto64-bit

architecture

CoreNetplatformcache(CPC) • 2.0MBconfiguredasdual1MBblocks

Hierarchicalinterconnectfabric • CoreNetfabricsupportingcoherentandnon-coherenttransactionswith

prioritizationandbandwidthallocationamongstCoreNetendpoints

• QMANfabricsupportingpacket-levelqueuemanagementandqualityof

service scheduling

Two64-bitDDR3/3LSDRAM

memorycontrollerswithECC

and interleaving support

• Upto1600MT/s

• Memorypre-fetchengine

DPAAincorporatingacceleration

for the following functions

• Packetparsing,classificationanddistribution(FMAN)

• QMANforscheduling,packetsequencingandcongestionmanagement

• HardwareBMANforbufferallocationandde-allocation

• Cryptographyacceleration(SEC5.0)atupto40Gb/s

SerDes • 20lanesatupto5Gb/s

• SupportsSGMII,XAUI,PCIerev1.1/2.0,SATA

Ethernet interfaces • Two10Gb/sEthernetMACs

• 10x1Gb/sEthernetMACs

High-speedperipheralinterfaces • ThreePCIExpress2.0controllers

• TwoserialATA(SATA2.0)controllers

Additional peripheral interfaces • TwoHigh-SpeedUSB2.0controllerswithintegratedPHY

• Enhancedsecuredigitalhostcontroller(SD/MMC/eMMC)

• Enhancedserialperipheralinterface

• FourI

2

Ccontrollers

• FourUARTs

• IntegratedflashcontrollersupportingNANDandNORflash

DMA • Dualfourchannel

Supportforhardware

virtualizationandpartitioning

enforcement

• Extraprivilegedlevelforhypervisorsupport

QorIQtrustarchitecture1.1 • Secureboot,securedebug,tamperdetection,volatilekeystorage

DPAA Hardware Accelerators

Framemanager(FMAN) 24Gbpsclassify,parse

and distribute

Buffermanager(BMAN) 64 buffer pools

Queuemanager(QMAN) Upto2

24

queues

Security(SEC) 17Gbps:3DES,AES

RAID5/6Engine Calculatesparityfor

network attached

storage and direct

attached storage

applications

Data Path Acceleration Architecture

(DPAA)

TheP5040integratesQorIQDPAA,an

innovative multicore infrastructure for

schedulingworktocores(physicalandvirtual),

hardware accelerators and network interfaces.

TheFMAN,aprimaryelementoftheDPAA,

parses headers from incoming packets and

classifies and selects data buffers with optional

policing and congestion management. The

FMANpassesitsworktotheQMAN,which

assigns it to cores or accelerators with a

multi-level scheduling hierarchy. The P5040

also offers accelerators for cryptography and

RAID5/6offload.

System Peripherals and Networking

Fornetworking,therearedualFMANswithdual

10Gb/sand10x1Gb/sMACcontrollersthat

connecttoPHYs,switchesandbackplanes

overRGMII,SGMIIandXAUI.High-speed

system expansion is supported through three

PCIExpress

®

v2.0controllersthatsupporta

varietyoflanewidths.Otherperipheralsinclude

SATA,SD/MMC,I

2

C,UART,SPI,NOR/NAND

controller,GPIOanddual1600MT/sDDR3/3L

controllers.

Software and Tool Support

• Enea:Real-timeoperatingsystemsupport

andvirtualizationsoftware

• GreenHills:Comprehensiveportfolioof

software and hardware development tools,

trace tools, real-time operating systems

andvirtualizationsoftware

• MentorGraphics

®

:Commercial-grade

Linuxsolution

• QNX

®

:Real-timeOSanddevelopmenttool

support

• QorIQP5040developmentsystem

(P5040QDS-PA)availableJune2012