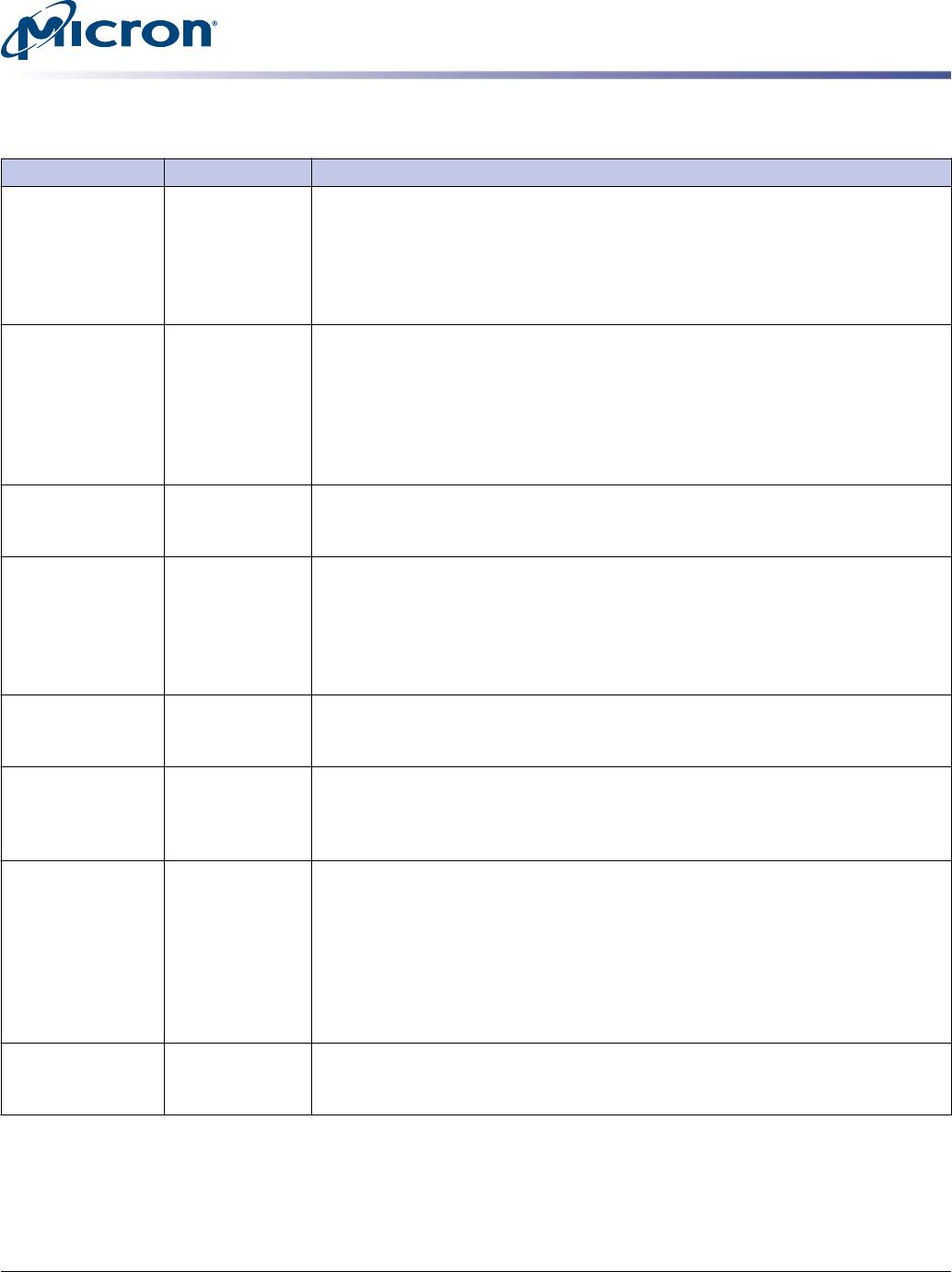

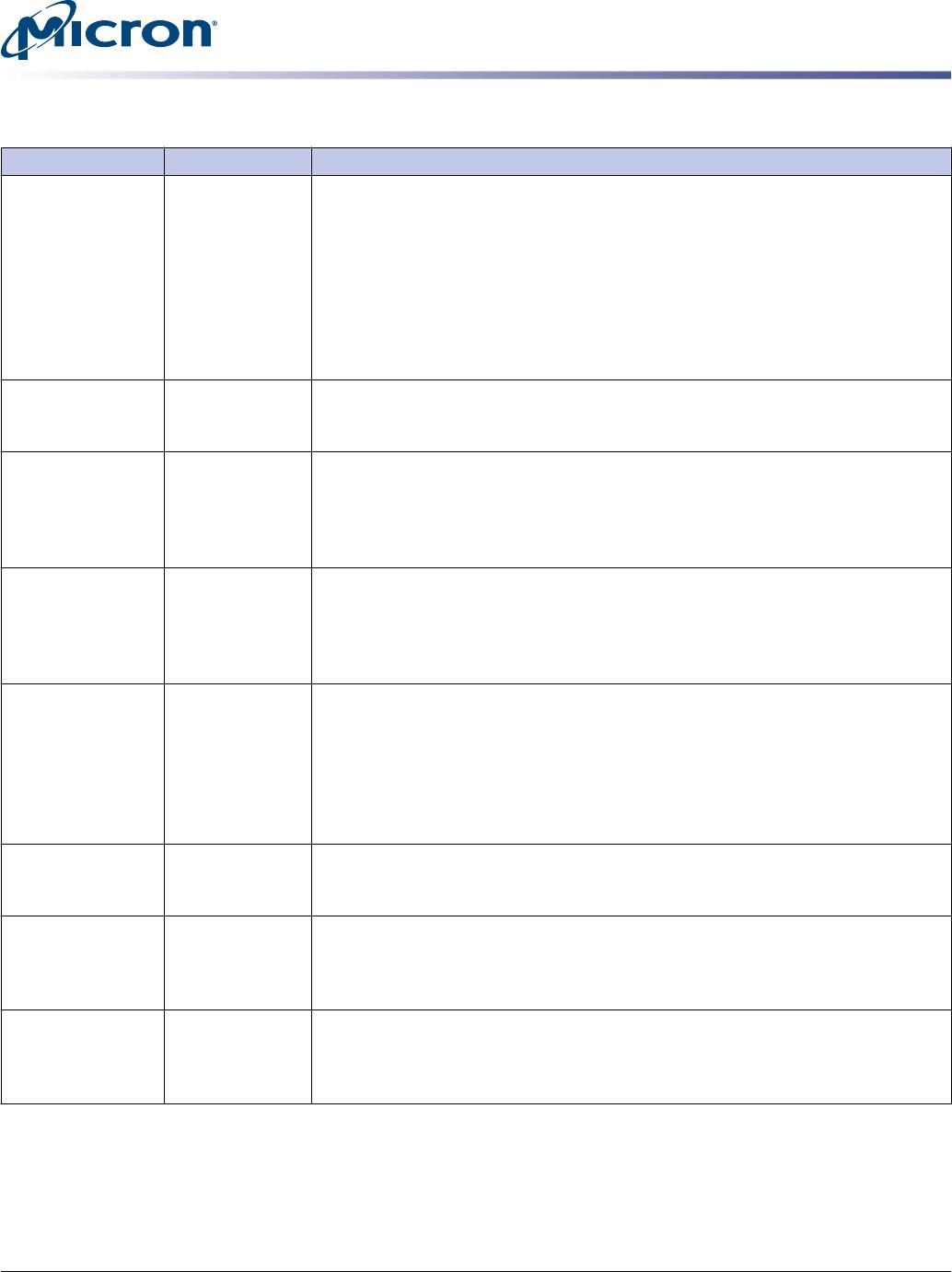

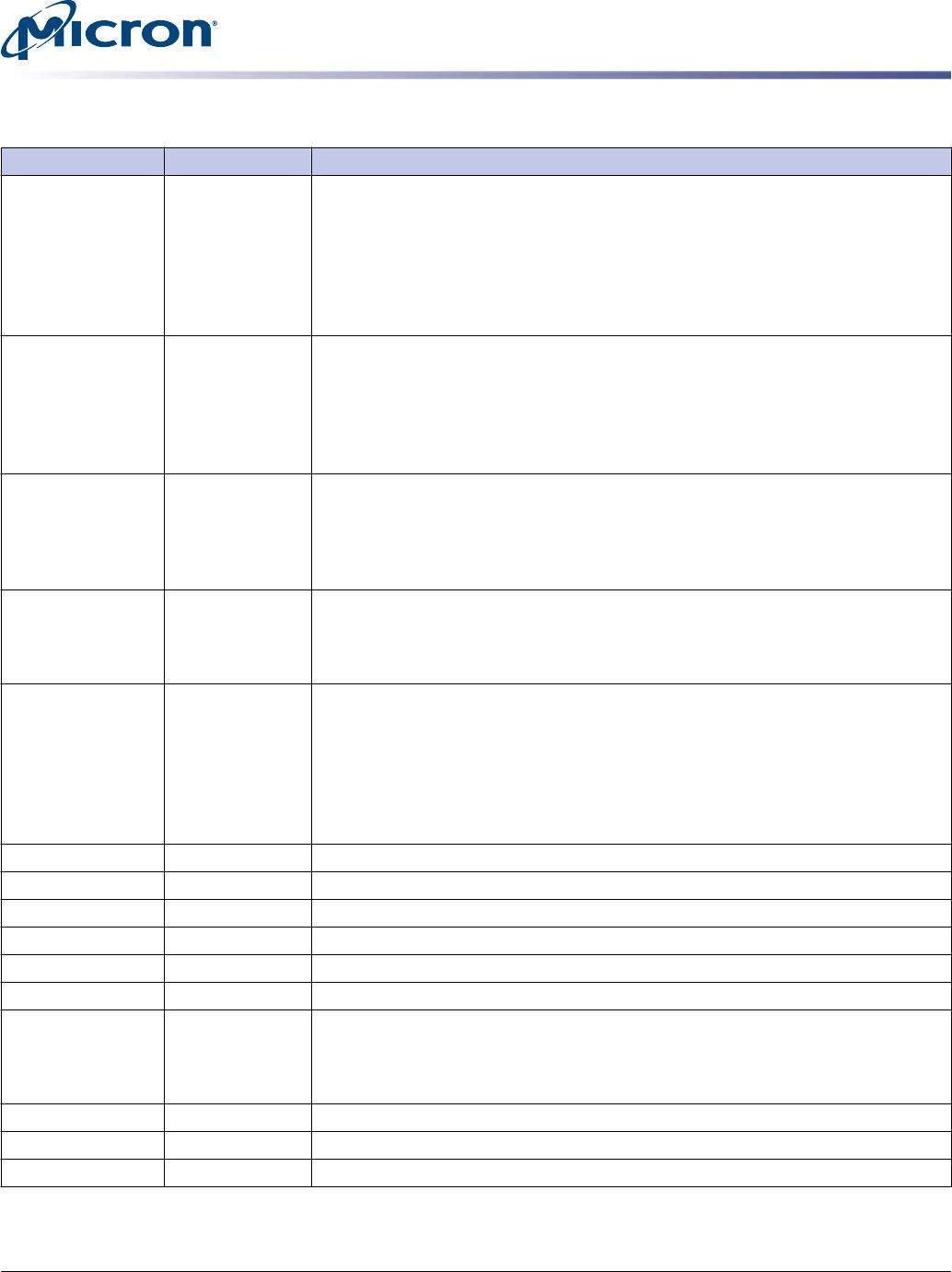

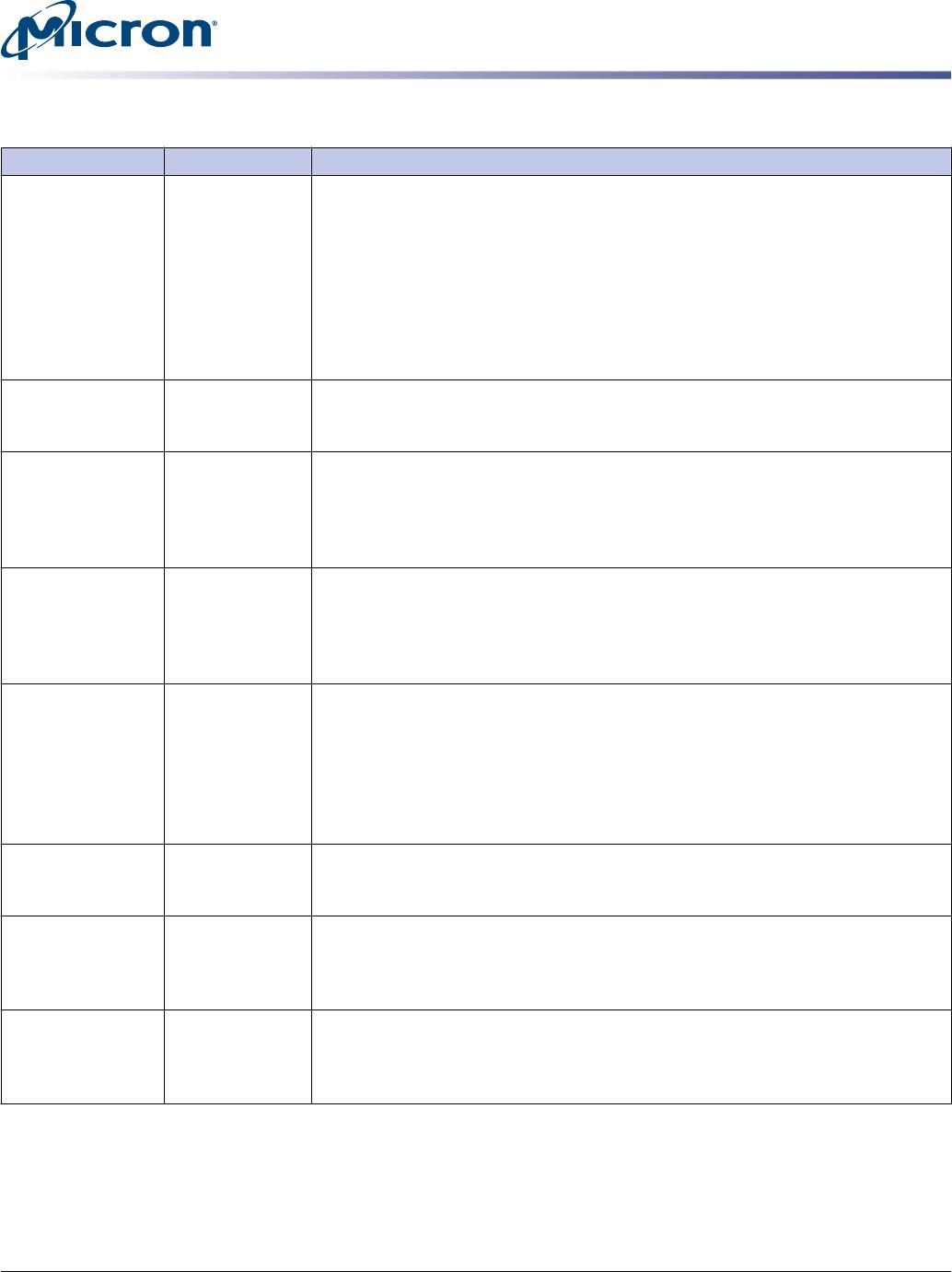

Table 3: FBGA 78-Ball Descriptions (Continued)

Symbol Type Description

CKE Input Clock enable: CKE HIGH activates, and CKE LOW deactivates, the internal clock

signals, device input buffers, and output drivers. Taking CKE LOW provides PRE-

CHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or active

power-down (row active in any bank). CKE is asynchronous for self refresh exit.

After V

REFCA

has become stable during the power-on and initialization sequence,

it must be maintained during all operations (including SELF REFRESH). CKE must

be maintained HIGH throughout read and write accesses. Input buffers (exclud-

ing CK_t, CK_c, ODT, RESET_n, and CKE are disabled during power-down. Input

buffers (excluding CKE and RESET#) are disabled during self refresh.

CS_n Input Chip select: All commands are masked when CS_n is registered HIGH. CS_n pro-

vides for external rank selection on systems with multiple ranks. CS_n is consid-

ered part of the command code.

DM_nS Input Input data mask: DM_n is an input mask signal for write data. Input data is

masked when DM is sampled LOW coincident with that input data during a write

access. DM is sampled on both edges of DQS. DM is not supported on x4 configu-

rations. LDM_n is associated with DQ[7:0]. The DM, DBI, and TDQS functions are

enabled by mode register settings. See the Data Mask (DM) section.

ODT Input On-die termination: ODT (registered HIGH) enables termination resistance in-

ternal to the DDR4 SDRAM. When enabled, ODT (R

TT

) is applied only to each DQ,

DQS_t, DQS_c, DM_n/DBI_n/TDQS_t, and TDQS_c signal for the x4 and x8 configu-

rations (when the TDQS function is enabled via mode register). The ODT pin will

be ignored if the mode registers are programmed to disable R

TT

.

PAR Input Parity for command and address: This function can be enabled or disabled via

the mode register. When enabled, the parity signal covers all command and ad-

dress inputs, including RAS_n/A16, CAS_n/A15, WE_n/A14, A[17:0], A10/AP, A12/

BC_n, BA[1:0], BG[1:0], C0/A18, C1/A19, C2/A20. Control pins NOT covered by the

parity signal are CS_n, CKE, and ODT. Unused address pins that are density- and

configuration-specific should be treated internally as 0s by the DRAM parity log-

ic.

RAS_n/A16,

CAS_n/A15,

WE_n/A14

Input Command inputs: RAS_n/A16 , CAS_n/A15, and WE_n/A14 (along with CS_n and

ACT_n) define the command and/or address being entered. See the ACT_n de-

scription in this table.

RESET_n Input Active LOW asynchronous reset: Reset is active when RESET_n is LOW, and in-

active when RESET_n is HIGH. RESET_n must be HIGH during normal operation.

RESET_n is a CMOS rail-to-rail signal with DC HIGH and LOW at 80% and 20% of

V

DD

; that is, 960 mV for DC HIGH and 240 mV for DC LOW.

TEN Input Connectivity test mode: TEN is active when HIGH and inactive when LOW. TEN

must be LOW during normal operation. TEN is a CMOS rail-to-rail signal with DC

HIGH and LOW at 80% and 20% of V

DD

(960mV for DC HIGH and 240mV for DC

LOW).

16Gb: x4, x8 TwinDie DDR4 SDRAM

Ball Assignments and Descriptions

PDF: 09005aef85fd40a1

DDR4_16Gb_x4_x8_2CS_TwinDie.pdf - Rev. D 12/16 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.