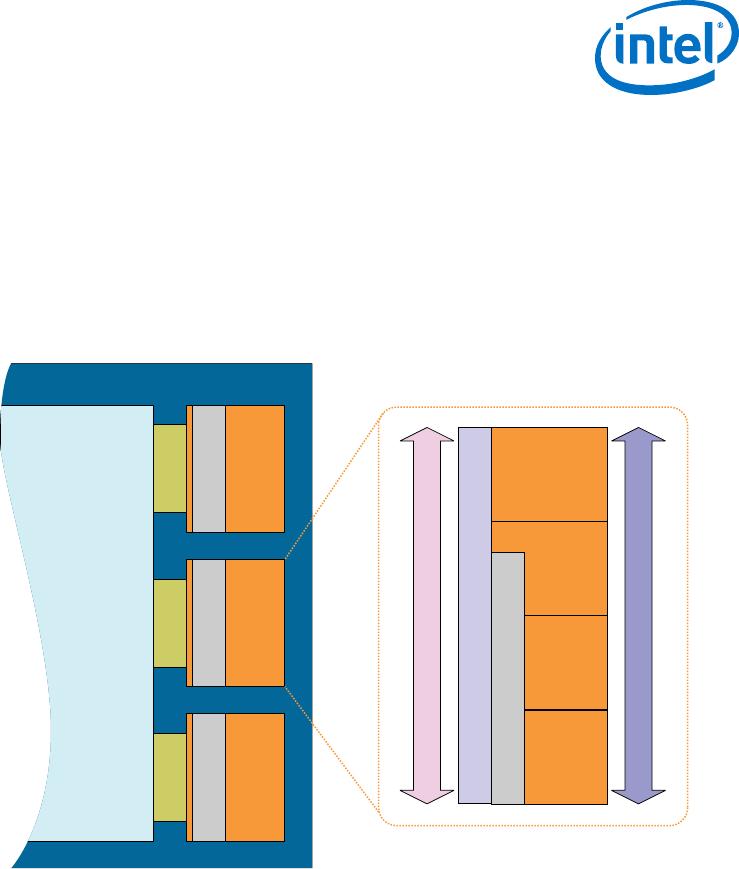

Within each transceiver tile, the transceivers are arranged in four banks of six PMA-

PCS groups. A wide variety of bonded and non-bonded data rate configurations are

possible within each bank, and within each tile, using a highly configurable clock

distribution network.

1.8.1. PMA Features

PMA channels are comprised of transmitter (TX), receiver (RX), and high speed

clocking resources.

Intel Stratix 10 device features provide exceptional signal integrity at data rates up to

28.3 Gbps. Clocking options include ultra-low jitter LC tank-based (ATX) PLLs with

optional fractional synthesis capability, channel PLLs operating as clock multiplier units

(CMUs), and fractional synthesis PLLs (fPLLs).

• ATX PLL—can be configured in integer mode, or optionally, in a new fractional

synthesis mode. Each ATX PLL spans the full frequency range of the supported

data rate range providing a stable, flexible clock source with the lowest jitter.

• CMU PLL—when not being used as a transceiver, select PMA channels can be

configured as channel PLLs operating as CMUs to provide an additional master

clock source within the transceiver bank.

• fPLL—In addition, dedicated fPLLs are available with precision frequency synthesis

capabilities. fPLLs can be used to synthesize multiple clock frequencies from a

single reference clock source and replace multiple reference oscillators for multi-

protocol and multi-rate applications.

On the receiver side, each PMA has an independent channel PLL that allows analog

tracking for clock-data recovery. Each PMA also has advanced equalization circuits that

compensate for transmission losses across a wide frequency spectrum.

• Variable Gain Amplifier (VGA)—to optimize the receiver's dynamic range

• Continuous Time Linear Equalizer (CTLE)—to compensate for channel losses

with lowest power dissipation

• Decision Feedback Equalizer (DFE)—to provide additional equalization

capability on backplanes even in the presence of crosstalk and reflections

• On-Die Instrumentation (ODI)—to provide on-chip eye monitoring capabilities

(Eye Viewer). This capability helps to optimize link equalization parameters during

board bring-up and supports in-system link diagnostics and equalization margin

testing

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

18