Feature Description

Communication Interface

Controllers

• Three 10/100/1000 Ethernet media access controls (MAC) with integrated DMA

— Supports RGMII and RMII external PHY Interfaces

— Option to support other PHY interfaces through FPGA logic

• GMII

• MII

• RMII (requires MII to RMII adapter)

• RGMII (requires GMII to RGMII adapter)

• SGMII (requires GMII to SGMII adapter)

— Supports IEEE 1588-2002 and IEEE 1588-2008 standards for precision networked

clock synchronization

— Supports IEEE 802.1Q VLAN tag detection for reception frames

— Supports Ethernet AVB standard

• Two USB On-the-Go (OTG) controllers with DMA

— Dual-Role Device (device and host functions)

• High-speed (480 Mbps)

• Full-speed (12 Mbps)

• Low-speed (1.5 Mbps)

• Supports USB 1.1 (full-speed and low-speed)

— Integrated descriptor-based scatter-gather DMA

— Support for external ULPI PHY

— Up to 16 bidirectional endpoints, including control endpoint

— Up to 16 host channels

— Supports generic root hub

— Configurable to OTG 1.3 and OTG 2.0 modes

• Five I

2

C controllers (three can be used by EMAC for MIO to external PHY)

— Support both 100Kbps and 400Kbps modes

— Support both 7-bit and 10-bit addressing modes

— Support Master and Slave operating mode

• Two UART 16550 compatible

— Programmable baud rate up to 115.2Kbaud

• Four serial peripheral interfaces (SPI) (2 Master, 2 Slaves)

— Full and Half duplex

Timers and I/O

• Timers

— 4 general-purpose timers

— 4 watchdog timers

• 48 HPS direct I/O allow HPS peripherals to connect directly to I/O

• Up to three IO48 banks may be assigned to HPS for HPS DDR access

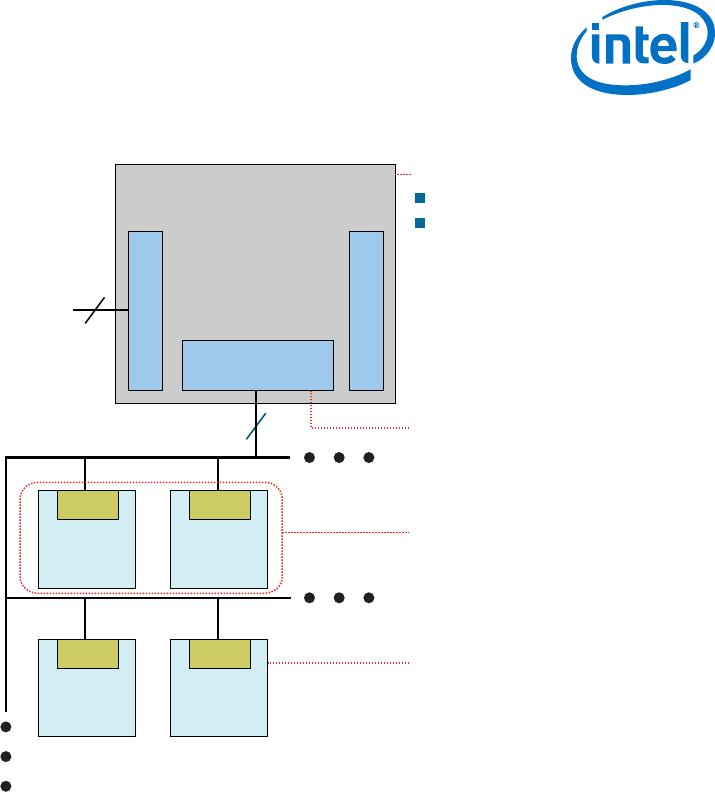

Interconnect to Logic Core • FPGA-to-HPS Bridge

— Allows IP bus masters in the FPGA fabric to access to HPS bus slaves

— Configurable 32-, 64-, or 128-bit AMBA AXI interface

• HPS-to-FPGA Bridge

— Allows HPS bus masters to access bus slaves in FPGA fabric

— Configurable 32-, 64-, or 128-bit AMBA AXI interface allows high-bandwidth HPS

master transactions to FPGA fabric

• HPS-to-SDM and SDM-to-HPS Bridges

— Allows the HPS to reach the SDM block and the SDM to bootstrap the HPS

• Light Weight HPS-to-FPGA Bridge

— Light weight 32-bit AXI interface suitable for low-latency register accesses from HPS

to soft peripherals in FPGA fabric

• FPGA-to-HPS SDRAM Bridge

— Up to three AMBA AXI interfaces supporting 32, 64, or 128-bit data paths

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

31