IDT70V659/58/57S

High-Speed 3.3V 128/64/32K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

18

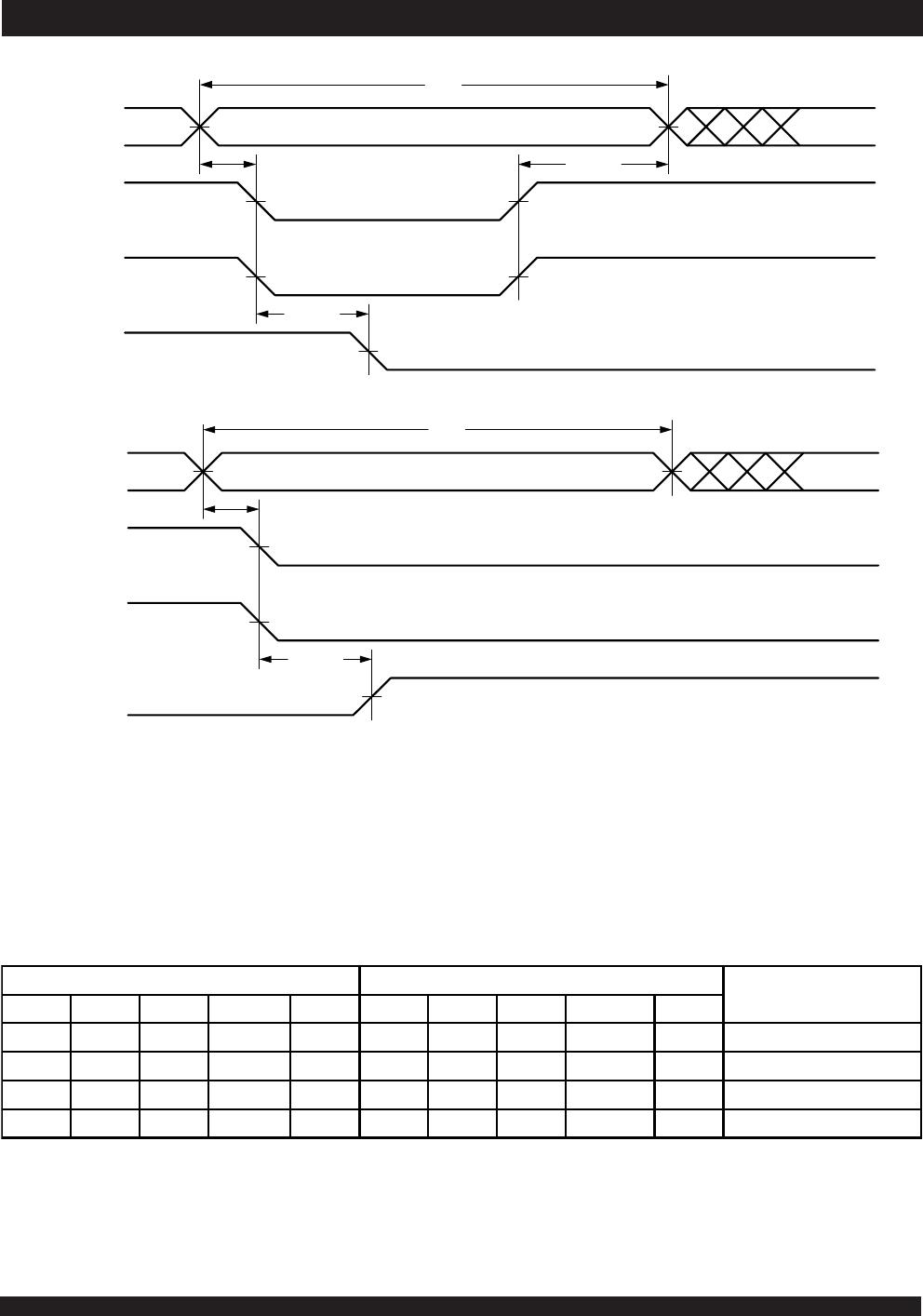

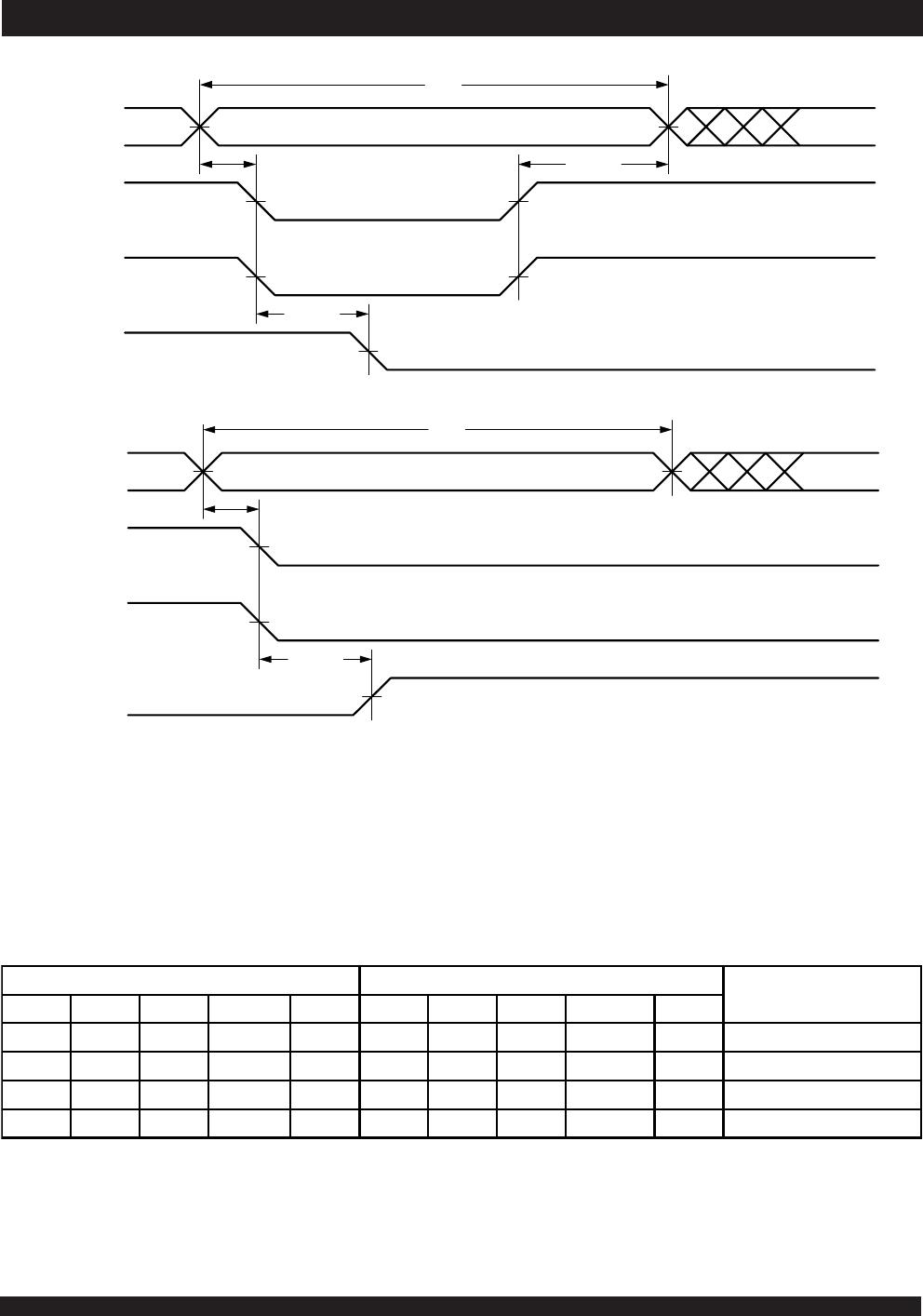

Truth Table III — Interrupt Flag

(1,4)

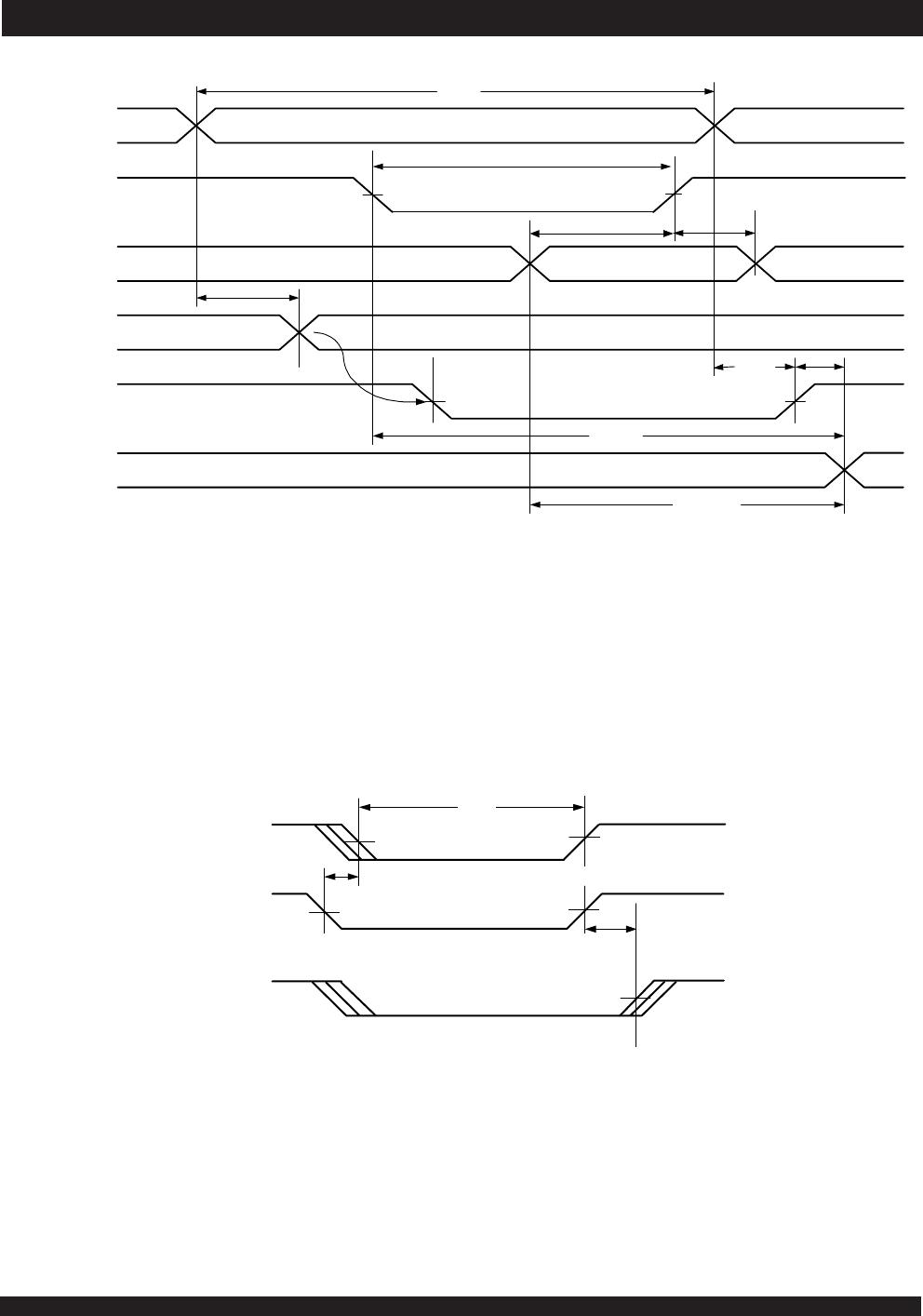

Waveform of Interrupt Timing

(1)

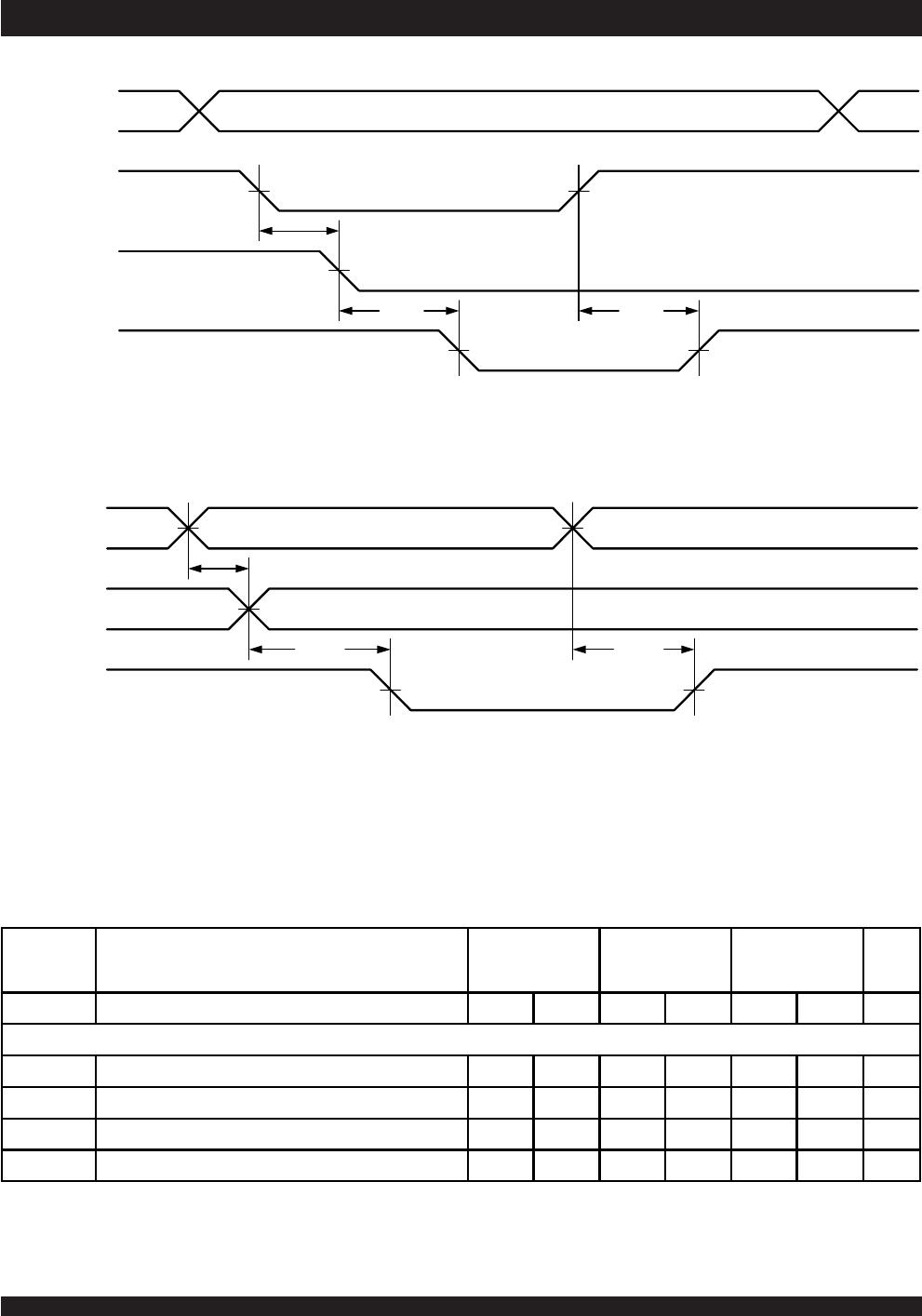

NOTES:

1. All timing is the same for left and right ports. Port “A” may be either the left or right port. Port “B” is the port opposite from port “A”.

2. Refer to Interrupt Truth Table.

3. Timing depends on which enable signal (CE or R/W) is asserted last.

4. Timing depends on which enable signal (CE

or R/W) is de-asserted first.

NOTES:

1. Assumes BUSY

L = BUSYR =VIH.

2. If BUSY

L = VIL, then no change.

3. If BUSY

R = VIL, then no change.

4. INT

L and INTR must be initialized at power-up.

5. A

16x is a NC for IDT70V658, therefore Interrupt Addresses are FFFF and FFFE.

6. A

16x and A15x are NC's for IDT70V657, therefore Interrupt Addresses are 7FFF and 7FFE.

4869 drw 16

ADDR

"A"

INTERRUPT SET ADDRESS

CE

"A"

R/W

"A"

t

AS

t

WC

t

WR

(3)

(4)

t

INS

(3)

INT

"B"

(2)

4869 drw 17

ADDR

"B"

INTERRUPT CLEAR ADDRESS

CE

"B"

OE

"B"

t

AS

t

RC

(3)

t

INR

(3)

INT

"B"

(2)

Left Port Right Port

FunctionR/W

L

CE

L

OE

L

A

16L

-A

0L

(5,6)

INT

L

R/W

R

CE

R

OE

R

A

16R

-A

0R

(5,6)

INT

R

L L X 1FFFF XXXX X L

(2 )

Set Right INT

R

Flag

XXXXXXLL1FFFFH

(3 )

Reset Right INT

R

Flag

XXX X L

(3 )

L L X 1FFFE X Set Left INT

L

Flag

X L L 1FFFE H

(2 )

X X X X X Reset Left INT

L

Flag

4869 tbl 16