Table 4. M9K Operation Modes and Port Widths

Operation Modes Port Widths

Single port ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36

Simple dual port ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36

True dual port ×1, ×2, ×4, ×8, ×9, ×16, and ×18

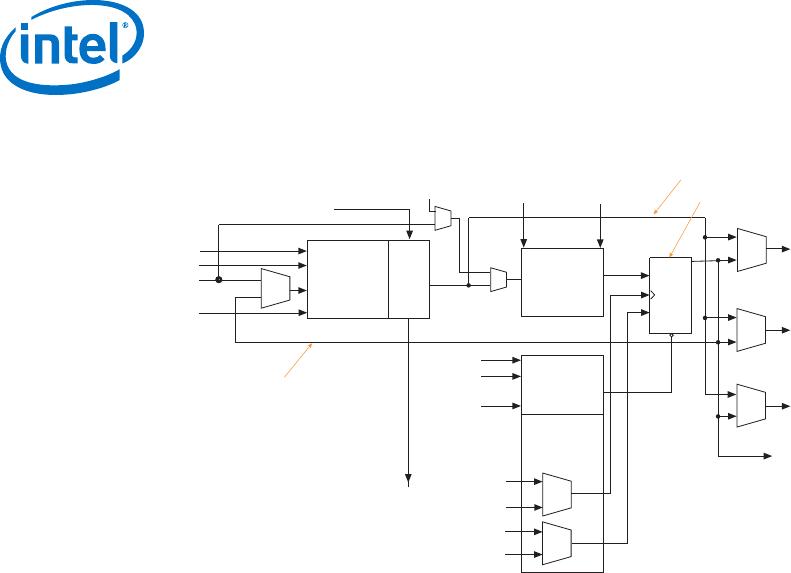

Clocking and PLL

Cyclone 10 LP devices feature global clock (GCLK) networks, dedicated clock pins, and

general purpose PLLs.

• Up to 20 GCLK networks that drive throughout the device

• Up to 15 dedicated clock pins

• Up to four general purpose PLLs with five outputs per PLL

The PLLs provide robust clock management and synthesis for the Cyclone 10 LP

device. You can dynamically reconfigure the PLLs in user mode to change the clock

phase or frequency.

FPGA General Purpose I/O

Cyclone 10 LP devices offer highly configurable GPIOs with these features:

• Support for over 20 popular single-ended and differential I/O standards.

• Programmable bus hold, pull-up resistors, delay, and drive strength.

• Programmable slew-rate control to optimize signal integrity.

• Calibrated on-chip series termination (R

S

OCT) or driver impedance matching (R

S

)

for single-endd I/O standards.

• True and emulated LVDS buffers with LVDS SERDES implemented using logic

elements in the device core.

• Hot socketing support.

Configuration

Cyclone 10 LP devices use SRAM cells to store configuration data. Configuration data

is downloaded to the Cyclone 10 LP device each time the device powers up.

You can use EPCS or EPCQ (AS x1) flash configuration devices to store configuration

data and configure the Cyclone 10 LP FPGAs.

• Cyclone 10 LP devices support 1.5 V, 1.8 V, 2.5 V, 3.0 V, and 3.3 V programming

voltages and several configuration schemes.

• The single-event upset (SEU) mitigation feature detects cyclic redundancy check

(CRC) errors automatically during configuration and optionally during user mode

1

.

1 User mode error detection is not supported on 1.0 V core voltage Cyclone 10 LP device

variants.

Cyclone

®

10 LP Device Overview

Intel

®

Cyclone

®

10 LP Device Overview

9