MAX7409/MAX7410/MAX7413/MAX7414

5th-Order, Lowpass,

Switched-Capacitor Filters

8 _______________________________________________________________________________________

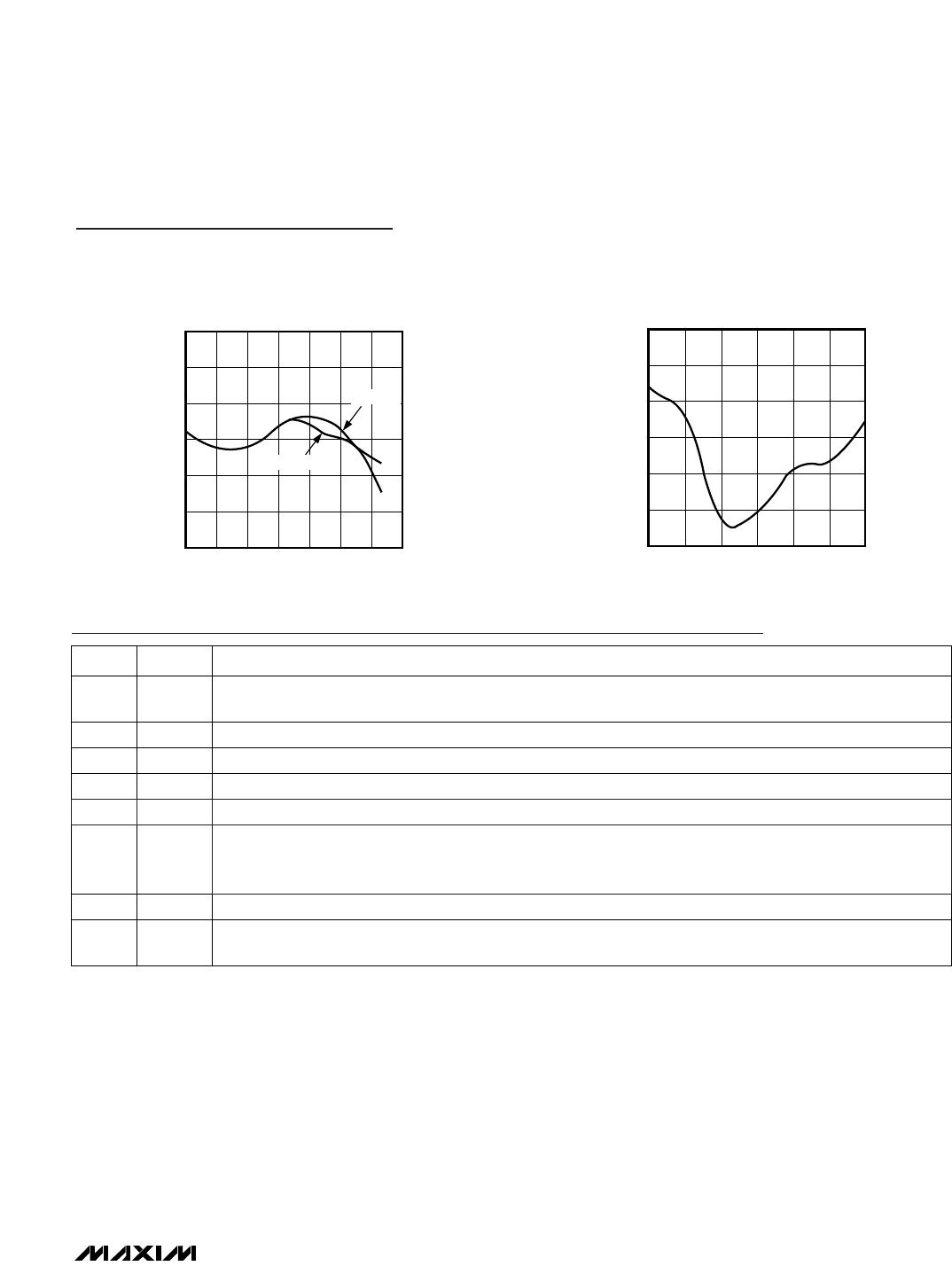

The difference between Bessel and Butterworth filters

can be observed when a 1kHz square wave is applied

to the filter input (Figure 1, trace A). With the filter cutoff

frequencies set at 5kHz, trace B shows the Bessel filter

response and trace C shows the Butterworth filter

response.

Background Information

Most switched-capacitor filters (SCFs) are designed with

biquadratic sections. Each section implements two filter-

ing poles, and the sections are cascaded to produce

higher-order filters. The advantage to this approach is

ease of design. However, this type of design is highly

sensitive to component variations if any section’s Q is

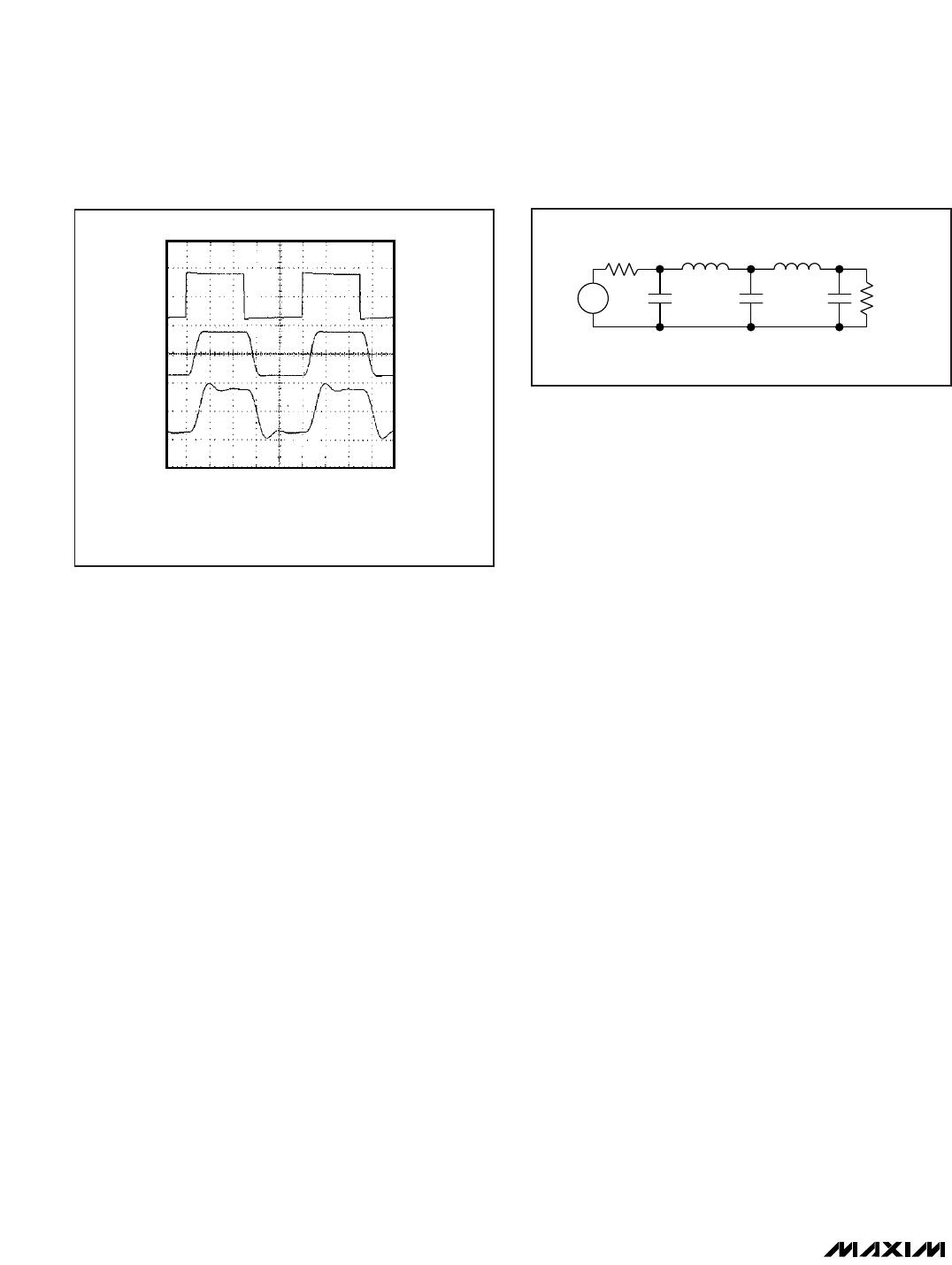

high. An alternative approach is to emulate a passive net-

work using switched-capacitor integrators with summing

and scaling. Figure 2 shows a basic 5th-order ladder filter

structure.

A switched-capacitor filter such as the MAX7409/

MAX7410/MAX7413/MAX7414 emulates a passive ladder

filter. The filter’s component sensitivity is low when com-

pared to a cascaded biquad design, because each

component affects the entire filter shape, not just one

pole-zero pair. In other words, a mismatched component

in a biquad design will have a concentrated error on its

respective poles, while the same mismatch in a ladder

filter design results in an error distributed over all poles.

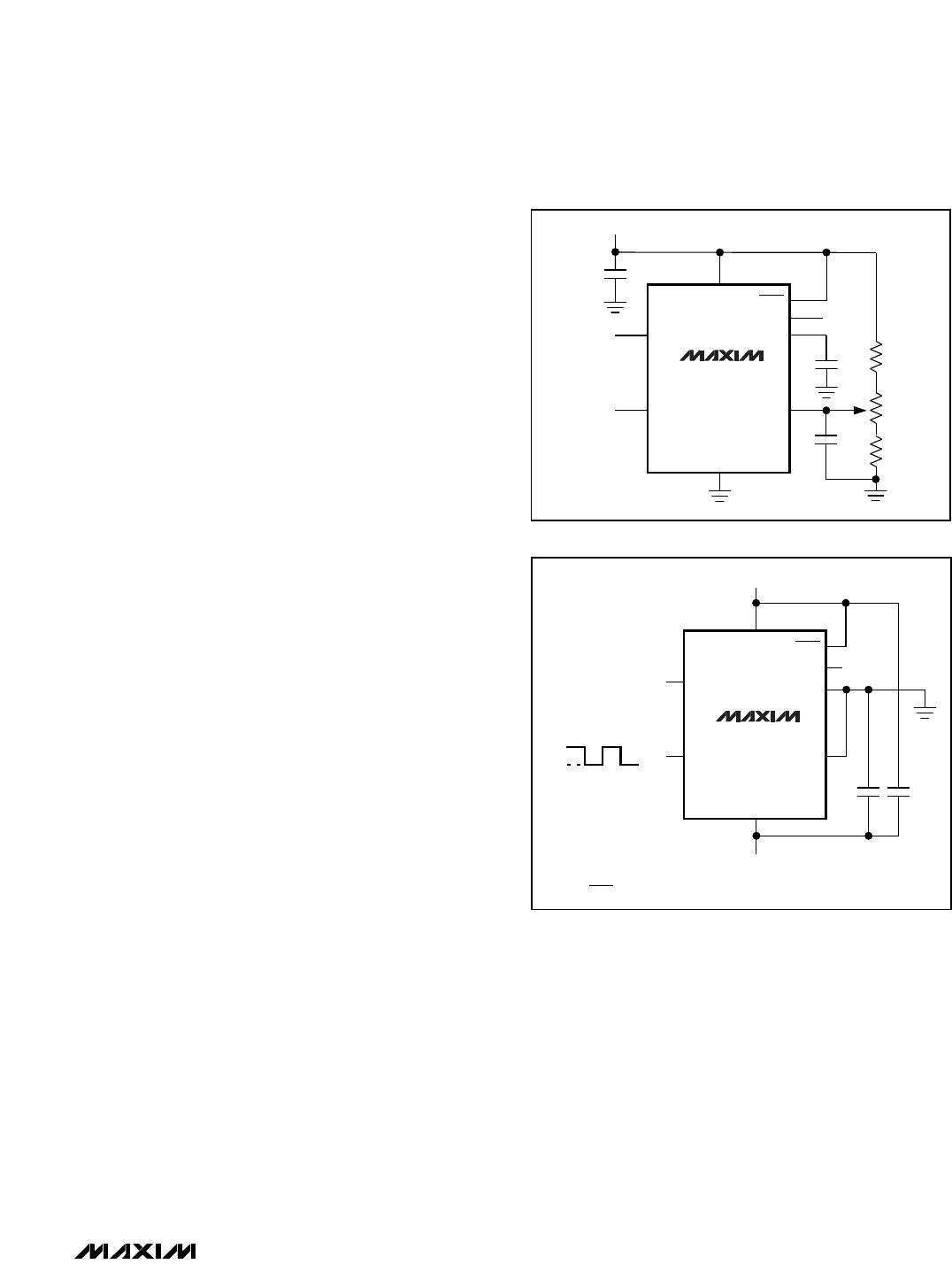

Clock Signal

External Clock

The MAX7409/MAX7410/MAX7413/MAX7414 family of

SCFs is designed for use with external clocks that have

a 50% ±10% duty cycle. When using an external clock

with these devices, drive CLK with a CMOS gate pow-

ered from 0 to V

DD

. Varying the rate of the external

clock adjusts the corner frequency of the filter as fol-

lows:

f

C

= f

CLK

/ 100

Internal Clock

When using the internal oscillator, connect a capacitor

(C

OSC

) between CLK and ground. The value of the

capacitor determines the oscillator frequency as follows:

f

OSC

(kHz) = 30 x 10

3

/ C

OSC

(pF)

Minimize the stray capacitance at CLK so that it does

not affect the internal oscillator frequency. Vary the rate

of the internal oscillator to adjust the filter’s corner fre-

quency by a 100:1 clock-to-corner frequency ratio. For

example, an internal oscillator frequency of 100kHz

produces a nominal corner frequency of 1kHz.

Input Impedance vs. Clock Frequencies

The MAX7409/MAX7410/MAX7413/MAX7414’s input

impedance is effectively that of a switched-capacitor

resistor (see the following equation), and is inversely

proportional to frequency. The input impedance values

determined below represent the average input imped-

ance, since the input current is not continuous. As a

rule, use a driver with an output impedance less than

10% of the filter’s input impedance. Estimate the input

impedance of the filter using the following formula:

Z

IN

= 1 / ( f

CLK

x 2.1pF)

For example, an f

CLK

of 100kHz results in an input

impedance of 4.8MΩ.