8302I Data Sheet

©2016 Integrated Device Technology, Inc Revision A March 4, 20163

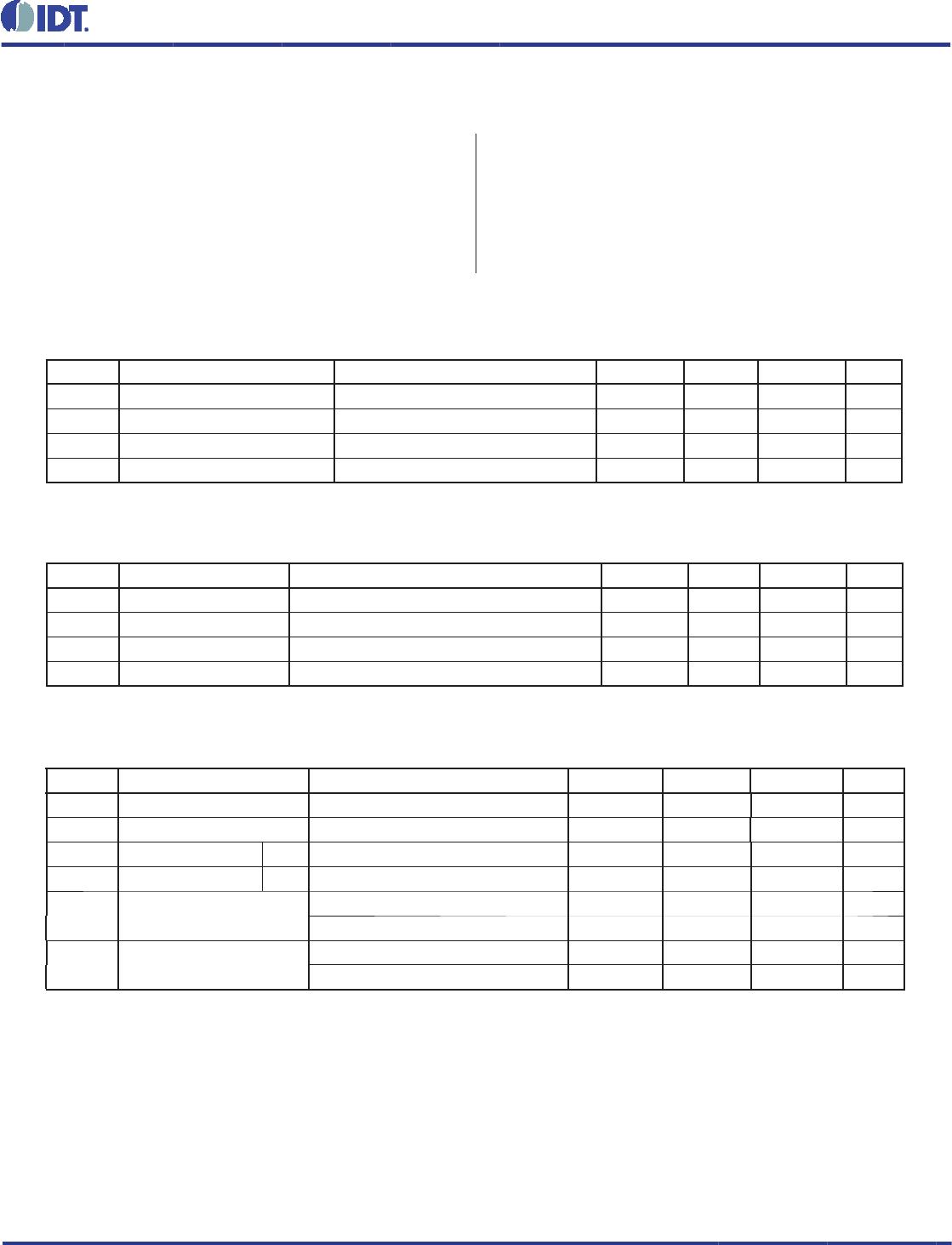

TABLE 3A. POWER SUPPLY DC CHARACTERISTICS, V

DD

= V

DDO

= 3.3V±5%, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

V

DD

Core Supply Voltage 3.135 3.3 3.465 V

V

DDO

Output Power Supply Voltage 3.135 3.3 3.465 V

I

DD

Power Supply Current 14 mA

I

DDO

Output Supply Current 5mA

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5 V

Outputs, V

O

-0.5V to V

DDO

+ 0.5V

Package Thermal Impedance, θ

JA

112.7°C/W (0 lfpm)

Storage Temperature, T

STG

-65°C to 150°C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifi cations only. Functional

operation of product at these conditions or any conditions

beyond those listed in the DC Characteristics or AC Charac-

teristics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

TABLE 3B. POWER SUPPLY DC CHARACTERISTICS, V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

V

DD

Core Supply Voltage 3.135 3.3 3.465 V

V

DDO

Output Supply Voltage 2.375 2.5 2.625 V

I

DD

Power Supply Current 14 mA

I

DDO

Output Supply Current 5mA

TABLE 3C. LVCMOS / LVTTL DC CHARACTERISTICS, V

DD

= V

DDO

= 3.3V±5%, TA = -40°C TO 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

V

IH

Input High Voltage 2 V

DD

+ 0.3 V

V

IL

Input Low Voltage -0.3 1.3 V

I

IH

Input High Current CLK V

DD

= V

IN

= 3.465V 150 µA

I

IL

Input Low Current CLK V

DD

= 3.465V, V

IN

= 0V -5 µA

V

OH

Output High Voltage

50Ω to V

DDO

/2 2.6 V

I

OH

= -100µA 2.9 V

V

OL

Output Low Voltage

50Ω to V

DDO

/2 0.5 V

I

OL

= 100µA 0.2 V