ADM1073 Data Sheet

Rev. B | Page 20 of 24

CURRENT FAULTS

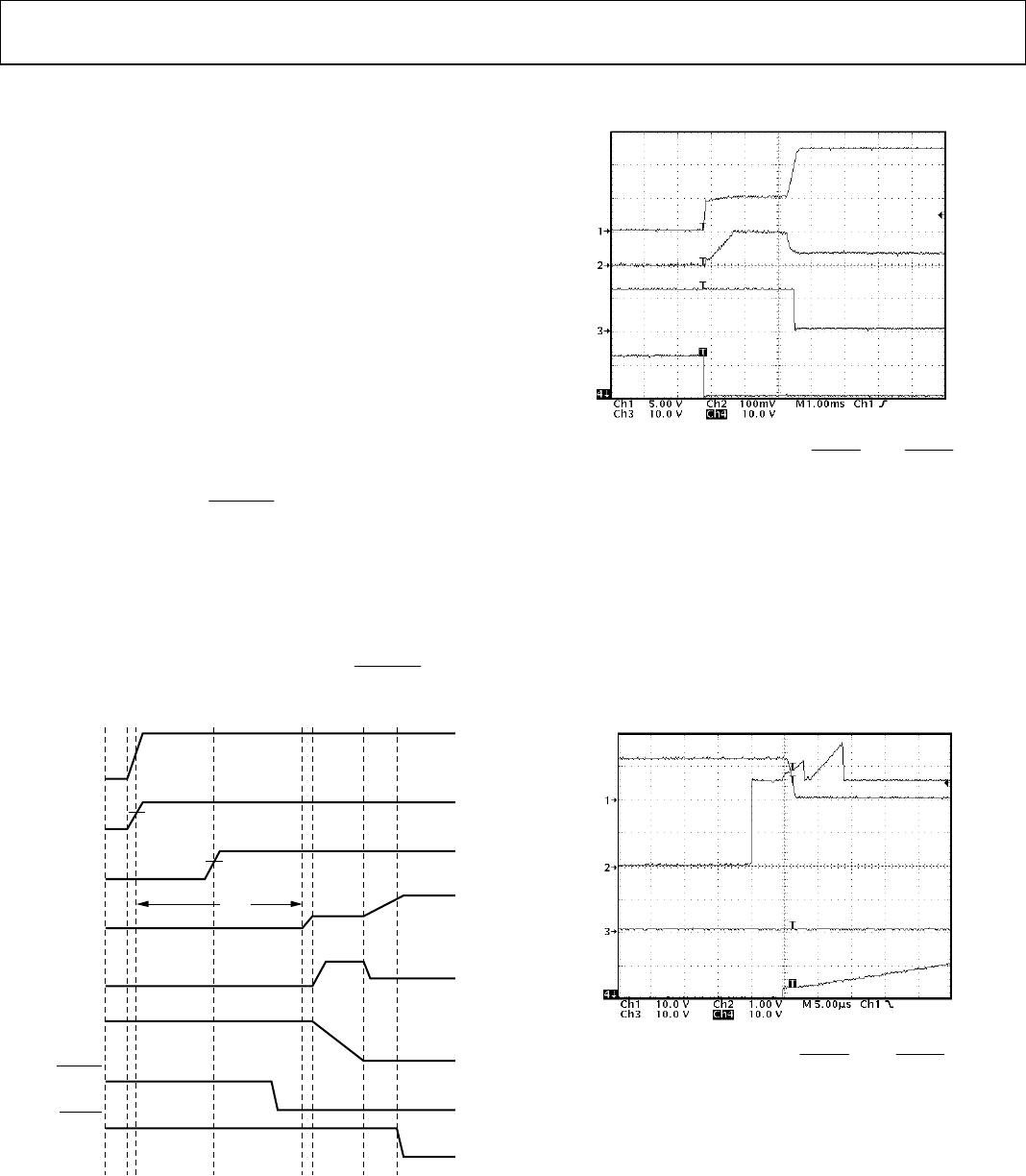

Some timing waveforms associated with overcurrent faults are

shown in the following figures. Figure 43 shows how a perma-

nent current fault is dealt with after startup.

SPLYGD

going low

indicates when the supply voltage is good. Because the output is

shorted, the sense voltage immediately rises through the 90 mV

circuit breaker threshold, and the fault timer is started. The

linear current control loop then goes into regulation at V

SENSE

=

100 mV, accurately limiting the load current at the preset level.

The limited consecutive retry scheme PWMs the GATE pin

seven times. When the seventh retry occurs, the permanent

fault is deemed permanent and the part latches off. The

LATCHED

output asserts at this time. Power must now be

cycled to restart the device. This can be achieved via a manual

card reseating event (which cycles the power) or with an

external

RESTART

or

SHDN

signal.

Figure 43. Timing Waveforms Associated with a Current Fault at Startup,

Using Limited Consecutive Retry (Ch1 = GATE; Ch2 = SENSE;

Ch3 =

SPLYGD

; Ch4 =

LATCHED

)

Note that the

LATCHED

output can also be tied back to the

RESTART

input, giving an infinite retry during current fault

with a 5-second cool-down period after every seven retries. The

waveforms for this event are similar to those in

Figure 43, but

repeats every five seconds.

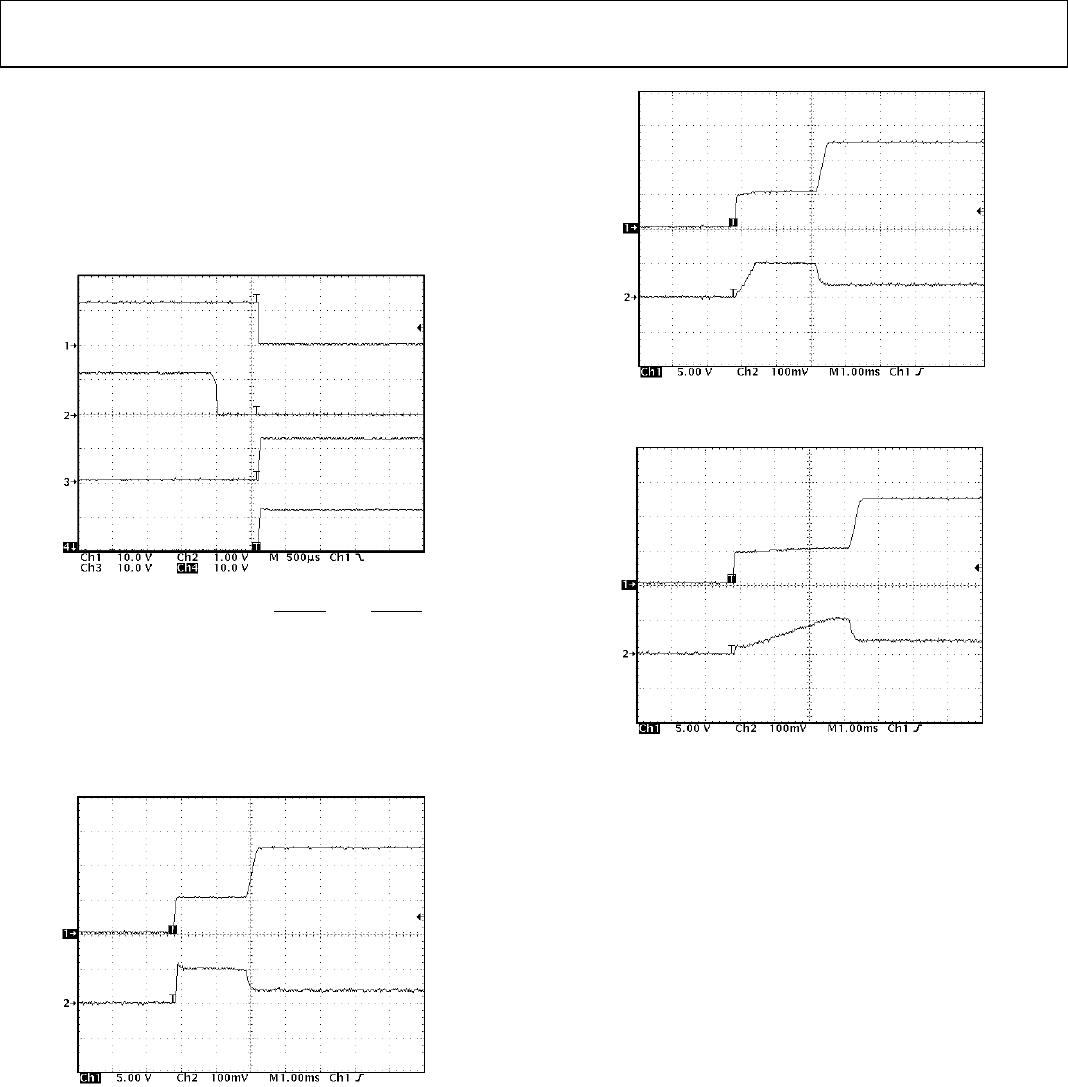

Figure 44 shows the behavior of ADM1073 when a temporary

current fault occurs followed by a permanent current fault.

When the first overcurrent fault occurs, the first 97.5 mV spike

on the SENSE line can be seen. The ADM1073 retries a number

of times, and during the fifth t

OFF

time this current fault corrects

itself. After this time period, a no-fault condition is detected

and the limited consecutive counter is reset. GATE is reasserted.

When the overcurrent fault returns permanently, the limited

consecutive retry counter detects seven consecutive faults and

the part latches off. In this way, the ADM1073 prevents

nuisance shutdowns caused by transient shorts of a

programmable duration (typically ~0.6 s, set via TIMER, as

follows), but provides latched shutdown protection from

permanently shorted loads.

Figure 44. Timing Waveforms Associated with a Temporary Current Fault

Followed by a Permanent Current Fault

(Ch1 = GATE; Ch2 = SENSE)

Figure 45 shows the behavior of the TIMER pin during a retry

cycle. Different current sources are switched in during the

on-time (TIMER ramping up) and off-times (TIMER ramping

down). This can be seen in the varying ramp-up and ramp-

down rates of TIMER below. The default ratio of t

ON

to t

OFF

is

6%. This ratio can be reduced with a resistor from TIMER to

V

EE

or increased with a resistor from TIMER to V

IN

. The total

retry period can be extended or reduced by changing the value

of the TIMER capacitor.

Figure 45. Timing Waveforms during a Retry Cycle for C

TIMER

= 0.82 nF

(Ch1 = GATE; Ch2 = SENSE; Ch3 = TIMER)