LTC2941

11

2941fb

For more information www.linear.com/LTC2941

be chosen for a given battery capacity Q

BAT

and a sense

resistor R

SENSE

as:

M≥128 •

BAT

16

•

SENSE

50mΩ

M can be set to 1, 2, 4, 8, …128 by programming B[5:3]

of the control register as M = 2

(4 • B[5] + 2 • B[4] + B[3])

. The

default value after power up is M = 128 = 2

7

(B[5:3] = 111).

In the above example of a 100mAh battery and a R

SENSE

of 50mΩ, the prescaler should be programmed to M = 4.

The q

LSB

then becomes 2.656µAh and the battery capacity

corresponds to roughly 37650 q

LSB

s.

Note that the internal digital resolution of the coulomb

counter is higher than indicated by q

LSB

. The digitized

charge q

INTERNAL

is M • 8 smaller than q

LSB

. q

INTERNAL

is

typically 299µAs for a 50mΩ sense resistor.

V

BAT

Alert B[7:6]

The V

BAT

alert function allows the LTC2941 to monitor

the voltage at SENSE

–

. If enabled, a drop of the voltage

at the SENSE

–

pin below a preset threshold is detected

and bit A[1] in the status register is set. If the alert mode

is enabled by setting B[2] to one, an alert is generated at

the AL/CC pin. The threshold for the V

BAT

alert function

is selectable according to Table 3.

Accumulated Charge Registers (C, D)

The coulomb counter of the LTC2941 integrates current

through the sense resistor. The 16-bit result of this charge

integration is stored in the accumulated charge registers

C and D. As the LTC2941 does not know the actual battery

status after initial power-up, the accumulated charge is

set to mid-scale (7FFFh). If the host knows the status of

the battery , the accumulated charge registers C[7:0] and

D[7:0] can be either programmed to the correct value via

I

2

C or it can be set after charging to FFFFh (full) by pulling

the AL/CC pin high (if charge complete mode is enabled

via bits B[2:1]). Before writing the accumulated charge

registers, the analog section should be shut down by setting

B[0] to 1. In order to avoid a change in the accumulated

charge registers between reading MSBs C[7:0] and LSBs

D[7:0], it is recommended to read them sequentially, as

shown in Figure 8.

Threshold Registers (E, F), (G, H)

For battery charge, the LTC2941 features a high and a

low threshold register. At power-up the high threshold

is set to FFFFh while the low threshold is set to 0000h.

Both thresholds can be programmed to a desired value via

I

2

C. As soon as the accumulated charge exceeds the high

threshold or falls below the low threshold, the LTC2941

sets the corresponding flag in the status register and pulls

the AL/CC pin low if alert mode is enabled.

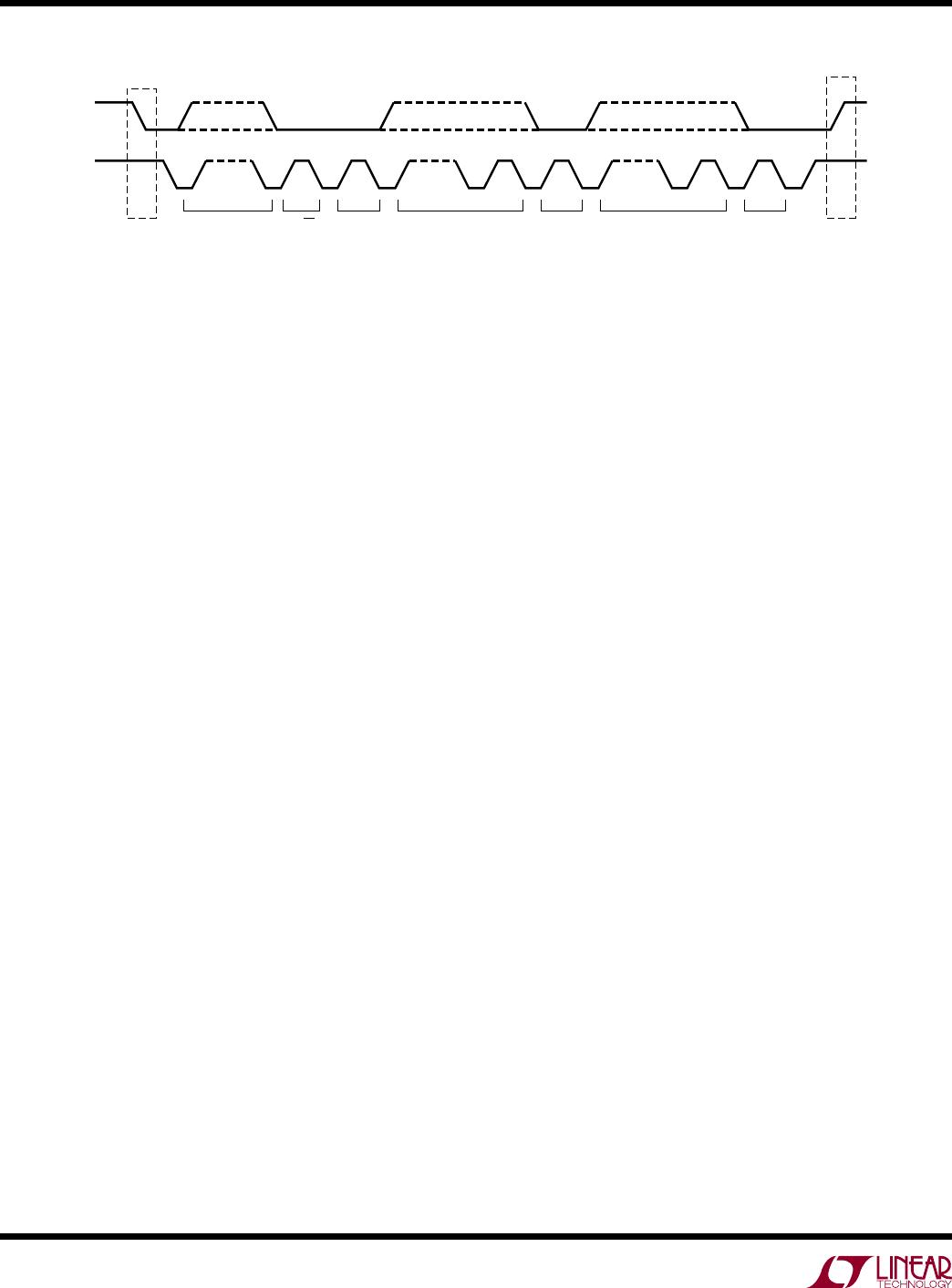

I

2

C Protocol

The LTC2941 uses an I

2

C/SMBus compatible 2-wire open-

drain interface supporting multiple devices and masters on

a single bus. The connected devices can only pull the bus

wires LOW and they never drive the bus HIGH. The bus

wires should be externally connected to a positive sup

-

ply voltage via a current source or pull-up resistor. When

the bus is idle, both SDA and SCL are HIGH. Data on the

I

2

C-bus can be transferred at rates of up to 100kbit/s in

standard mode and up to 400kbit/s in fast mode.

Each device on the I

2

C/SMBus is recognized by a unique

address stored in that device and can operate as either a

transmitter or receiver, depending on the function of the

device. In addition to transmitters and receivers, devices

can also be classified as masters or slaves when perform

-

ing data transfers. A master is the device which initiates a

data

transfer

on the bus and generates the clock signals to

permit that transfer. At the same time any device addressed

is considered a slave. The LTC2941 always acts as a slave.

Figure 4 shows an overview of the data transmission on

the I

2

C bus.

applicaTions inFormaTion