ZL40210 Data Sheet

6

Microsemi Corporation

3.0 Functional Description

The ZL40210 is an LVPECL clock fanout buffer with eight output clock drivers capable of operating at frequencies

up to 750MHz.

The ZL40210 is designed to fan out

low-jitter reference clocks for wired or optical communications applications

while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors

minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its

operation is guaranteed over the industrial temperature range -40°C to +85°C.

The device block diagram is shown in Figure 1; its operation is described in the following sections.

3.1 Clock Input

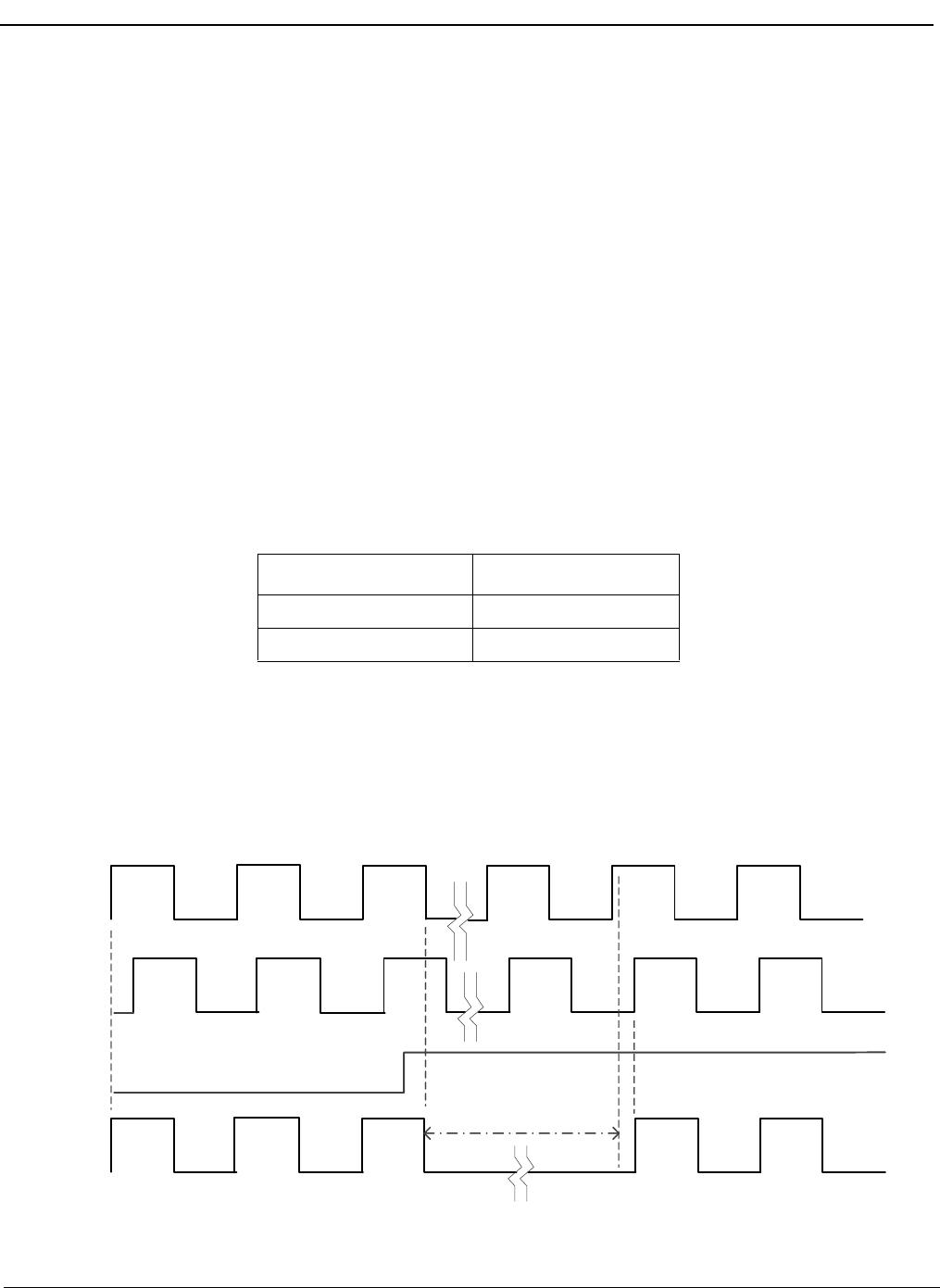

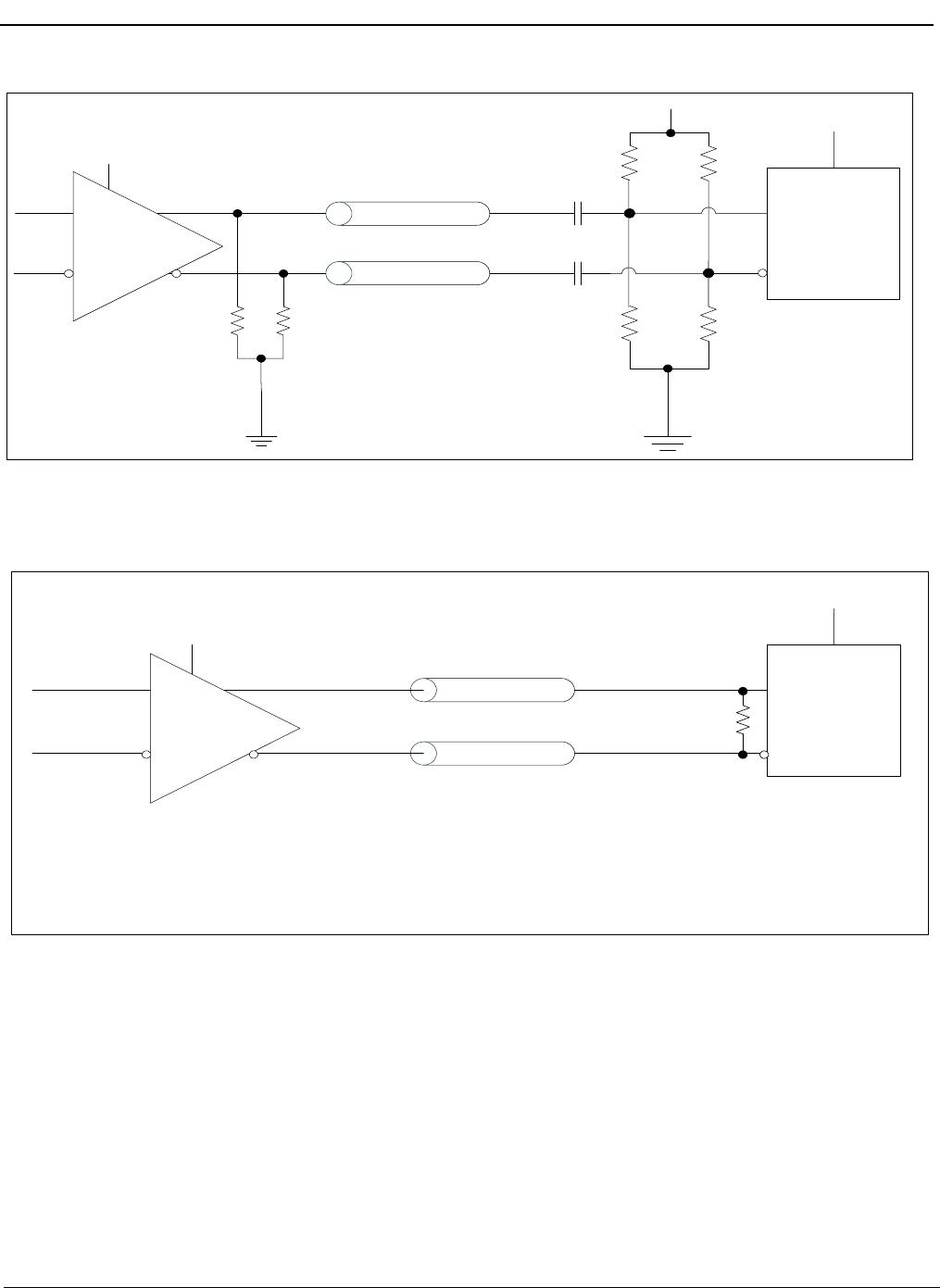

Inputs to the ZL40210 are externally terminated to allow use of precision termination components and to allow full

flexibility of input termination. The ZL40210 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL,

LVDS, CML or HCSL input signals; single ended input signals can also be accepted. A pin compatible device with

internal termination is also available.

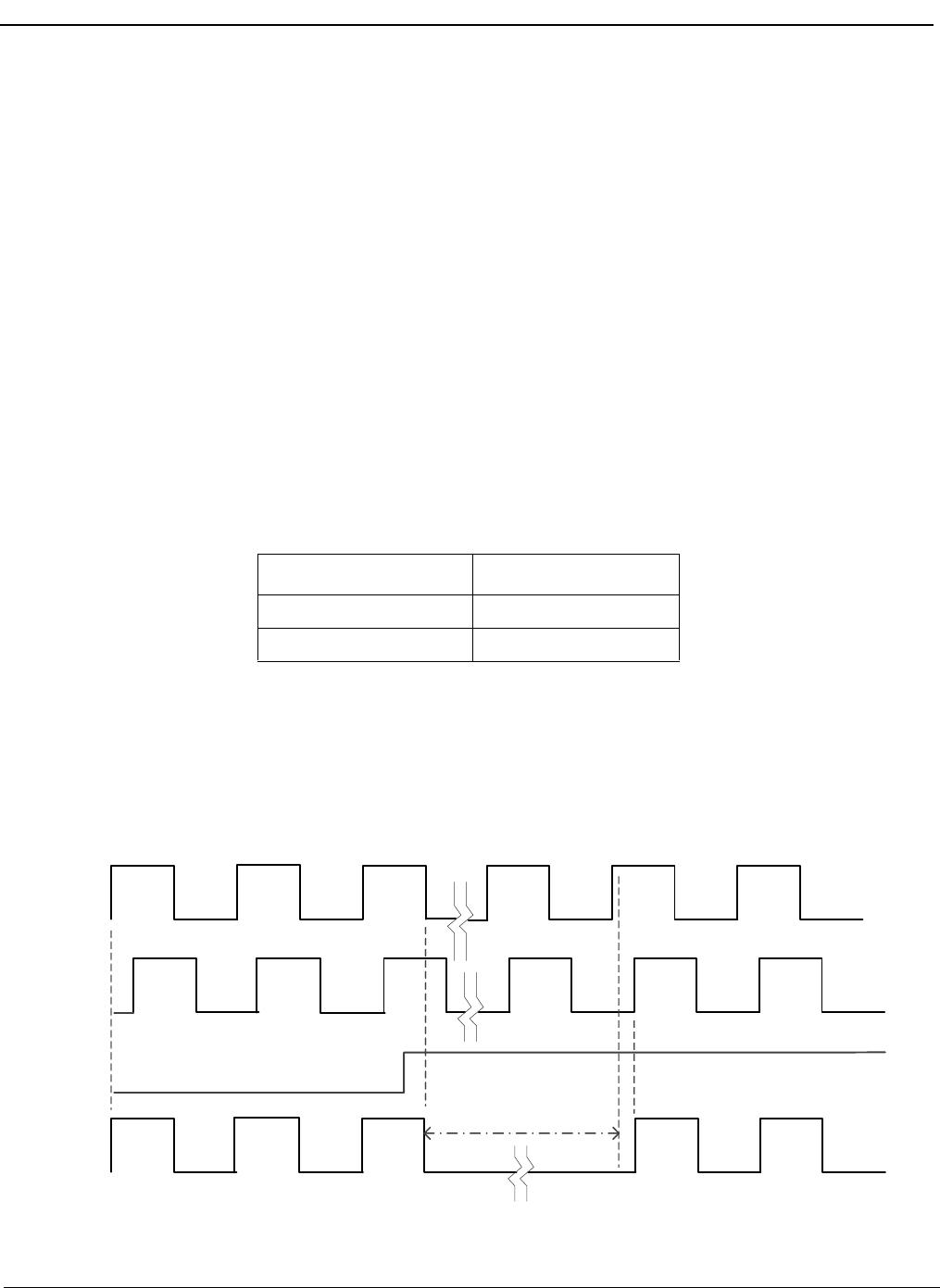

3.1.1 Clock Input Selection

The select line chooses which input clock is routed to the outputs.

Table 1 - Input Selection

Sel Active Input

0 clk0

1 clk1

The following figure shows the expected clock

switching performance. The output stops at the first falling edge of

the initial clock after the select pin changes state. During switching there will be a short time when the output clock

is not toggling. After this delay, the output will start toggling again with a rising edge of the newly selected clock.

This behavior is independent of the frequencies of the input clocks. For instance, the two clocks could be at

different frequencies and the behavior would still be consistent with this figure.

1 µs

clk0

clk1

sel

outn

1

0

Figure 3 - Output During Clock Switch - Both Clocks Running