Production Data WM8737L

w

PD, Rev 4.4, January 2012

25

MASTER AND SLAVE MODE OPERATION

The WM8737L can be configured as either a master or slave mode device. As a master device the

WM8737L generates BCLK and ADCLRC and thus controls sequencing of the data transfer on

ADCDAT. In slave mode, the WM8737L responds with data to clocks it receives over the digital audio

interface. The mode can be selected by writing to the MS bit (see Table 14). Master and slave modes

are illustrated below.

BCLK

ADCDAT

ADCLRC

WM8737

ADC

DSP /

ENCODER

BCLK

ADCDAT

ADCLRC

WM8737

ADC

DSP /

ENCODER

Figure 9a Master Mode Figure 9b Slave Mode

AUDIO DATA FORMATS

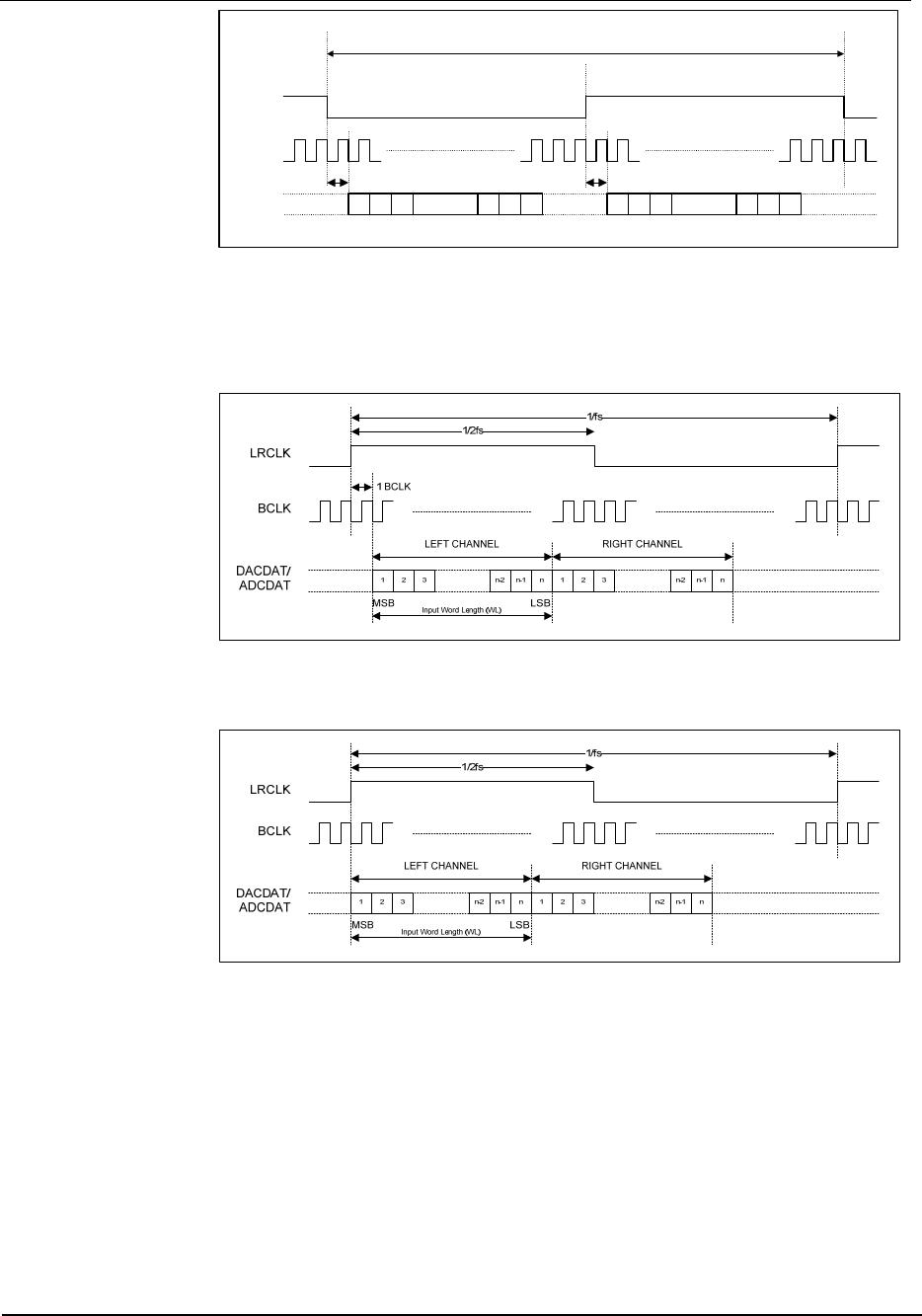

In Left Justified mode, the MSB is available on the first rising edge of BCLK following an ADCLRC

transition. The other bits up to the LSB are then transmitted in order. Depending on word length,

BCLK frequency and sample rate, there may be unused BCLK cycles before each ADCLRC

transition.

LEFT CHANNEL RIGHT CHANNEL

ADCLRC

BCLK

ADCDAT

1/fs

n321

n-2 n-1

LSBMSB

n321

n-2 n-1

LSBMSB

Figure 10 Left Justified Audio Interface (assuming n-bit word length)

In Right Justified mode, the LSB is available on the last rising edge of BCLK before an ADCLRC

transition. All other bits are transmitted before (MSB first). Depending on word length, BCLK

frequency and sample rate, there may be unused BCLK cycles after each ADCLRC transition.

LEFT CHANNEL RIGHT CHANNEL

ADCLRC

BCLK

ADCDAT

1/fs

n321

n-2 n-1

LSBMSB

n321

n-2 n-1

LSBMSB

Figure 11 Right Justified Audio Interface (assuming n-bit word length)

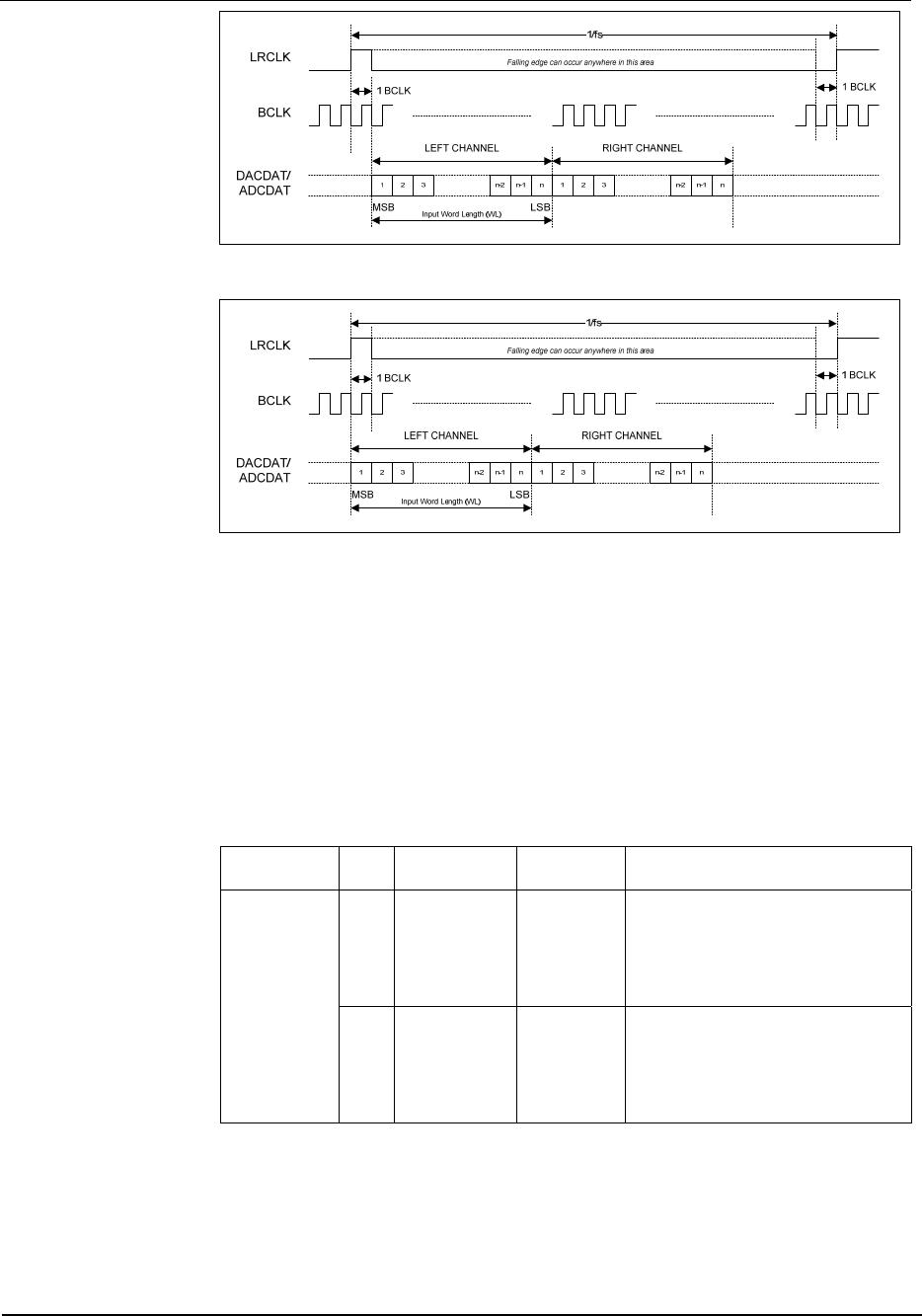

In I

2

S mode, the MSB is available on the second rising edge of BCLK following an ADCLRC

transition. The other bits up to the LSB are then transmitted in order. Depending on word length,

BCLK frequency and sample rate, there may be unused BCLK cycles between the LSB of one sample

and the MSB of the next.