3

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

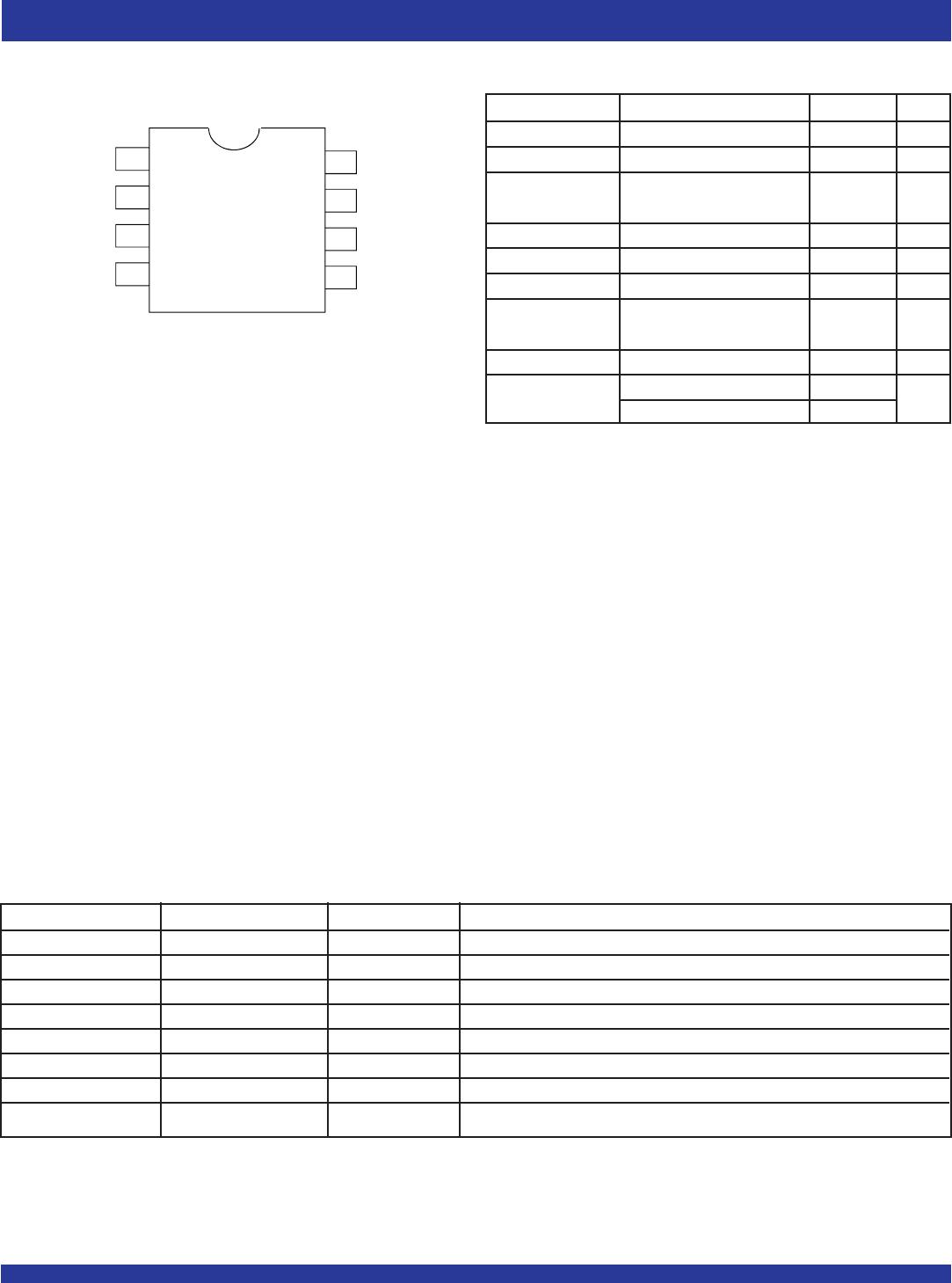

IDT23S05T

2.5V ZERO DELAY CLOCK BUFFER, SPREAD SPECTRUM COMPATIBLE

Symbol Parameter Min. Max. Unit

VDD Supply Voltage 2.3 2.7 V

TA Operating Temperature (Ambient Temperature) Commercial 0 +70 °C

Industrial –40 +85

CL Load Capacitance 10MHz - 133MHz — 15 pF

C

IN Input Capacitance — 7 pF

OPERATING CONDITIONS

DC ELECTRICAL CHARACTERISTICS

Symbol Parameter Conditions Min. Max. Unit

VIL Input LOW Voltage Level — 0.7 V

VIH Input HIGH Voltage Level 1.7 — V

IIL Input LOW Current VIN = 0V — 50 µA

IIH Input HIGH Current VIN = VDD — 100 µA

VOL Output LOW Voltage Standard Drive, IOL = 8mA — 0.3 V

VOH Output HIGH Voltage Standard Drive, IOH = -8mA 2 — V

IDD_PD Power Down Current REF = 0MHz Commercial — 12 µA

Industrial — 25

IDD Supply Current Unloaded Outputs at 66.66MHz — 32 mA

SWITCHING CHARACTERISTICS

(1,2)

Symbol Parameter Conditions Min. Typ. Max. Unit

t1 Output Frequency 15pF Load 10 — 133 MHz

Duty Cycle = t2 ÷ t1 Measured at VDD/2, FOUT = 66.66MHz 40 50 60 %

t3 Rise Time Measured between 0.7V and 1.7V — — 2.5 ns

t4 Fall Time Measured between 0.7V and 1.7V — — 2.5 ns

t5 Output to Output Skew All outputs equally loaded — — 250 ps

t6 Delay, REF Rising Edge to CLKOUT Rising Edge Measured at VDD/2 — 0 ±350 ps

t7 Device-to-Device Skew Measured at VDD/2 on the CLKOUT pins of devices — 0 700 ps

tJ Cycle-to-Cycle Jitter, pk - pk Measured at 66.66MHz, loaded outputs — — 200 ps

t

LOCK PLL Lock Time Stable power supply, valid clock presented on REF pin — — 1 ms

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.