MC74VHC1G126

www.onsemi.com

2

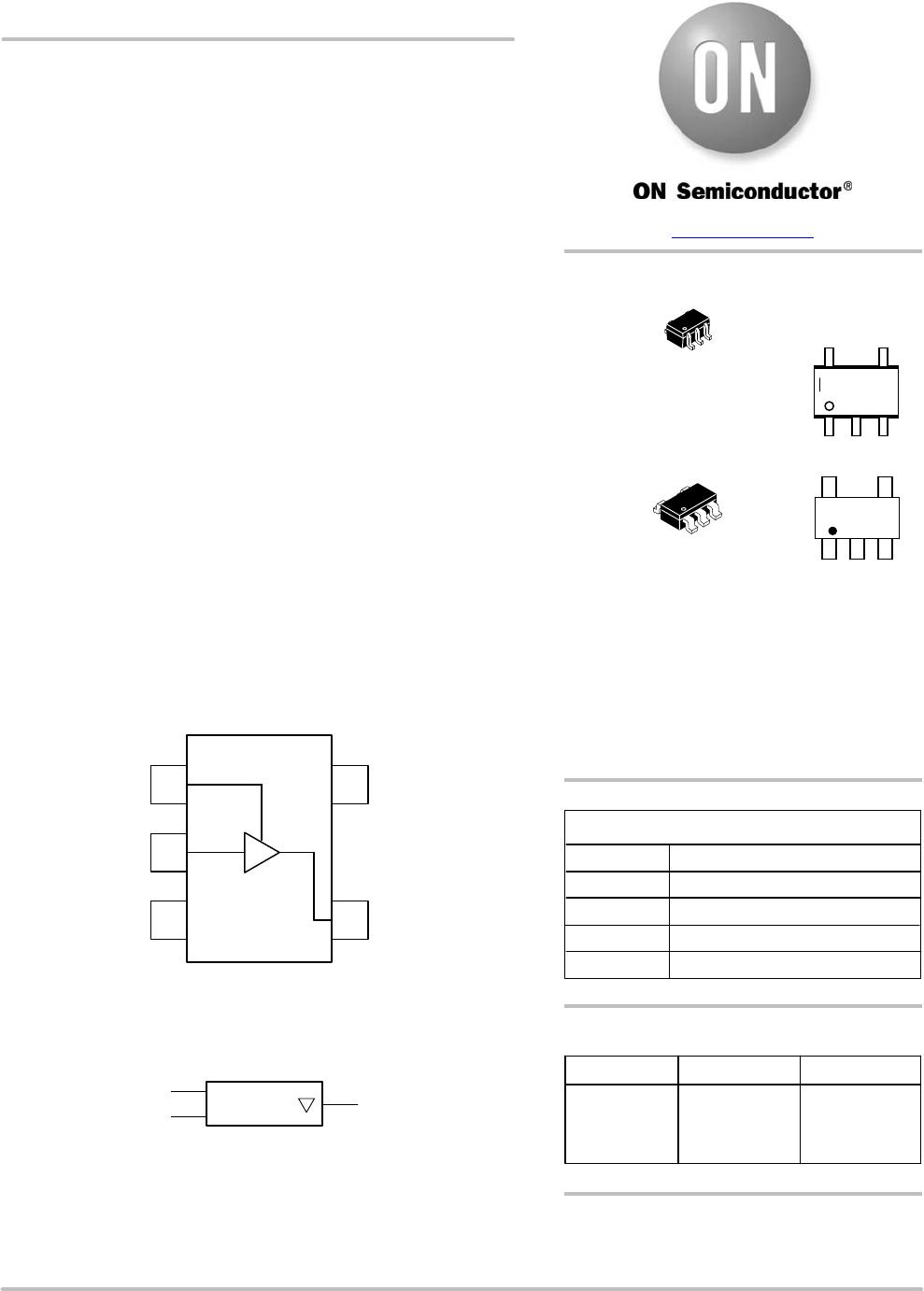

MAXIMUM RATINGS

Symbol Characteristics Value Unit

V

CC

DC Supply Voltage −0.5 to +7.0 V

V

IN

DC Input Voltage −0.5 to +7.0 V

V

OUT

DC Output Voltage V

CC

= 0

High or Low State

−0.5 to 7.0

−0.5 to V

CC

+ 0.5

V

I

IK

Input Diode Current −20 mA

I

OK

Output Diode Current V

OUT

< GND; V

OUT

> V

CC

+20 mA

I

OUT

DC Output Current, per Pin +25 mA

I

CC

DC Supply Current, V

CC

and GND +50 mA

P

D

Power dissipation in still air SC−88A, TSOP−5 200 mW

q

JA

Thermal resistance SC−88A, TSOP−5 333 °C/W

T

L

Lead temperature, 1 mm from case for 10 secs 260 °C

T

J

Junction temperature under bias +150 °C

T

stg

Storage temperature −65 to +150 °C

V

ESD

ESD Withstand Voltage Human Body Model (Note 1)

Machine Model (Note 2)

Charged Device Model (Note 3)

> 2000

> 200

N/A

V

I

Latchup

Latchup Performance Above V

CC

and Below GND at 125°C (Note 4) ±500 mA

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. Tested to EIA/JESD22−A114−A

2. Tested to EIA/JESD22−A115−A

3. Tested to JESD22−C101−A

4. Tested to EIA/JESD78

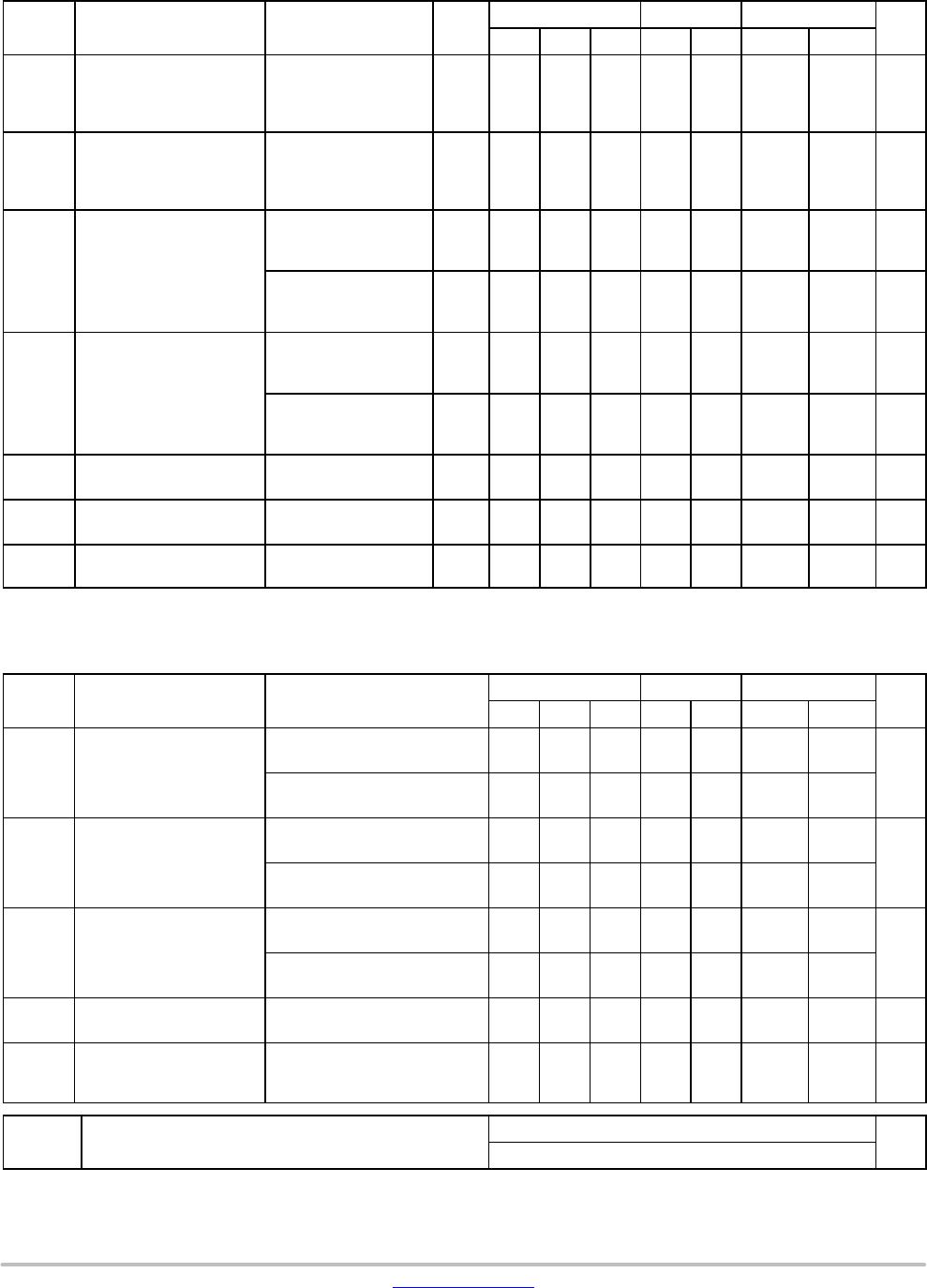

RECOMMENDED OPERATING CONDITIONS

Symbol Characteristics Min Max Unit

V

CC

DC Supply Voltage 2.0 5.5 V

V

IN

DC Input Voltage 0.0 5.5 V

V

OUT

DC Output Voltage 0.0 V

CC

V

T

A

Operating Temperature Range −55 +125 °C

t

r

, t

f

Input Rise and Fall Time V

CC

= 3.3 V ± 0.3 V

V

CC

= 5.0 V ± 0.5 V

0

0

100

20

ns/V

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

Device Junction Temperature versus

Time to 0.1% Bond Failures

Junction

Temperature °C

Time, Hours Time, Years

80 1,032,200 117.8

90 419,300 47.9

100 178,700 20.4

110 79,600 9.4

120 37,000 4.2

130 17,800 2.0

140 8,900 1.0

1

1 10 100

1000

TIME, YEARS

NORMALIZED FAILURE RATE

T

J

= 80

C°

T

J

= 90

C°

T

J

= 100 C°

T

J

= 110 C°

T

J

= 130 C°

T

J

= 120 C°

FAILURE RATE OF PLASTIC = CERAMIC

UNTIL INTERMETALLICS OCCUR

Figure 3. Failure Rate vs. Time Junction Temperature