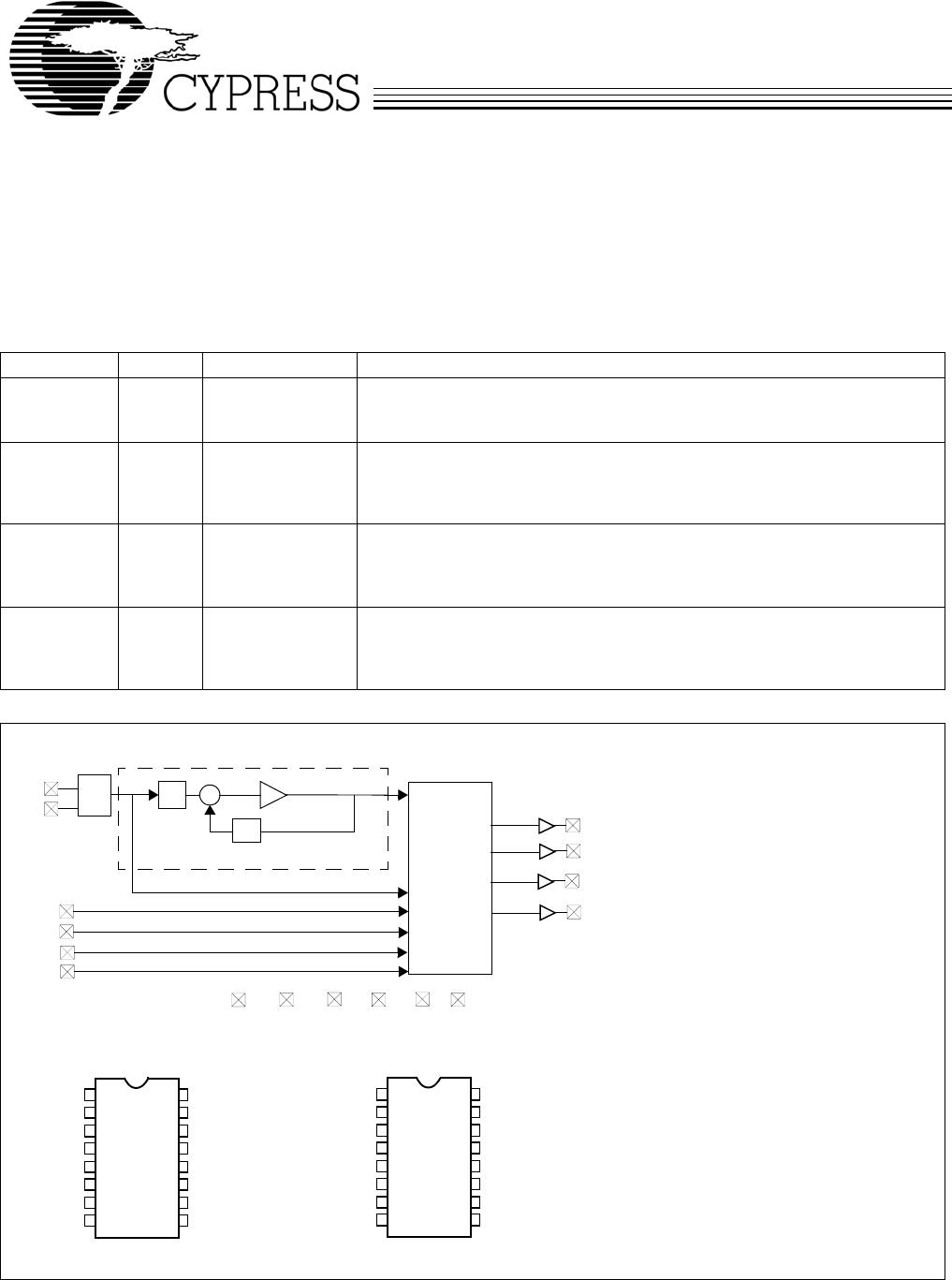

CY24206

Document #: 38-07451 Rev. *B Page 2 of 6

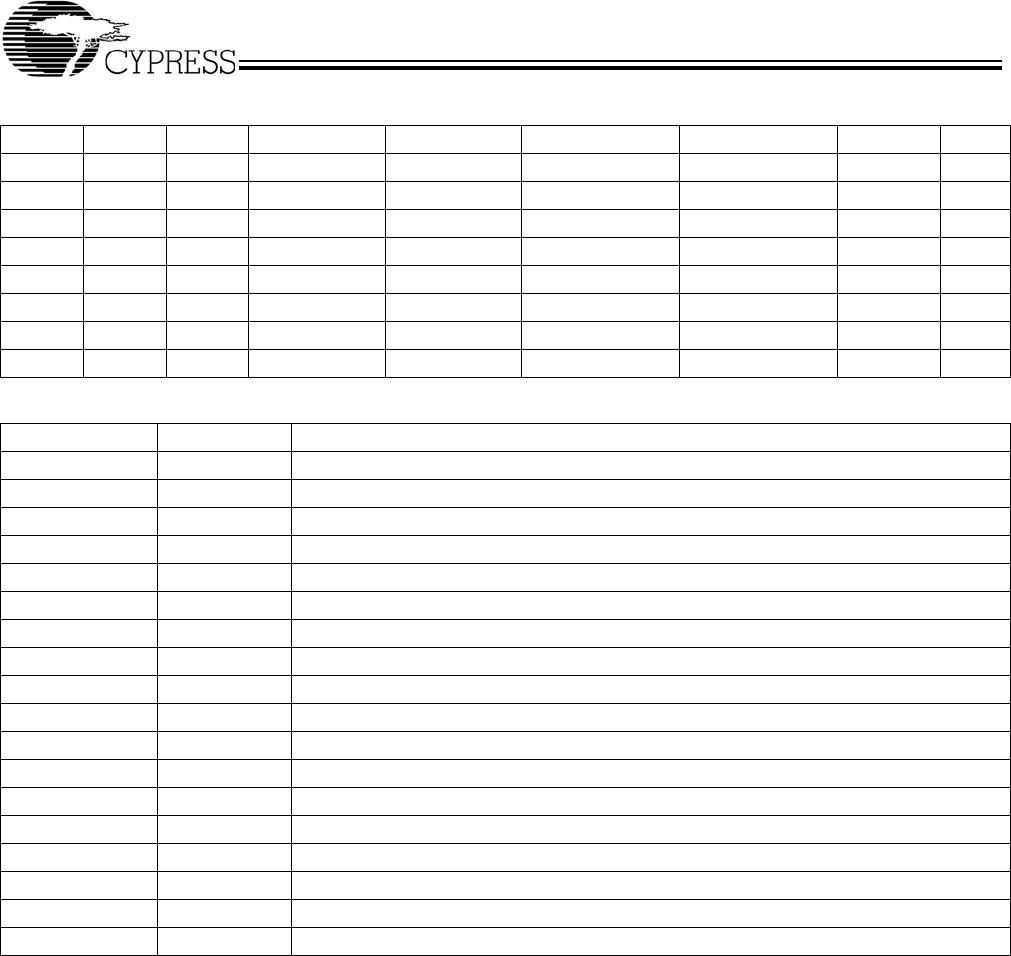

Frequency Select Options

FS2 FS1 FS0 CLK1 (-1,-2) CLK1 (-3,-4) CLK2 CLK3 (-2, -3,-4) REFCLK Units

0 0 0 81 81 27 (CLK1/3) 27 (CLK1/3) 27 MHz

0 0 1 81.081 81.081 27.027 (CLK1/3) 27.027 (CLK1/3) 27 MHz

0 1 0 74.175 74.17582 24.725 (CLK1/3) 74.17582 (CLK1) 27 MHz

0 1 1 74.250 74.25 24.75 (CLK1/3) 74.25 (CLK1) 27 MHz

1 0 0 81 81 27 27 (CLK1/3) 27 MHz

1 0 1 81.081 81.081 27 27.027 (CLK1/3) 27 MHz

1 1 0 74.175 74.1758 27 74.175 (CLK1) 27 MHz

1 1 1 74.250 74.25 27 74.25 (CLK1) 27 MHz

Pin Description

Name Pin Number Description

XIN 1 Reference Crystal Input.

V

DD

2 Voltage Supply.

AV

DD

3 Analog Voltage Supply.

OE 4 Output Enable, weak internal pull-up. 0 = outputs off, 1 = outputs on.

AV

SS

5 Analog Ground.

V

SSL

6 VDDL Ground.

CLK1 (-1,-2) 7 81-/81.081-/74.175-/74.250-MHz Clock Output (frequency selectable).

CLK1 (-3,-4) 7 81-/81.081-/74.17582-/74.25-MHz Clock Output (frequency selectable).

CLK2 8 27-/27.027-/24.725-/24.75-MHz Clock Output (frequency selectable).

REFCLK 9 Reference Clock Output.

FS0 10 Frequency Select 0, weak internal pull-up.

V

DDL

11 Voltage Supply.

N/C (-1) 12 No Connect.

CLK3 (-2,-3,-4) 12 27-/27.027-/74.175-/74.25-MHz Clock Output (frequency selectable).

VSS 13 Ground.

FS1 14 Frequency Select 1, weak internal pull-up.

FS2 15 Frequency Select 2, weak internal pull-up.

XOUT 16 Reference Crystal Output.

[+] Feedback