Package Information

www.vishay.com

Vishay Siliconix

Revision: 09-May-16

1

Document Number: 64694

For technical questions, contact: analogswitchtechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

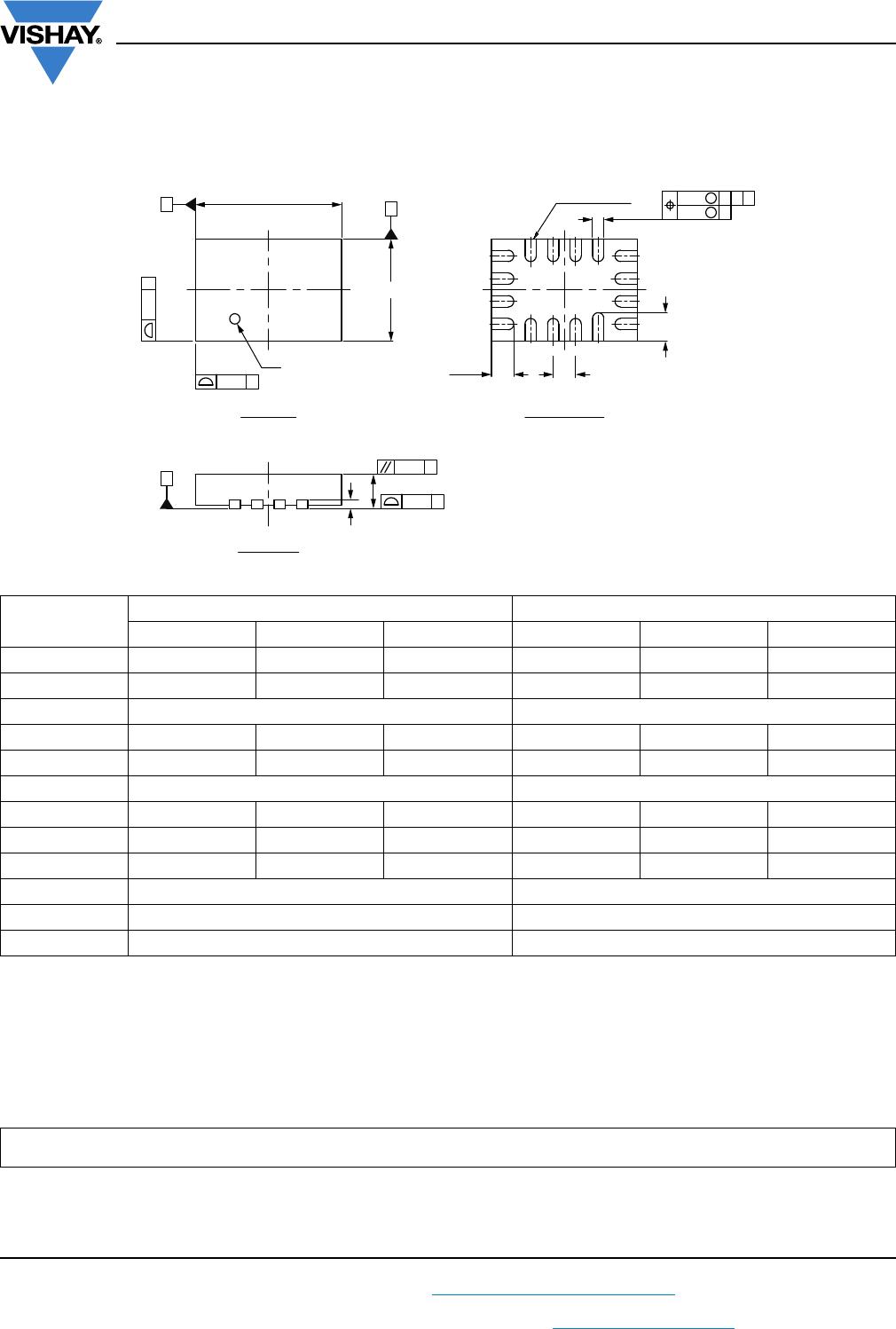

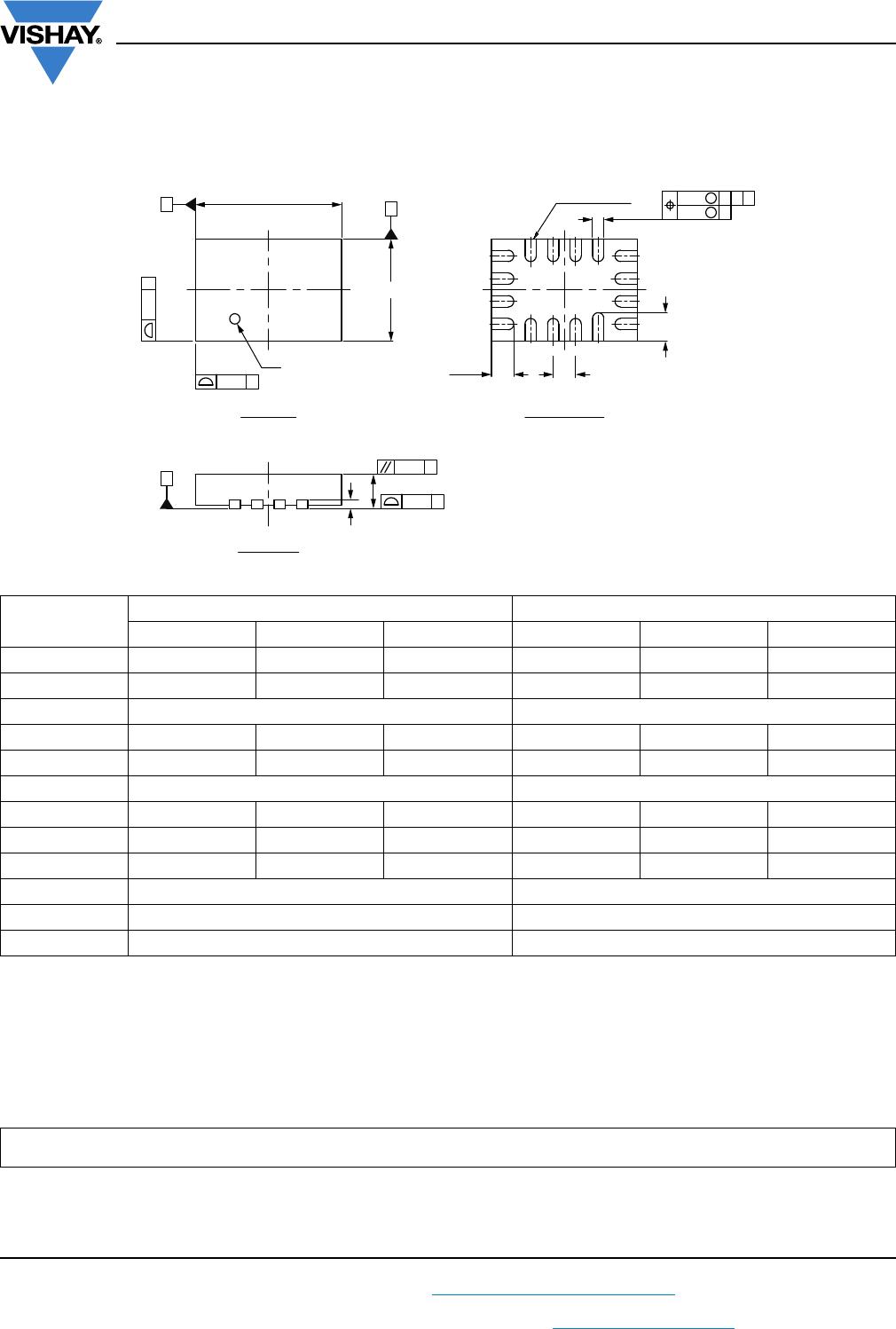

Thin miniQFN16 Case Outline

Notes

(1)

Use millimeters as the primary measurement.

(2)

Dimensioning and tolerances conform to ASME Y14.5M. - 1994.

(3)

N is the number of terminals. Nd and Ne is the number of terminals in each D and E site respectively.

(4)

Dimensions b applies to plated terminal and is measured between 0.15 mm and 0.30 mm from terminal tip.

(5)

The pin 1 identifier must be existed on the top surface of the package by using identification mark or other feature of package body.

(6)

Package warpage max. 0.05 mm.

DIMENSIONS

MILLIMETERS

(1)

INCHES

MIN. NOM. MAX. MIN. NOM. MAX.

A 0.50 0.55 0.60 0.020 0.022 0.024

A1 0 - 0.05 0 - 0.002

A3 0.15 ref. 0.006 ref.

b 0.15 0.20 0.25 0.006 0.008 0.010

D 2.50 2.60 2.70 0.098 0.102 0.106

e 0.40 BSC 0.016 BSC

E1.70

1.80 1.90

0.067

0.071 0.075

L 0.35 0.40 0.45 0.014 0.016 0.018

L1 0.45 0.50 0.55 0.018 0.020 0.022

N

(3)

16 16

Nd

(3)

44

Ne

(3)

44

ECN: T16-0226-Rev. B, 09-May-16

DWG: 6023

0.10 C

0.10

A

A3

C

0.10 C

0.10 C

Side view

Top view Bottom view

C

A

B

13

12 11 10

D

E

9

8

7

6

5

8

7

6

5

13

14

15

16

L1

1234

Pin #1 identier

(5)

Seating

plane

Terminal tip

(4)

16 x b

0.10

0.05

C

C

M

M

AB

1211109

4

15 x L

321

e

14

15

16