AD976/AD976A

–11–

REV. C

VOLTAGE REFERENCE

The AD976/AD976A has an on-chip temperature compensated

bandgap voltage reference that is factory trimmed to 2.5 V

± 20 mV. The full-scale range of the ADC is equal to ±4V

REF

.

Thus, the nominal range will be ±10 V.

The accuracy of the AD976 over the specified temperature

range is dominated by the drift performance of the voltage refer-

ence. The on-chip voltage reference is laser-trimmed to provide

a typical drift of 7 ppm/°C. This typical drift characteristic is

shown in Figure 13, which is a plot of the change in reference

voltage (in mV) versus the change in temperature—notice the

plot is normalized for zero error at +25°C. If improved drift

performance is required, an external reference such as the

AD780 should be used to provide a drift as low as 3 ppm/°C. In

order to simplify the drive requirements of the voltage reference

(internal or external), an onboard reference buffer is provided.

The output of this buffer is provided at the CAP pin and is

available to the user; however, when externally loading the refer-

ence buffer, it is important to make sure that proper precautions

are taken to minimize any degradation in the ADC’s perfor-

mance. Figure 14 shows the load regulation of the reference

buffer. Notice that this figure is also normalized so that there is

zero error with no dc load. In the linear region, the output im-

pedance at this point is typically 1 ohm. Because of this 1 ohm

output impedance, it is important to minimize any ac or input

dependent loads that will lead to increased distortion. Any dc

loads will simply act as a gain error. Although the typical char-

acteristic of Figure 14 shows that the AD976 is capable of driv-

ing loads greater than 15 mA, it is not recommended that the

steady state current exceed 2 mA.

In addition to the on-chip reference, an external 2.5 V reference

can be applied. When choosing an external reference for a

16-bit application, however, careful attention should be paid to

noise and temperature drift. These critical specifications can

have a significant effect on the ADC performance.

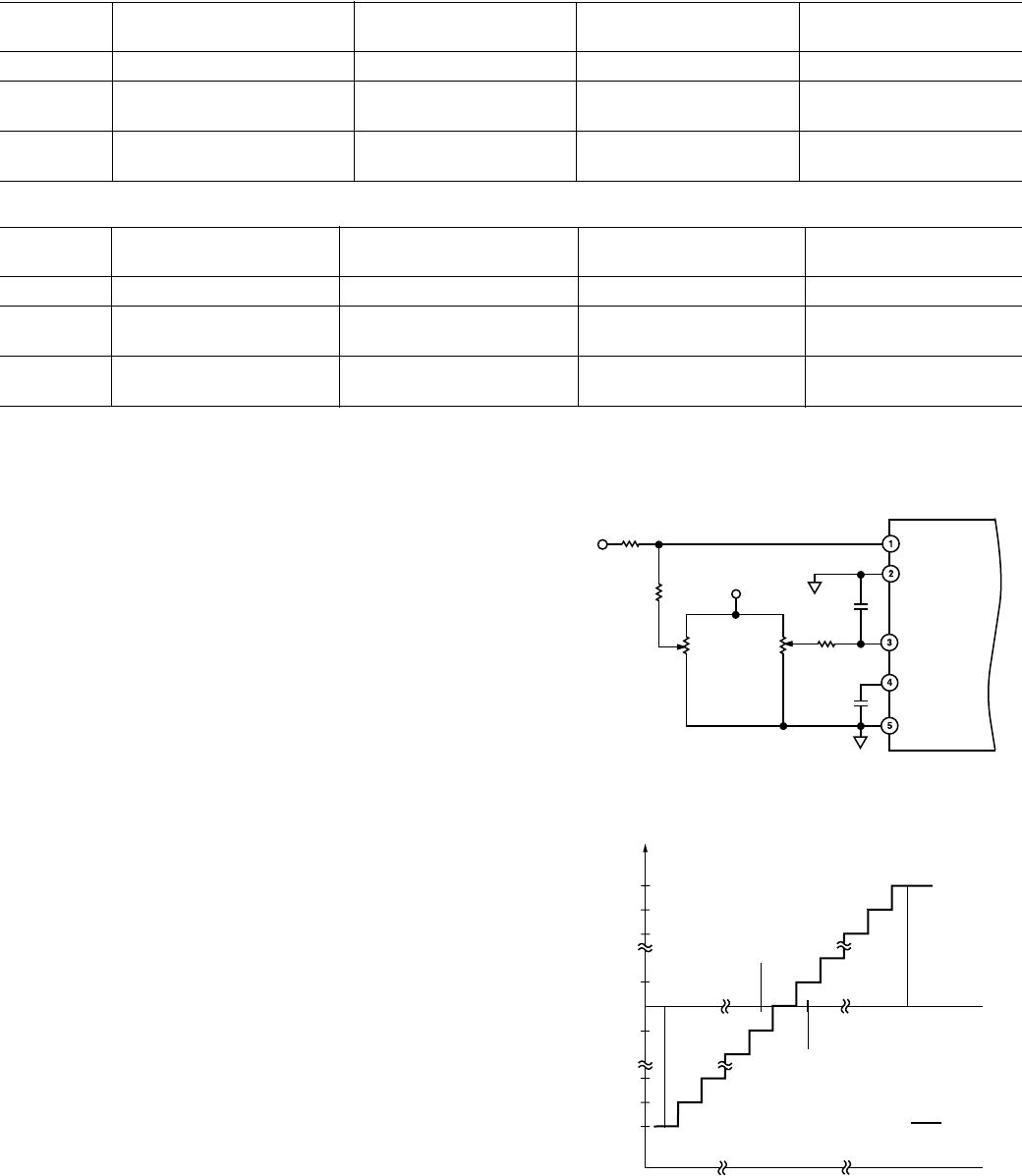

Figure 9 shows the AD976/AD976A with the AD780 voltage

reference applied to the REF pin. The AD780 is a bandgap

reference that exhibits ultralow drift, low initial error, and low

output noise. For low power applications, the REF192 provides

a low quiescent current, high accuracy and low temperature

drift solution.

C4

0.1mF

V

ANA

C3

1mF

V

IN

AGND1

REF

CAP

AGND2

610V INPUT

R2

33.2kV

C2

2.2mF

AD976/

AD976A

R1

200V

C1

2.2mF

AD780

GND

V

OUT

TEMP

V

IN

0.1mF

+5V

Figure 9. AD780 External Reference Connection to the

AD976/AD976A

AC PERFORMANCE

The AD976/AD976A is fully specified and tested for dynamic

performance specifications. The ac parameters are required for

signal processing applications such as speech recognition and

spectrum analysis. These applications require information on

the ADC’s effect on the spectral content of the input signal.

Hence, the parameters for which the AD976/AD976A is

specified include: S/(N+D), THD and Spurious Free Dynamic

Range. These terms are discussed in greater detail in the follow-

ing sections.

As a general rule, it is recommended that the results from sev-

eral conversions be averaged to reduce the effects of noise, thus

improving parameters such as S/(N+D) and THD. The ac per-

formance of the AD976/AD976A can be optimized by operating

the ADC at its maximum sampling rate of 100 kHz/200 kHz

and by digitally filtering the resulting bit stream to the desired

signal bandwidth. By distributing noise over a wider frequency

range, the noise density in the frequency band of interest can be

reduced. For example, if the required input bandwidth is 50 kHz,

the AD976A could be oversampled by a factor of 2. This would

yield a 3 dB improvement in the effective SNR performance.

FREQUENCY – kHz

0

–10

–150

0 10010 20 30 40

–40

–70

–130

–140

–20

–30

–60

–50

dB

–90

–120

–80

–110

–100

50 60 70 80 90 955 1525354555657585

F

SAMPLE

= 200kHz

F

IN

= 45kHz

SNR = 86.23dB

THD = –105.33dB

100%

Figure 10. FFT PLOT

DC PERFORMANCE

The factory calibration scheme used for the AD976/AD976A

compensates for bit weight errors that may exist in the capacitor

array. The mismatch in capacitor values is adjusted (using the

calibration coefficients) during a conversion, resulting in excellent

dc linearity performance. Figures 11, 12, 15, 16, 17 and 18,

respectively, show typical INL, typical DNL, typical positive and

negative INL and DNL distribution plots for the AD976/AD976A

at +25°C.

A histogram test is a statistical method for deriving an A/D

converter’s differential nonlinearity. A ramp input is sampled

by the ADC and a large number of conversions are taken and

stored. Theoretically, the codes would all be the same size and

therefore have an equal number of occurrences. A code with an

average number of occurrences would have a DNL of “0.” A

code that is different than the average would have a DNL that

was either greater or less than zero LSB. A DNL of –1 LSB

indicates that there is a missing code present at the 16-bit level

and that the ADC exhibits 15-bit performance.