MAX3747A/MAX3747B

155Mbps to 3.2Gbps, Low-Power SFP

Limiting Amplifiers

9

Maxim Integrated

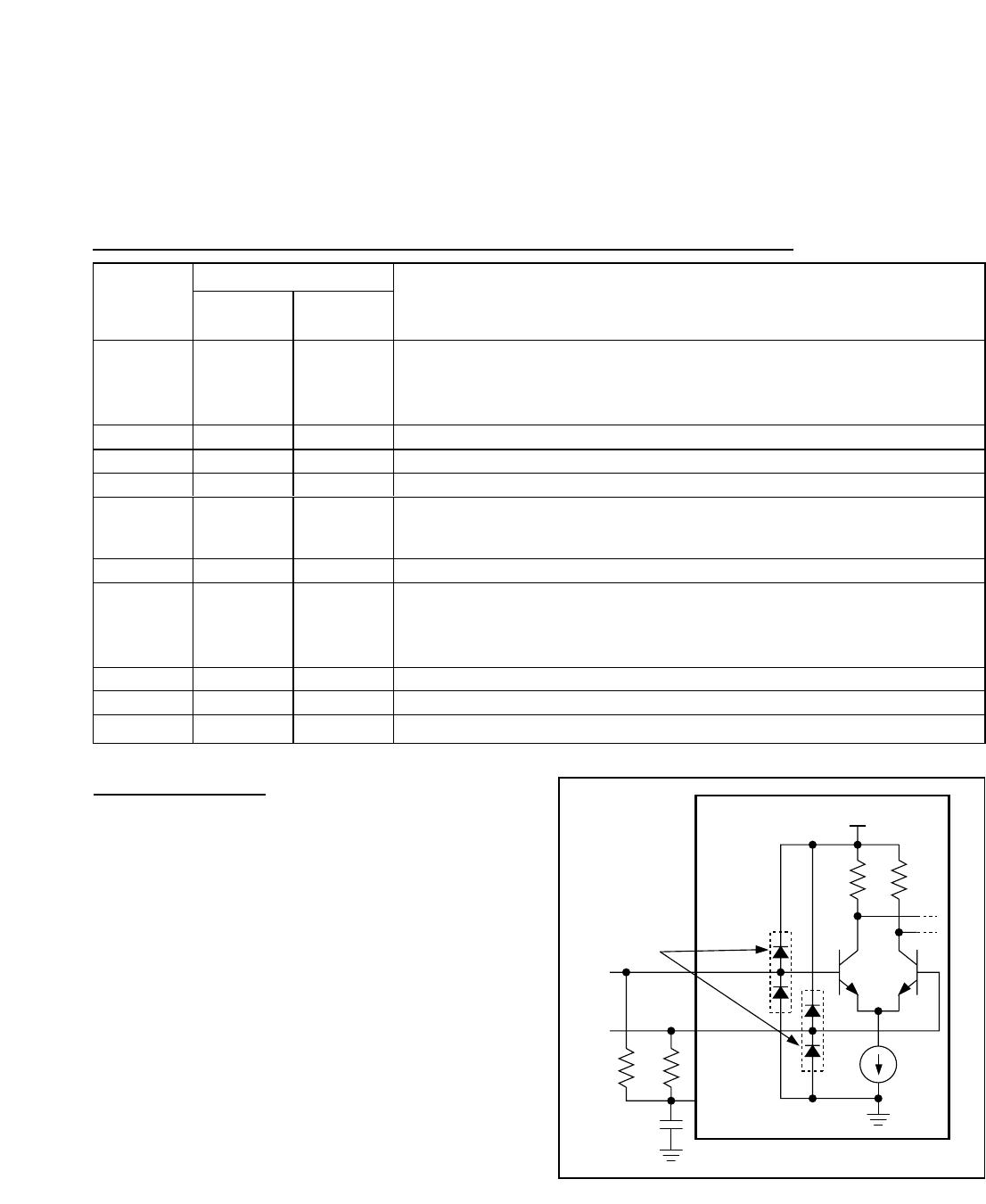

Loss-of-Signal Indicator

The MAX3747A/MAX3747B are equipped with LOS cir-

cuitry that indicates when the input signal is below a pro-

grammable threshold, set by a voltage on the TH pin

(see the

Typical Operating Characteristics

). The voltage

on the TH pin is set by two resistors, one connecting

from the TH pin to V

CC

and the other connecting from TH

to V

REF

(Figure 5). An RMS power detector compares

the input signal amplitude with this threshold and feeds

the signal-detect information to the LOS output, which is

open collector. To prevent LOS chatter in the region of

the programmed threshold, approximately 2dB of hys-

teresis is built into the LOS assert/deassert function.

Once asserted, LOS is not deasserted until the input

amplitude rises to the required level. Figure 6 shows the

LOS output circuit.

Applications Information

Program the LOS Assert Threshold

Program the LOS assert threshold according to Figure

5. The combination of R

TH1

and R

TH2

should be

greater than or equal to 5kΩ, see the Assert/Deassert

vs. V

TH

graph in the

Typical Operating Characteristics

.

Select the Coupling Capacitor

When AC-coupling is desired, coupling capacitors C

IN

and C

OUT

should be selected to minimize the receiv-

er’s deterministic jitter. Jitter is decreased as the input

low-frequency cutoff (f

IN

) is decreased:

f

IN

= 1/[2π(50)(C

IN

)]

For all applications, the recommended value for C

IN

and C

OUT

is 0.1µF, which provides f

IN

equal to 32kHz.

Refer to Application Note HFAN-1.1:

Choosing AC-

Coupling Capacitors

on the Maxim website

(www.maximintegrated.com)

.