PCA9538 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 8 — 8 November 2017 8 of 34

NXP Semiconductors

PCA9538

8-bit I

2

C-bus and SMBus low power I/O port with interrupt and reset

6.2.5 Register 3 - Configuration register

This register configures the directions of the I/O pins. If a bit in this register is set, the

corresponding port pin is enabled as an input with high-impedance output driver. If a bit in

this register is cleared, the corresponding port pin is enabled as an output. At reset, the

I/Os are configured as inputs.

6.3 Power-on reset

When power is applied to V

DD

, an internal Power-On Reset (POR) holds the PCA9538 in

a reset condition until V

DD

has reached V

POR

. At that point, the reset condition is released

and the PCA9538 registers and state machine will initialize to their default states.

Thereafter, V

DD

must be lowered below 0.2 V to reset the device.

For a power reset cycle, V

DD

must be lowered below 0.2 V and then restored to the

operating voltage.

6.4 RESET input

A reset can be accomplished by holding the RESET pin LOW for a minimum of t

w(rst)

.

The PCA9538 registers and SMBus/I

2

C-bus state machine will be held in their default

state until the RESET

input is once again HIGH. This input requires a pull-up resistor to

V

DD

if no active connection is used.

6.5 Interrupt output

The open-drain interrupt output (INT) is activated when one of the port pins changes state

and the pin is configured as an input. The interrupt is de-activated when the input returns

to its previous state or the Input Port register is read.

Note that changing an I/O from an output to an input may cause a false interrupt to occur

if the state of the pin does not match the contents of the Input Port register.

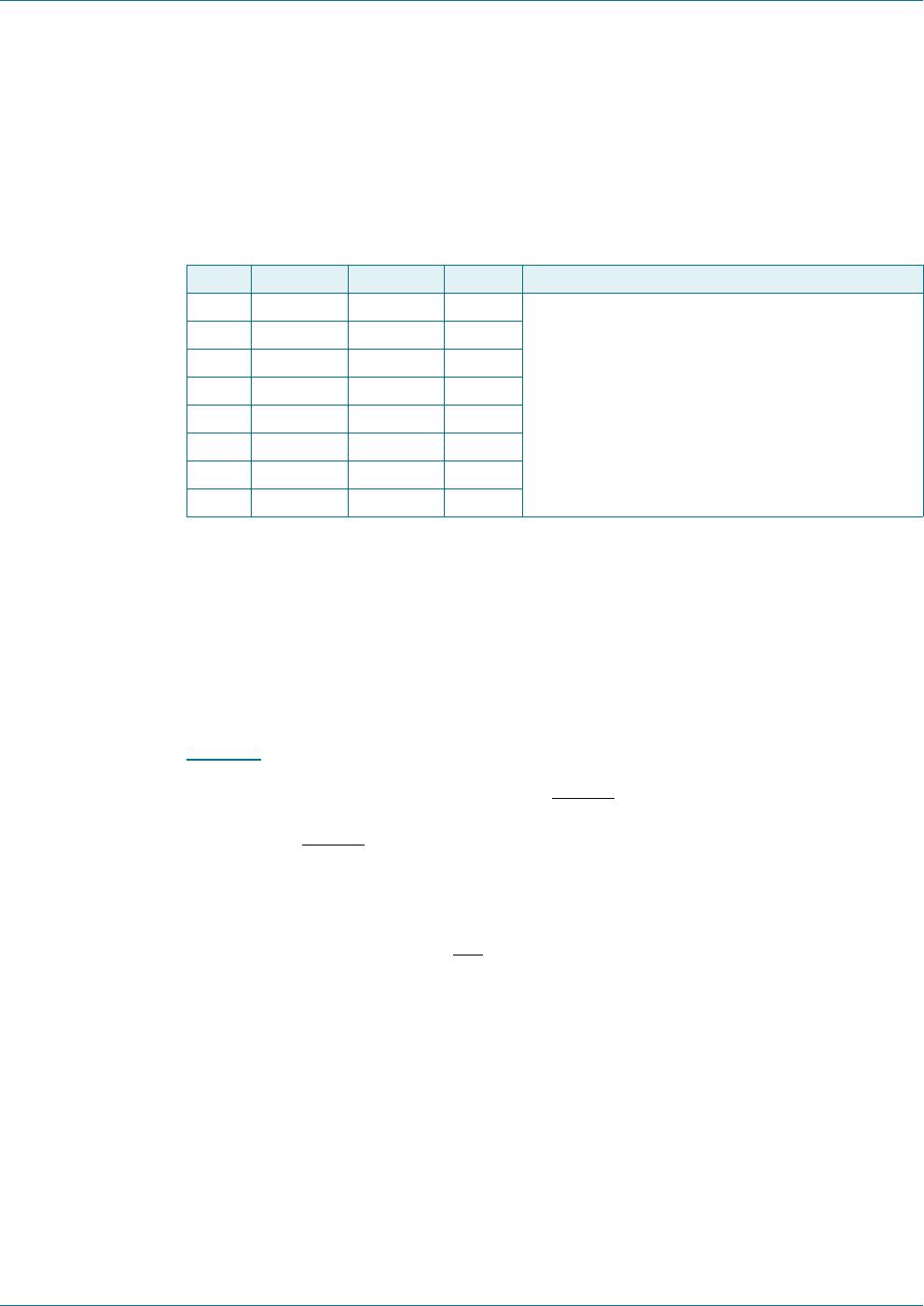

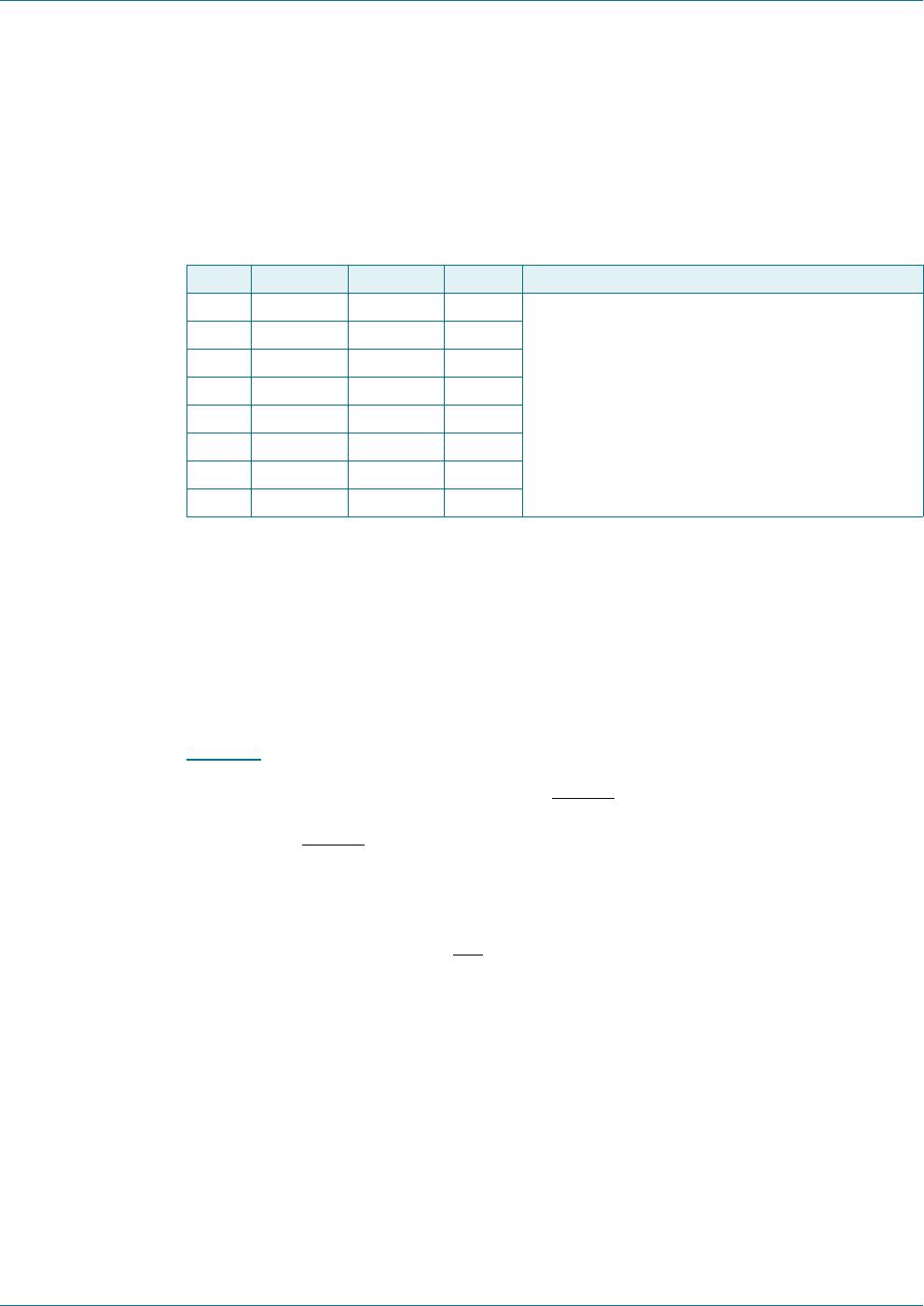

Table 8. Register 3 - Configuration register bit description

Legend: * default value.

Bit Symbol Access Value Description

7 C7 R/W 1* configures the directions of the I/O pins

0 = corresponding port pin enabled as an output

1 = corresponding port pin configured as an input

(default value)

6C6 R/W 1*

5C5 R/W 1*

4C4 R/W 1*

3C3 R/W 1*

2C2 R/W 1*

1C1 R/W 1*

0C0 R/W 1*