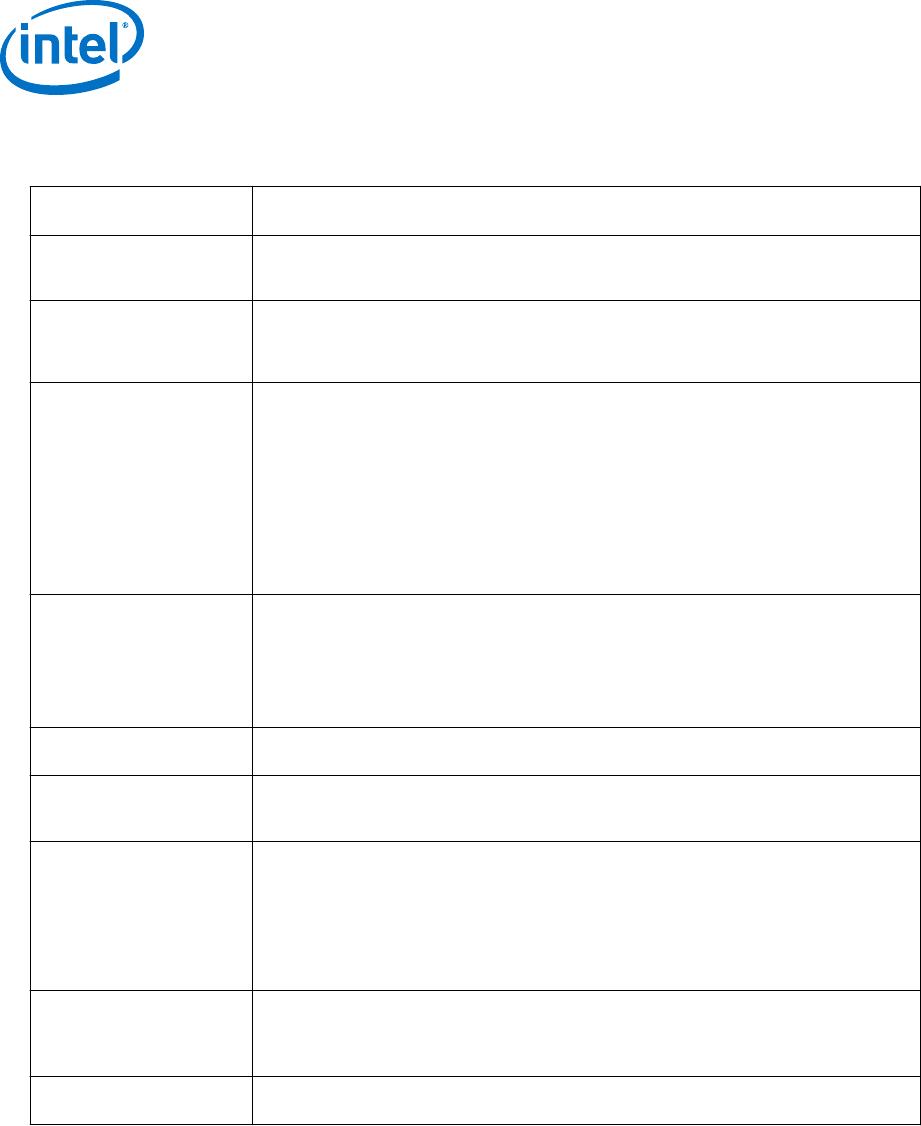

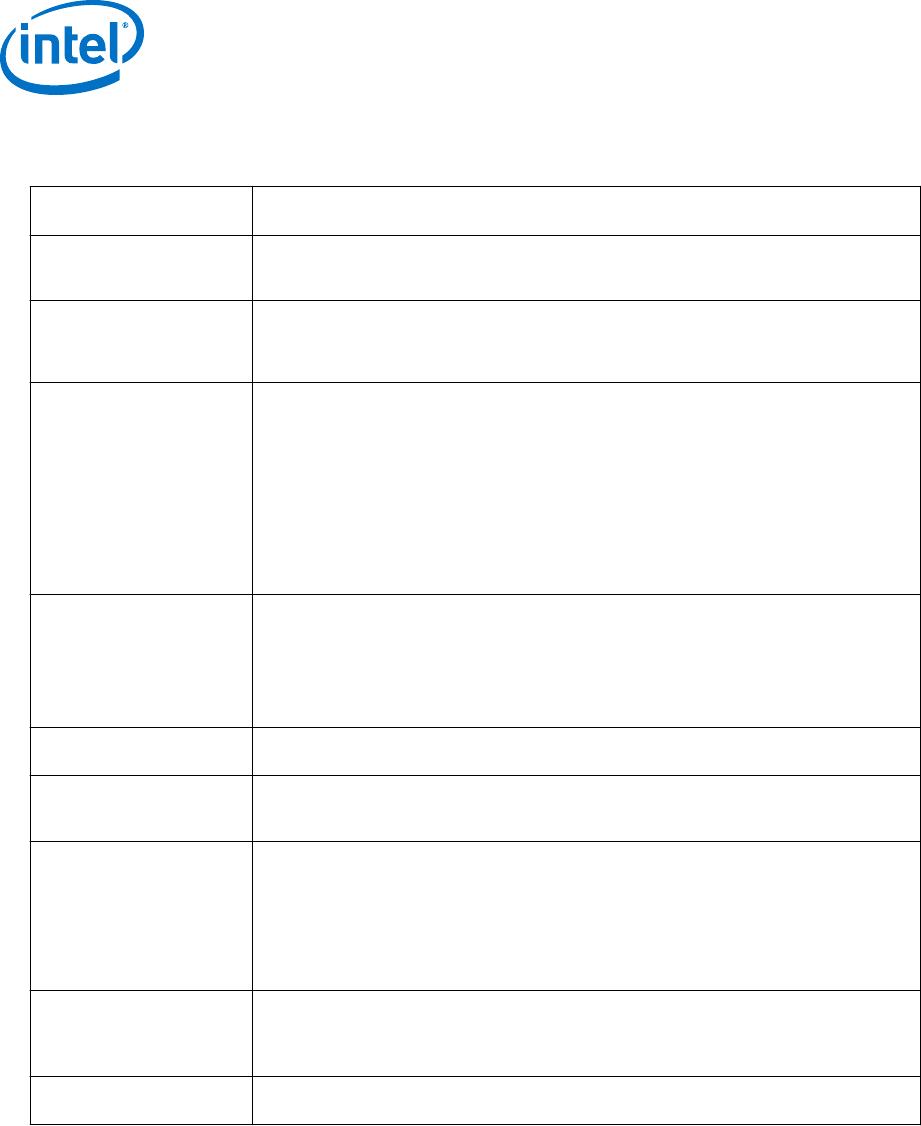

Table 24. Improvements in 20 nm HPS

This table lists the key improvements of the 20 nm HPS compared to the 28 nm HPS.

Advantages/

Improvements

Description

Increased performance and

overdrive capability

While the nominal processor frequency is 1.2 GHz, the 20 nm HPS offers an “overdrive”

feature which enables a higher processor operating frequency. This requires a higher supply

voltage value that is unique to the HPS and may require a separate regulator.

Increased processor memory

bandwidth and DDR4

support

Up to 64-bit DDR4 memory at 2,400 Mbps support is available for the processor. The hard

memory controller for the HPS comprises a multi-port front end that manages connections

to a single port memory controller. The multi-port front end allows logic core and the HPS

to share ports and thereby the available bandwidth of the memory controller.

Flexible I/O sharing An advanced I/O pin muxing scheme allows improved sharing of I/O between the HPS and

the core logic. The following types of I/O are available for SoC:

• 17 dedicated I/Os—physically located inside the HPS block and are not accessible to

logic within the core. The 17 dedicated I/Os are used for HPS clock, resets, and

interfacing with boot devices, QSPI, and SD/MMC.

• 48 direct shared I/O—located closest to the HPS block and are ideal for high speed HPS

peripherals such as EMAC, USB, and others. There is one bank of 48 I/Os that supports

direct sharing where the 48 I/Os can be shared 12 I/Os at a time.

• Standard (shared) I/O—all standard I/Os can be shared by the HPS peripherals and any

logic within the core. For designs where more than 48 I/Os are required to fully use all

the peripherals in the HPS, these I/Os can be connected through the core logic.

EMAC core Three EMAC cores are available in the HPS. The EMAC cores enable an application to

support two redundant Ethernet connections; for example, backplane, or two EMAC cores

for managing IEEE 1588 time stamp information while allowing a third EMAC core for debug

and configuration. All three EMACs can potentially share the same time stamps, simplifying

the 1588 time stamping implementation. A new serial time stamp interface allows core

logic to access and read the time stamp values. The integrated EMAC controllers can be

connected to external Ethernet PHY through the provided MDIO or I

2

C interface.

On-chip memory The on-chip memory is updated to 256 KB support and can support larger data sets and

real time algorithms.

ECC enhancements Improvements in L2 Cache ECC management allow identification of errors down to the

address level. ECC enhancements also enable improved error injection and status reporting

via the introduction of new memory mapped access to syndrome and data signals.

HPS to FPGA Interconnect

Backbone

Although the HPS and the Logic Core can operate independently, they are tightly coupled

via a high-bandwidth system interconnect built from high-performance ARM AMBA AXI bus

bridges. IP bus masters in the FPGA fabric have access to HPS bus slaves via the FPGA-to-

HPS interconnect. Similarly, HPS bus masters have access to bus slaves in the core fabric

via the HPS-to-FPGA bridge. Both bridges are AMBA AXI-3 compliant and support

simultaneous read and write transactions. Up to three masters within the core fabric can

share the HPS SDRAM controller with the processor. Additionally, the processor can be used

to configure the core fabric under program control via a dedicated 32-bit configuration port.

FPGA configuration and HPS

booting

The FPGA fabric and HPS in the SoCs are powered independently. You can reduce the clock

frequencies or gate the clocks to reduce dynamic power.

You can configure the FPGA fabric and boot the HPS independently, in any order, providing

you with more design flexibility.

Security New security features have been introduced for anti-tamper management, secure boot,

encryption (AES), and authentication (SHA).

Intel

®

Arria

®

10 Device Overview

A10-OVERVIEW | 2018.04.09

Intel

®

Arria

®

10 Device Overview

34