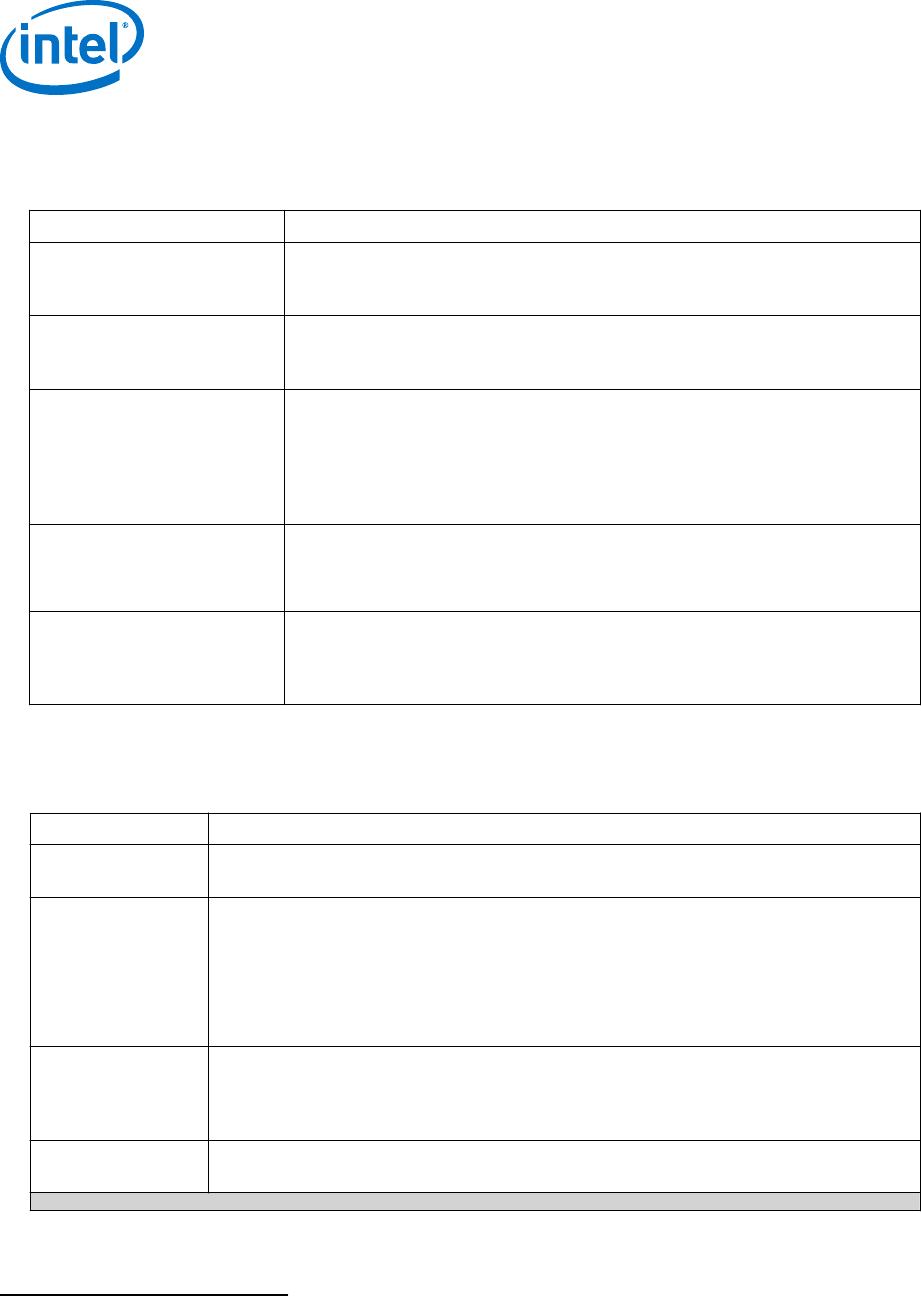

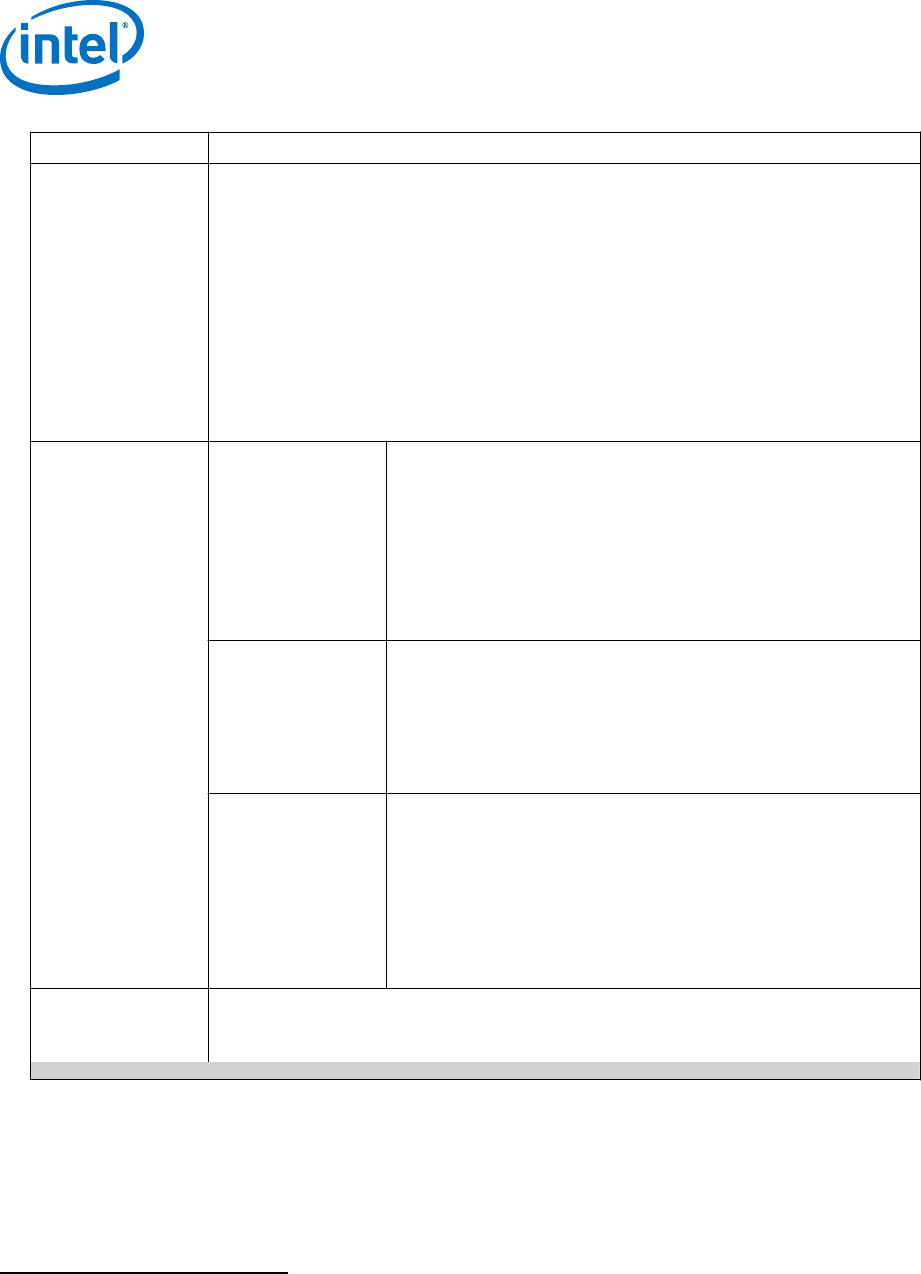

Feature Description

Embedded Hard IP

blocks

Variable-precision DSP • Native support for signal processing precision levels from 18 x 19 to

54 x 54

• Native support for 27 x 27 multiplier mode

• 64-bit accumulator and cascade for systolic finite impulse responses

(FIRs)

• Internal coefficient memory banks

• Preadder/subtractor for improved efficiency

• Additional pipeline register to increase performance and reduce

power

• Supports floating point arithmetic:

— Perform multiplication, addition, subtraction, multiply-add,

multiply-subtract, and complex multiplication.

— Supports multiplication with accumulation capability, cascade

summation, and cascade subtraction capability.

— Dynamic accumulator reset control.

— Support direct vector dot and complex multiplication chaining

multiply floating point DSP blocks.

Memory controller DDR4, DDR3, and DDR3L

PCI Express* PCI Express (PCIe*) Gen3 (x1, x2, x4, or x8), Gen2 (x1, x2, x4, or x8)

and Gen1 (x1, x2, x4, or x8) hard IP with complete protocol stack,

endpoint, and root port

Transceiver I/O • 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC)

• PCS hard IPs that support:

— 10-Gbps Ethernet (10GbE)

— PCIe PIPE interface

— Interlaken

— Gbps Ethernet (GbE)

— Common Public Radio Interface (CPRI) with deterministic latency

support

— Gigabit-capable passive optical network (GPON) with fast lock-

time support

• 13.5G JESD204b

• 8B/10B, 64B/66B, 64B/67B encoders and decoders

• Custom mode support for proprietary protocols

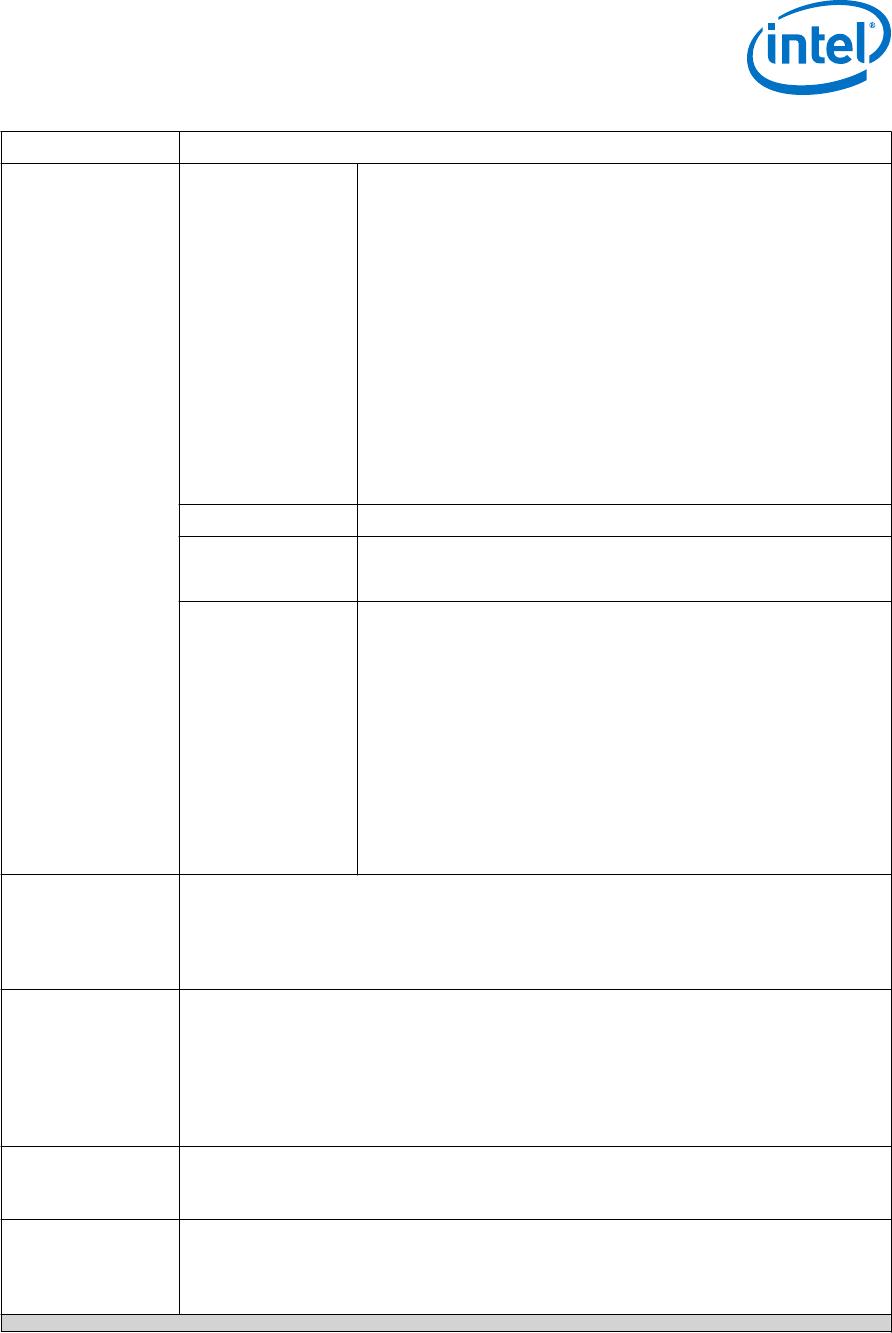

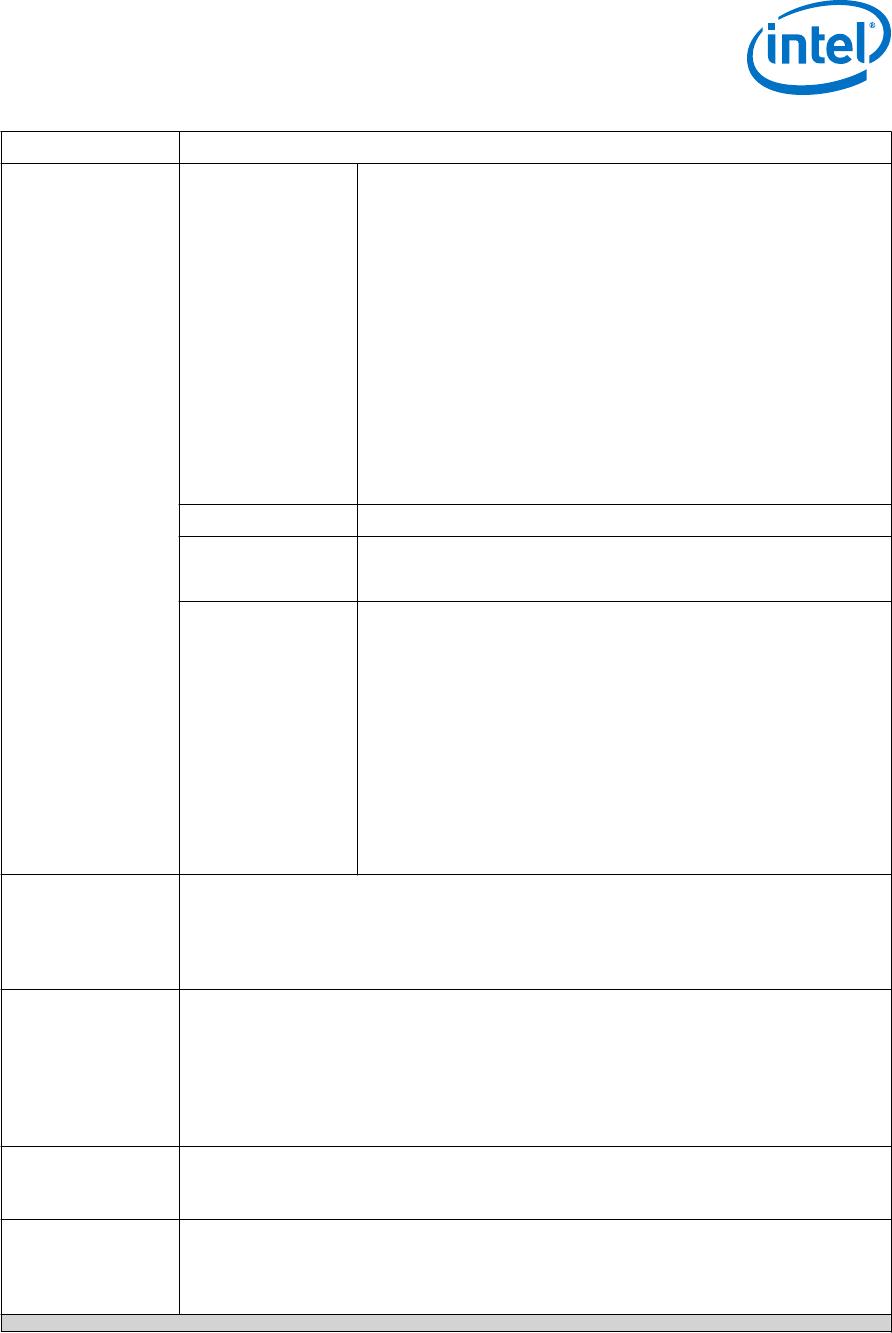

Core clock networks • Up to 800 MHz fabric clocking, depending on the application:

— 667 MHz external memory interface clocking with 2,400 Mbps DDR4 interface

— 800 MHz LVDS interface clocking with 1,600 Mbps LVDS interface

• Global, regional, and peripheral clock networks

• Clock networks that are not used can be gated to reduce dynamic power

Phase-locked loops

(PLLs)

• High-resolution fractional synthesis PLLs:

— Precision clock synthesis, clock delay compensation, and zero delay buffering (ZDB)

— Support integer mode and fractional mode

— Fractional mode support with third-order delta-sigma modulation

• Integer PLLs:

— Adjacent to general purpose I/Os

— Support external memory and LVDS interfaces

FPGA General-purpose

I/Os (GPIOs)

• 1.6 Gbps LVDS—every pair can be configured as receiver or transmitter

• On-chip termination (OCT)

• 1.2 V to 3.0 V single-ended LVTTL/LVCMOS interfacing

External Memory

Interface

• Hard memory controller— DDR4, DDR3, and DDR3L support

— DDR4—speeds up to 1,200 MHz/2,400 Mbps

— DDR3—speeds up to 1,067 MHz/2,133 Mbps

• Soft memory controller—provides support for RLDRAM 3

(2)

, QDR IV

(2)

, and QDR II+

continued...

Intel

®

Arria

®

10 Device Overview

A10-OVERVIEW | 2018.04.09

Intel

®

Arria

®

10 Device Overview

5