LM75A_4 © NXP B.V. 2007. All rights reserved.

Product data sheet Rev. 04 — 10 July 2007 4 of 24

NXP Semiconductors

LM75A

Digital temperature sensor and thermal watchdog

7. Functional description

7.1 General operation

The LM75A uses the on-chip band gap sensor to measure the device temperature with

the resolution of 0.125 °C and stores the 11-bit 2's complement digital data, resulted from

11-bit A-to-D conversion, into the device Temp register. This Temp register can be read at

any time by a controller on the I

2

C-bus. Reading temperature data does not affect the

conversion in progress during the read operation.

The device can be set to operate in either mode: normal or shutdown. In normal operation

mode, the temp-to-digital conversion is executed every 100 ms and the Temp register is

updated at the end of each conversion. In shutdown mode, the device becomes idle, data

conversion is disabled and the Temp register holds the latest result; however, the device

I

2

C-bus interface is still active and register write/read operation can be performed. The

device operation mode is controllable by programming bit B0 of the configuration register.

The temperature conversion is initiated when the device is powered-up or put back into

normal mode from shutdown.

In addition, at the end of each conversion in normal mode, the temperature data (or Temp)

in the Temp register is automatically compared with the overtemperature shutdown

threshold data (or Tos) stored in the Tos register, and the hysteresis data (or Thyst) stored

in the Thyst register, in order to set the state of the device OS output accordingly. The

device Tos and Thyst registers are write/read capable, and both operate with 9-bit

2's complement digital data. To match with this 9-bit operation, the Temp register uses

only the 9 MSB bits of its 11-bit data for the comparison.

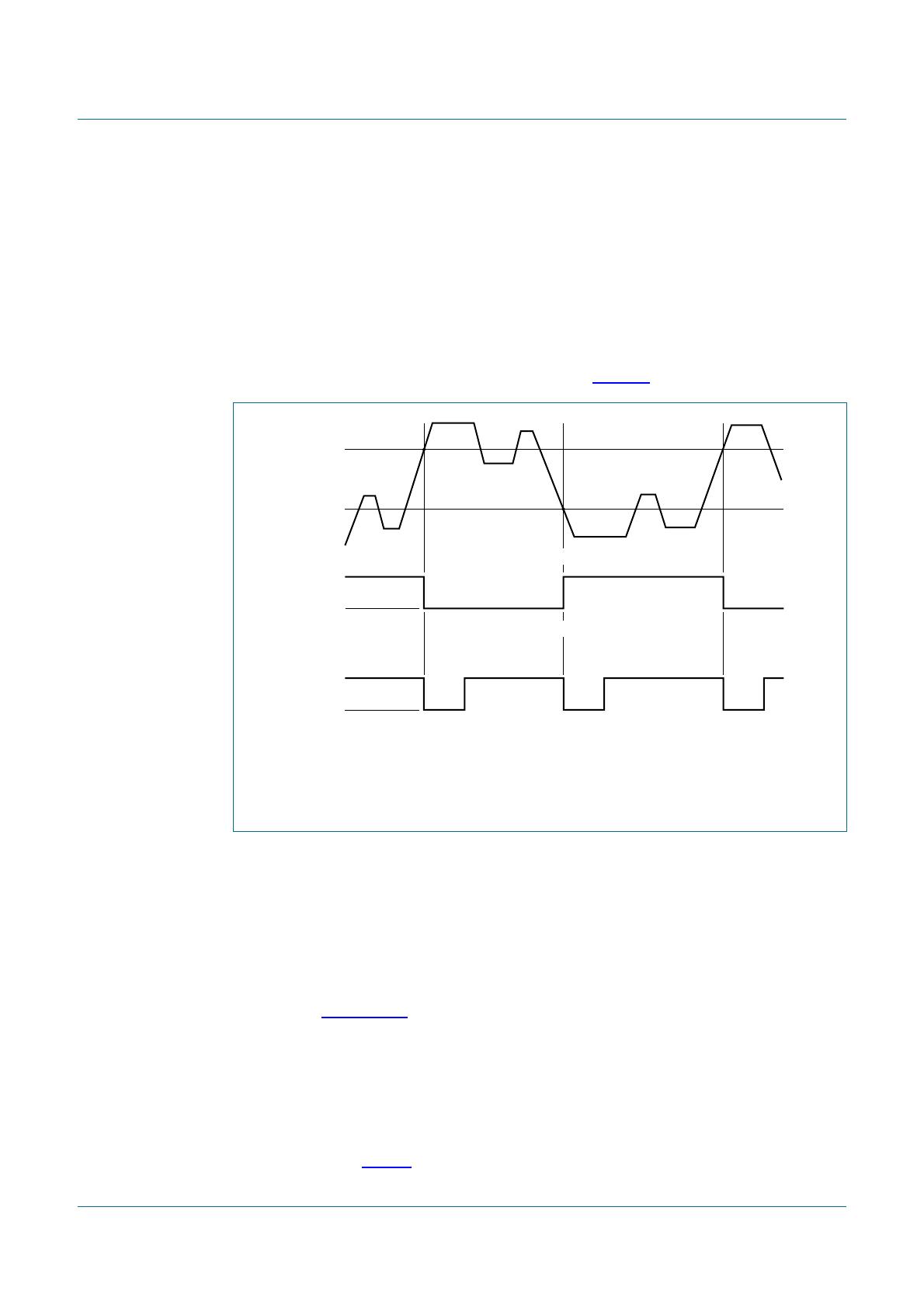

The way that the OS output responds to the comparison operation depends upon the OS

operation mode selected by configuration bit B1, and the user-defined fault queue defined

by configuration bits B3 and B4.

In OS comparator mode, the OS output behaves like a thermostat. It becomes active

when the Temp exceeds the T

os

, and is reset when the Temp drops below the T

hyst

.

Reading the device registers or putting the device into shutdown does not change the

state of the OS output. The OS output in this case can be used to control cooling fans or

thermal switches.

In OS interrupt mode, the OS output is used for thermal interruption. When the device is

powered-up, the OS output is first activated only when the Temp exceeds the T

os

; then it

remains active indefinitely until being reset by a read of any register. Once the OS output

has been activated by crossing T

os

and then reset, it can be activated again only when the

Temp drops below the T

hyst

; then again, it remains active indefinitely until being reset by a

read of any register. The OS interrupt operation would be continued in this sequence:

T

os

trip, Reset, T

hyst

trip, Reset, T

os

trip, Reset, T

hyst

trip, Reset, etc.

A1 6 Digital input. User-defined address bit 1.

A0 7 Digital input. User-defined address bit 0.

V

CC

8 Power supply.

Table 3. Pin description

…continued

Symbol Pin Description