AD5220

–8–

REV. 0

OPERATION

The AD5220 provides a 128-position digitally controlled vari-

able resistor (VR) device. Changing the VR settings is accom-

plished by pulsing the CLK pin while CS is active low. The

direction of the increment is controlled by the U/D (UP/DOWN)

control input pin. When the wiper hits the end of the resistor

(Terminals A or B) additional CLK pulses no longer change

the wiper setting. The wiper position is immediately decoded

by the wiper decode logic changing the wiper resistance. Ap-

propriate debounce circuitry is required when push button

switches are used to control the count sequence and direction

of count. The exact timing requirements are shown in Figure 3.

The AD5220 powers ON in a centered wiper position exhibit-

ing nearly equal resistances of R

WA

and R

WB

.

UP/

DOWN

CNTR

RS

D

E

C

O

D

E

7

40

H

POR

EN

AD5220

V

DD

A

W

B

GND

CLK

CS

U/D

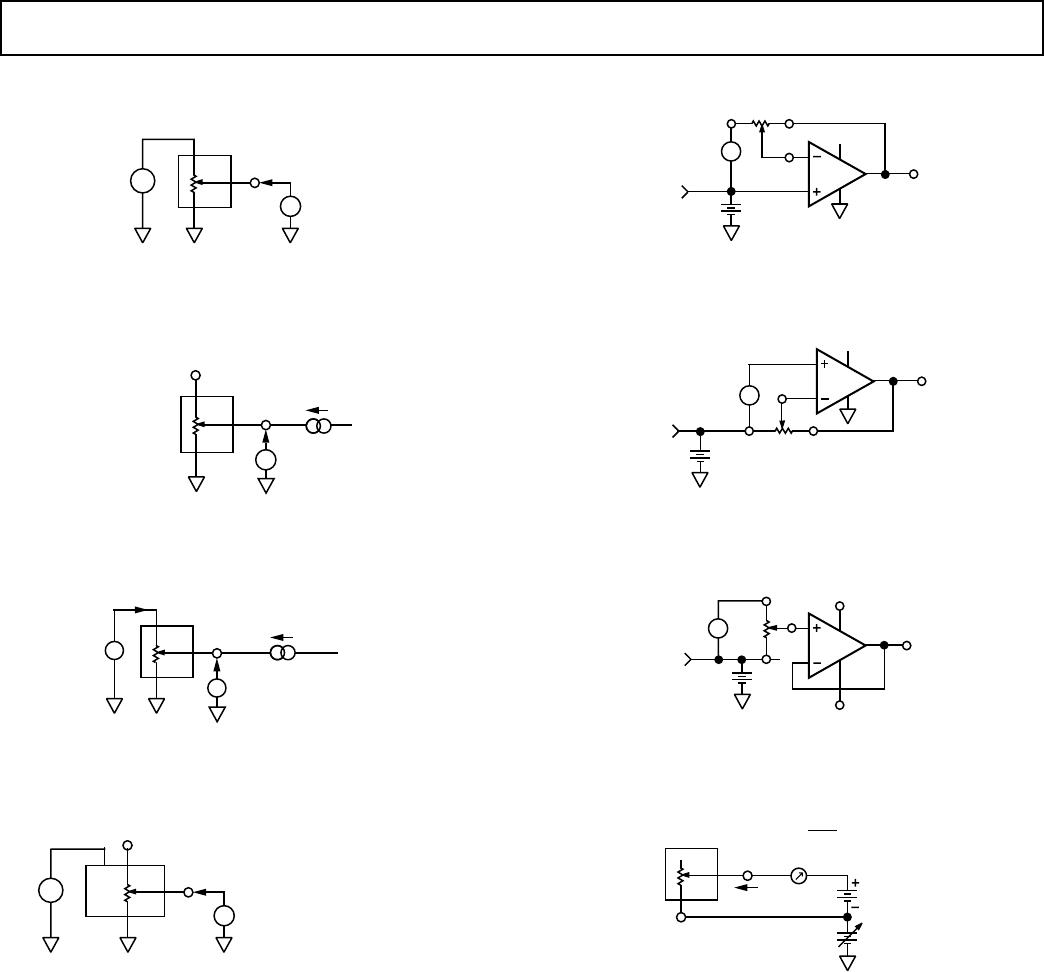

Figure 35. Block Diagram

DIGITAL INTERFACING OPERATION

The AD5220 contains a three-wire serial input interface. The

three inputs are clock (CLK), CS and UP/DOWN (U/D). The

negative-edge sensitive CLK input requires clean transitions to

avoid clocking multiple pulses into the internal UP/DOWN

counter register, see Figure 35. Standard logic families work

well. If mechanical switches are used for product evaluation

they should be debounced by a flip-flop or other suitable

means. When CS is taken active low the clock begins to incre-

ment or decrement the internal UP/DOWN counter dependent

upon the state of the U/D control pin. The UP/DOWN counter

value (D) starts at 40

H

at system power ON. Each new CLK

pulse will increment the value of the internal counter by one

LSB until the full scale value of 3F

H

is reached as long as the

U/D pin is logic high. If the U/D pin is taken to logic low the

counter will count down stopping at code 00

H

(zero-scale).

Additional clock pulses on the CLK pin are ignored when the

wiper is at either the 00

H

position or the 3F

H

position.

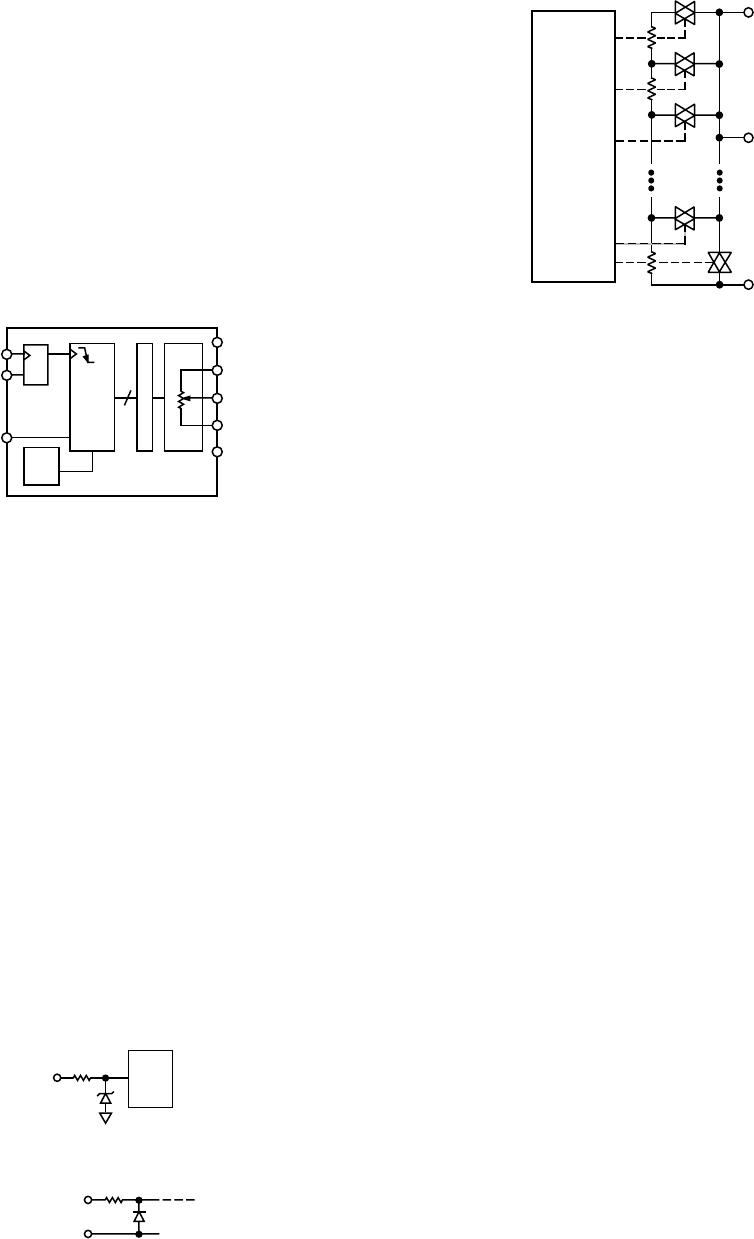

All digital inputs (CS, U/D, CLK) are protected with a series

input resistor and parallel Zener ESD structure shown in

Figure 36.

LOGIC

1kV

Figure 36. Equivalent ESD Protection Digital Pins

20V

A, B, W

GND

Figure 37. Equivalent ESD Protection Analog Pins

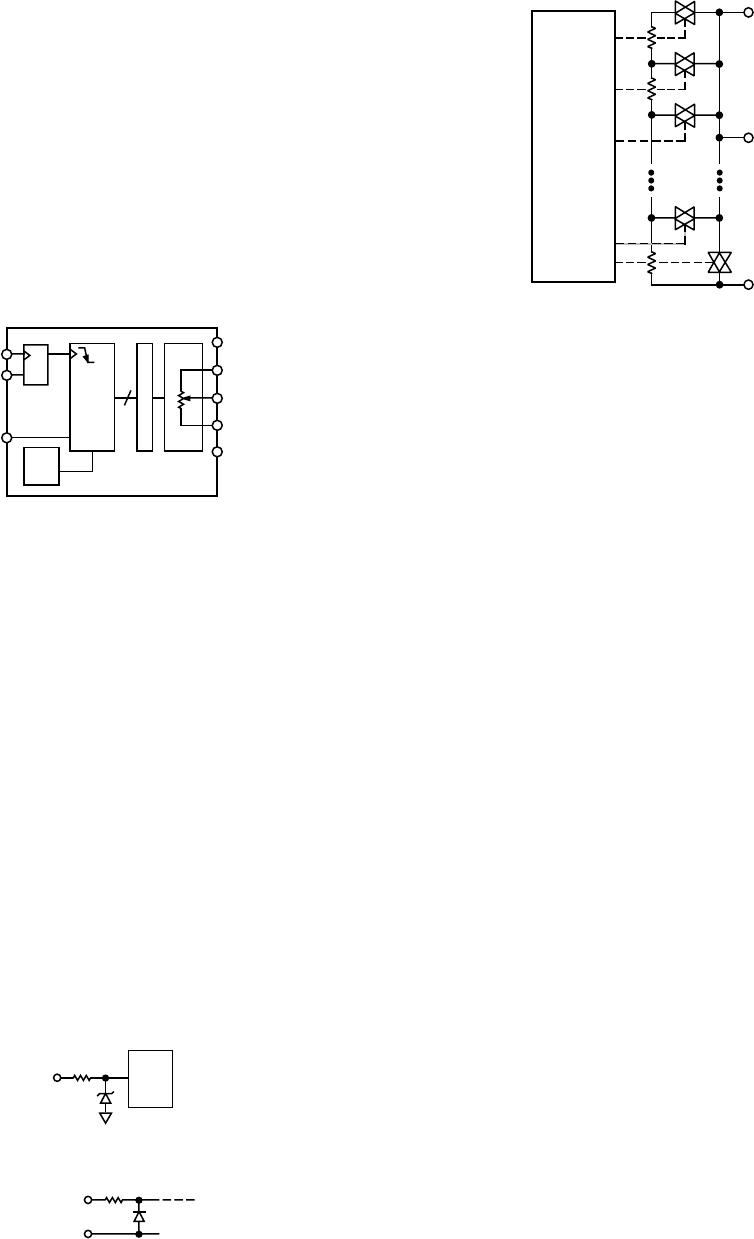

D0

D1

D2

D3

D4

D5

D6

RDAC

UP/DOWN

CNTR

&

DECODE

Wx

Bx

R

S

= R

NOMINAL

/128

R

S

R

S

R

S

Ax

Figure 38. AD5220 Equivalent RDAC Circuit

PROGRAMMING THE VARIABLE RESISTOR

Rheostat Operation

The nominal resistance of the RDAC between terminals A and

B is available with values of 10 kΩ, 50 kΩ, and 100 kΩ. The

final three characters of the part number determine the nominal

resistance value, e.g., 10 kΩ =10; 50 kΩ = 50; 100 kΩ = 100.

The nominal resistance (R

AB

) of the VR has 128 contact points

accessed by the wiper terminal, plus the B terminal contact. At

power ON the resistance from the wiper to either end Terminal

A or B is approximately equal. Clocking the CLK pin will in-

crease the resistance from the Wiper W to Terminal B by one

unit of R

S

resistance (see Figure 38). The resistance R

WB

is

determined by the number of pulses applied to the clock pin.

Each segment of the internal resistor string has a nominal resis-

tance value of R

S

= R

AB

/128, which becomes 78 Ω in the case of

the 10 kΩ AD5220BN10 product. Care should be taken to limit

the current flow between W and B in the direct contact state to

a maximum value of 5 mA to avoid degradation or possible de-

struction of the internal switch contact.

Like the mechanical potentiometer the RDAC replaces, it is

totally symmetrical (see Figure 38). The resistance between the

Wiper W and Terminal A also produces a digitally controlled

resistance R

WA

. When these terminals are used the B–terminal

should be tied to the wiper.

The typical part-to-part distribution of R

BA

is process lot depen-

dent having a ±30% variation. The change in R

BA

with tempera-

ture has a 800 ppm/°C temperature coefficient.

The R

BA

temperature coefficient increases as the wiper is pro-

grammed near the B-terminal due to the larger percentage con-

tribution of the wiper contact switch resistance, which has a

0.5%/°C temperature coefficient. Figure 14 shows the effect of

the wiper contact resistance as a function of code setting. An-

other performance factor influenced by the switch contact resis-

tance is the relative linearity error performance between the

10 kΩ, and the 50 kΩ or 100 kΩ versions. The same switch

contact resistance is used in all three versions. Thus the perfor-

mance of the 50 kΩ and 100 kΩ devices which have the least

impact on wiper switch resistance exhibits the best linearity

error, see Figures 7 and 8.