XC9572XL High Performance CPLD

6 www.xilinx.com DS057 (v2.0) April 3, 2007

Product Specification

R

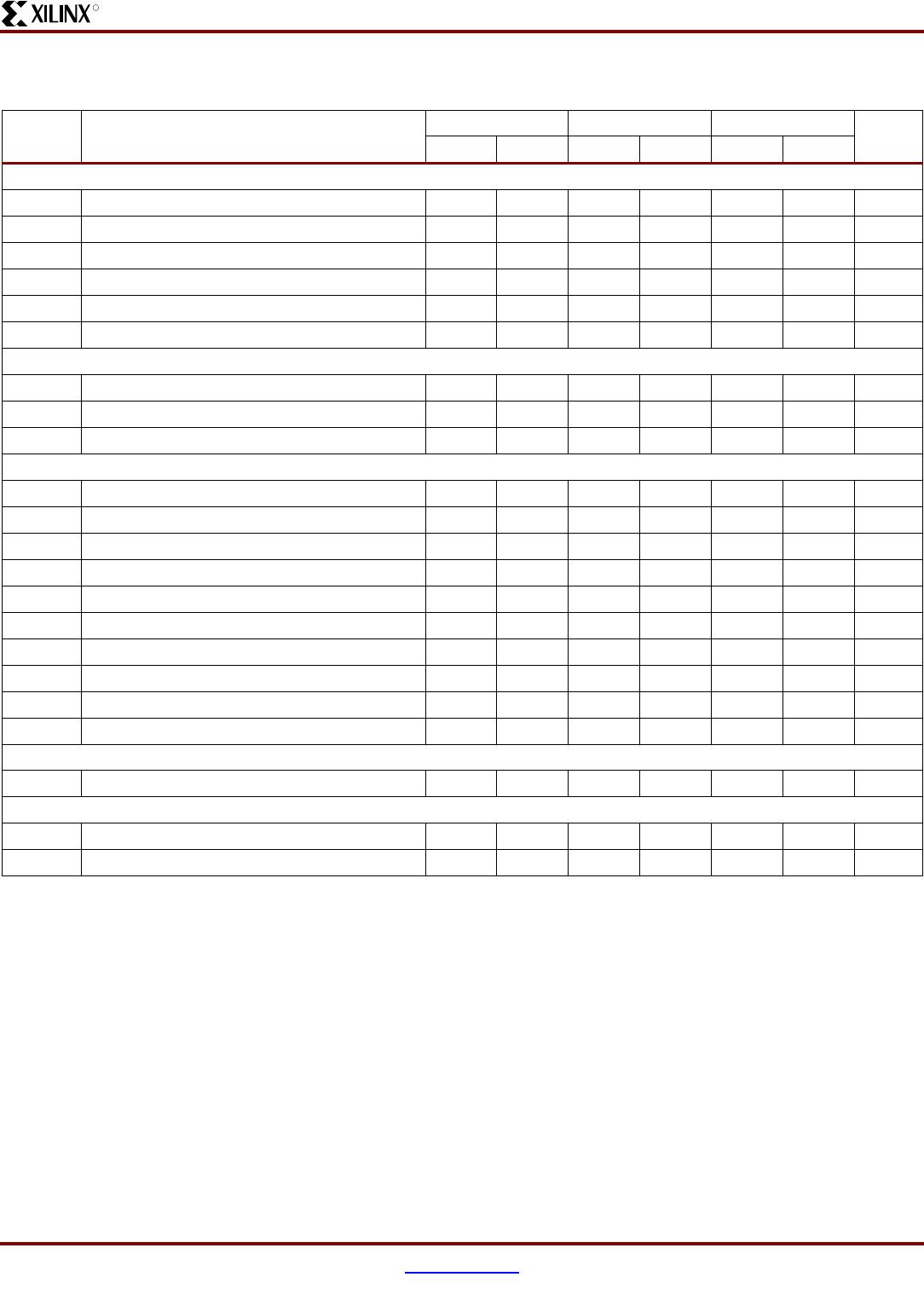

XC9572XL I/O Pins

(4)

Func-

tion

Block

Macro-

cell PC44 VQ44 CS48 VQ64 TQ100

BScan

Order

Func

-tion

Block

Macro-

cell PC44VQ44CS48VQ64TQ100

BScan

Order

1 1 ----16213 3 1 ----41105

1 2 1 39 D7 8 13 210 3 2 11 5 B5 22 32 102

1 3 - - D4 12 18 207 3 3 - - C4 31 49 99

1 4 ---1320204 3 4 ---325096

1 5 2 40 D6 9 14 201 3 5 12 6 A4 24 35 93

16341C7101519836---345390

1 7 ----25195 3 7 ----5487

18442C6111719238137B4253784

195

(1)

43

(1)

B7

(1)

15

(1)

22

(1)

18939148A3274281

1 10 - - - 18 28 186 3 10 - - D3 39 60 78

1116

(1)

44

(1)

B6

(1)

16

(1)

23

(1)

183 3 11 18 12 B2 33 52 75

1 12 ---2333180 3 12 ---406172

1 13 ----36177 3 13 ----6369

1147

(1)

1

(1)

A7

(1)

17

(1)

27

(1)

174 3 14 19 13 B1 35 55 66

11582A61929171 3152014C2365663

1 16 ----39168 3 162418D2426460

11793C52030165 3172216C3385857

1 18 ----40162 3 18 ----5954

2 1 ----87159 4 1 ----6551

2 2 35 29 F4 60 94 156 4 2 25 19 E1 43 67 48

2 3 ---5891153 4 3 ---467145

2 4 ---5993150 4 4 ---477242

2 5 36 30 G5 61 95 147 4 5 26 20 E2 44 68 39

2 6 37 31 F5 62 96 144 4 6 - - E4 49 76 36

2 7 ----3

(2)

141 4 7 ----7733

2 8 38 32 G6 63 97 138 4 8 27 21 F1 45 70 30

2939

(1)

33

(1)

G7

(1)

64

(1)

99

(1)

135 4 9 ----6627

2 10 ---11132 4 10 ---518124

21140

(1)

34

(1)

F6

(1)

2

(1)

4

(1)

129 4 11 28 22 G1 48 74 21

2 12 ---46126 4 12 ---528218

2 13 ----8123 4 13 ----8515

21442

(3)

36

(3)

E6

(3)

5

(3)

9

(3)

120 4 14 29 23 F2 50 78 12

2 15 43 37 E7 6 11 117 4 15 33 27 E3 56 89 9

2 16 ----10114 4 16 ----866

2174438E5712111 4173428G457903

2 18 ----92108 4 18 ----790

Notes:

1. Global control pin.

2. GTS1 for TQ100.

3. GTS1 for PC44, VQ44, CS48, and VQ64.

4. The pin-outs are the same for Pb-free versions of packages.