ADuM3300/ADuM3301 Data Sheet

Rev. D | Page 8 of 20

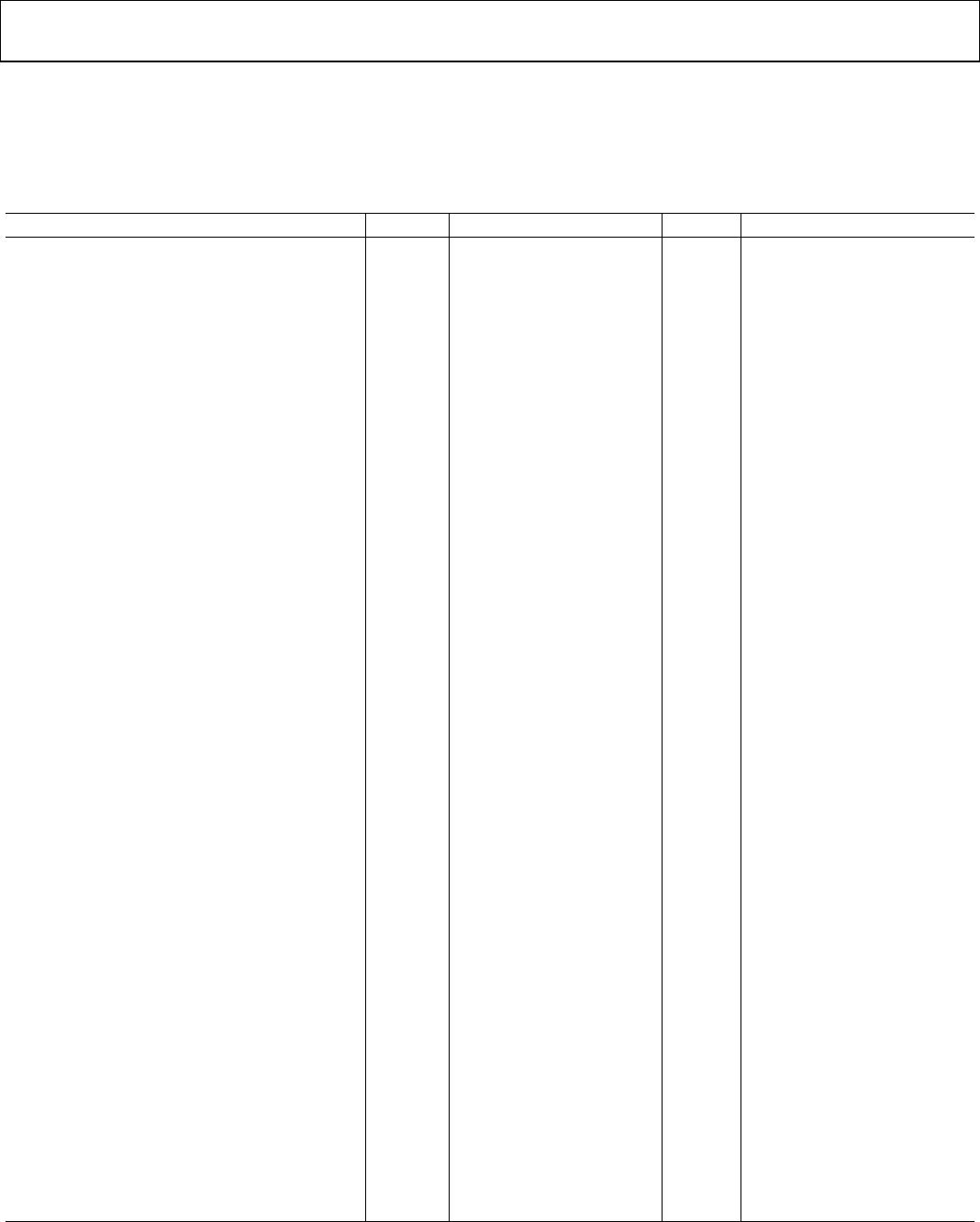

Parameter Symbol Min Typ Max Unit Test Conditions

90 Mbps (CRW Grade Only)

V

DD1

Supply Current I

DD1 (90)

5 V/3 V Operation 41 57 mA 45 MHz logic signal freq.

3 V/5 V Operation 22 31 mA 45 MHz logic signal freq.

DD2

DD2 (90)

5 V/3 V Operation 15 21 mA 45 MHz logic signal freq.

3 V/5 V Operation 28 41 mA 45 MHz logic signal freq.

For All Models

Input Currents I

IA

, I

IB

, I

IC

,

I

ID

, I

E1

, I

E2

−10 +0.01 +10 µA 0 V ≤ V

IA

, V

IB

, V

IC

, V

ID

≤ V

DD1

or V

DD2

,

0 V ≤ V

E1

, V

E2

≤ V

DD1

or V

DD2

Logic High Input Threshold

IH

EH

5 V/3 V Operation 2.0 V

3 V/5 V Operation 1.6 V

Logic Low Input Threshold

V

IL

, V

EL

5 V/3 V Operation 0.8 V

3 V/5 V Operation 0.4 V

Logic High Output Voltages V

OAH

, V

OBH

,

V

OCH

, V

ODH

(V

DD1

or

V

DD2

) − 0.1

(V

DD1

or V

DD2

) V I

Ox

= −20 µA, V

Ix

= V

IxH

(V

DD1

or

V

DD2

) − 0.4

(V

DD1

or

V

DD2

) − 0.2

V I

Ox

= −4 mA, V

Ix

= V

IxH

Logic Low Output Voltages V

OAL

, V

OBL

,

V

OCL

, V

ODL

Ox

Ix

IxL

Ox

Ix

IxL

0.2 0.4 V I

Ox

= 4 mA, V

Ix

= V

IxL

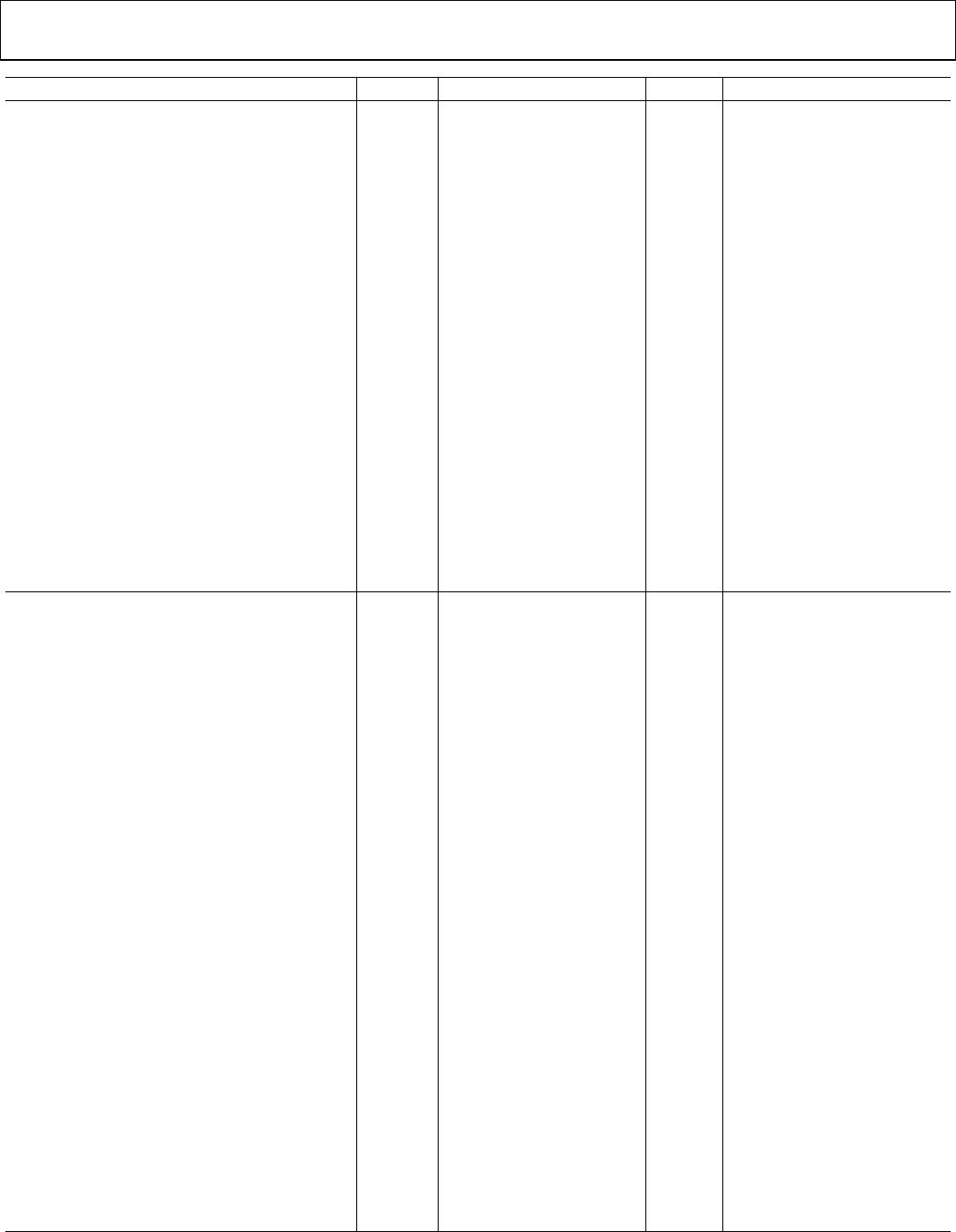

SWITCHING SPECIFICATIONS

ADuM3300ARWZ/ADuM3301ARWZ

Minimum Pulse Width

2

PW 1000 ns C

L

= 15 pF, CMOS signal levels

Maximum Data Rate

3

1 Mbps C

L

= 15 pF, CMOS signal levels

Propagation Delay

4

t

PHL

, t

PLH

50 70 100 ns C

L

= 15 pF, CMOS signal levels

Pulse Width Distortion, |t

PLH

− t

PHL

|

4

PWD 40 ns C

L

= 15 pF, CMOS signal levels

Propagation Delay Skew

5

t

PSK

50 ns C

L

= 15 pF, CMOS signal levels

Channel-to-Channel Matching

6

t

PSKCD/OD

50 ns C

L

= 15 pF, CMOS signal levels

ADuM3300BRWZ/ADuM3301BRWZ

Minimum Pulse Width

2

PW 100 ns C

L

= 15 pF, CMOS signal levels

Maximum Data Rate

3

10 Mbps C

L

= 15 pF, CMOS signal levels

4

PHL

PLH

L

= 15 pF, CMOS signal levels

Pulse Width Distortion, |t

PLH

PHL

4

L

= 15 pF, CMOS signal levels

Change vs. Temperature 5 ps/°C C

L

= 15 pF, CMOS signal levels

Propagation Delay Skew

5

t

PSK

22 ns C

L

= 15 pF, CMOS signal levels

Channel-to-Channel Matching,

Codirectional Channels

6

t

PSKCD

3 ns C

L

= 15 pF, CMOS signal levels

Channel-to-Channel Matching,

Opposing-Directional Channels

6

t

PSKOD

6 ns C

L

= 15 pF, CMOS signal levels

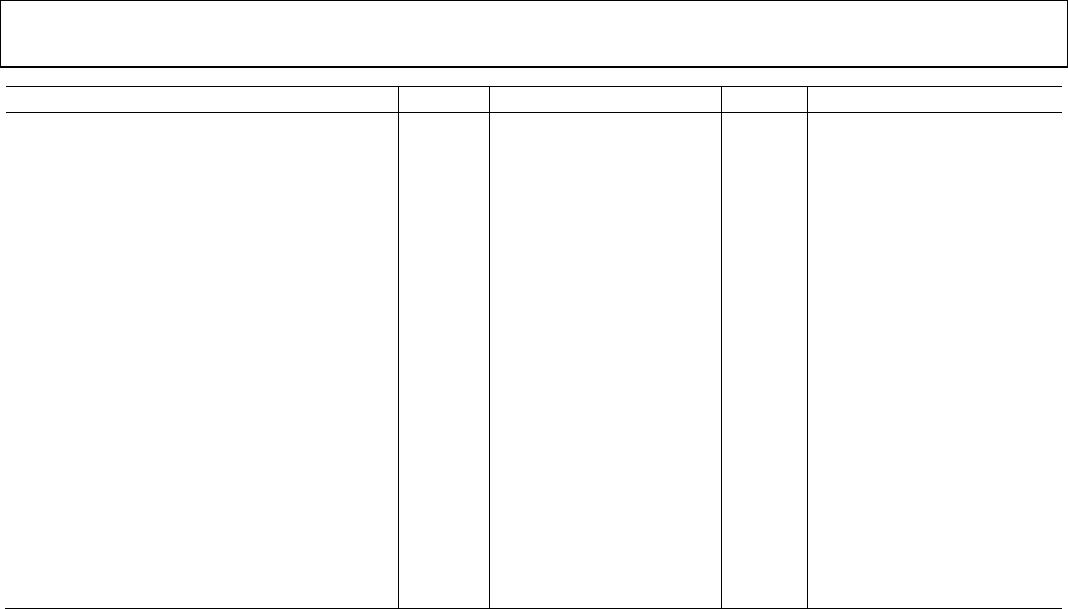

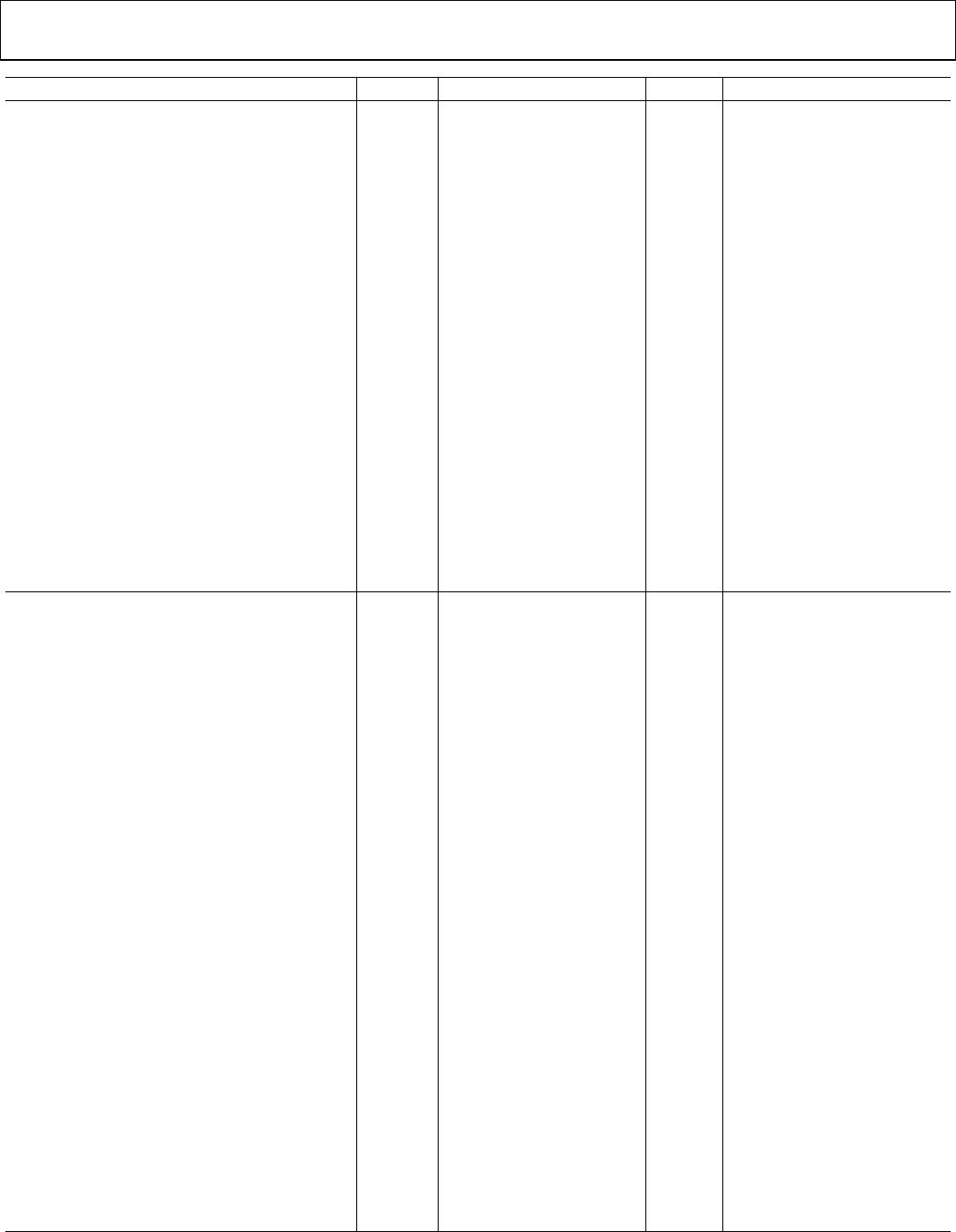

ADuM3300CRWZ/ADuM3301CRWZ

Minimum Pulse Width

2

PW 8.3 11.1 ns C

L

= 15 pF, CMOS signal levels

Maximum Data Rate

3

90 120 Mbps C

L

= 15 pF, CMOS signal levels

Propagation Delay

4

t

PHL

, t

PLH

20 30 40 ns C

L

= 15 pF, CMOS signal levels

Pulse Width Distortion, |t

PLH

− t

PHL

|

4

PWD 0.5 2 ns C

L

= 15 pF, CMOS signal levels

Change vs. Temperature 3 ps/°C C

L

= 15 pF, CMOS signal levels

Propagation Delay Skew

5

t

PSK

14 ns C

L

= 15 pF, CMOS signal levels

Channel-to-Channel Matching,

Codirectional Channels

6

t

PSKCD

2 ns C

L

= 15 pF, CMOS signal levels

Channel-to-Channel Matching,

Opposing-Directional Channels

6

t

PSKOD

5 ns C

L

= 15 pF, CMOS signal levels