Data Sheet ADuM1240/ADuM1241/ADuM1245/ADuM1246

Rev. B | Page 17 of 24

APPLICATIONS INFORMATION

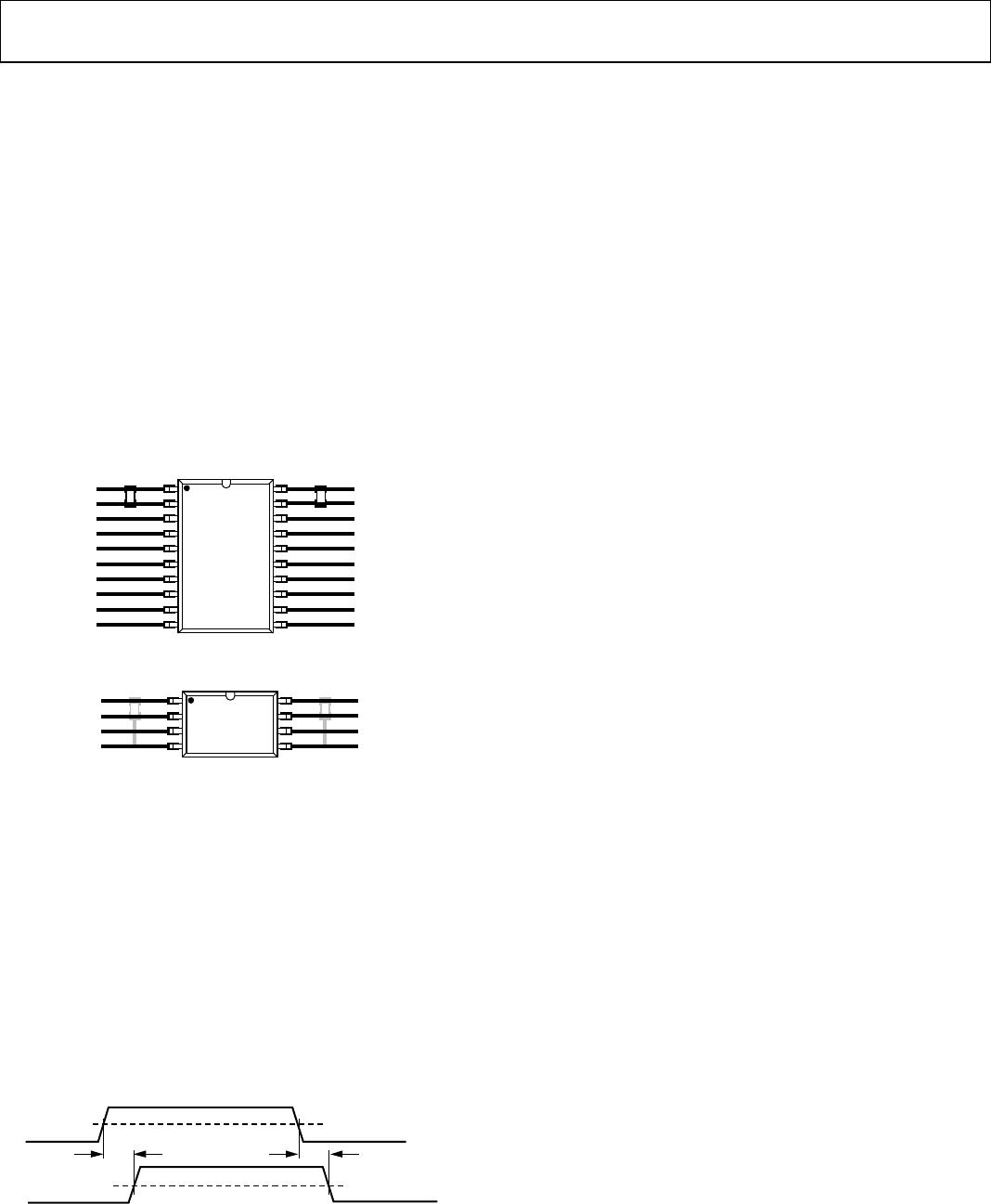

PCB LAYOUT

The ADuM1240/ADuM1241/ADuM1245/ADuM1246 digital

isolators require no external interface circuitry for the logic

interfaces. Power supply bypassing is strongly recommended at

both the input and output supply pins: V

DD1

and V

DD2

(see

Figure 27). Maintain the capacitor value between 0.01 μF and

0.1 μF and for best results, ensure that the total lead length

between both ends of the capacitor and the input power supply

does not exceed 20 mm.

With proper PCB design choices, these digital isolators readily

meet CISPR 22 Class A (and FCC Class A) emissions standards,

as well as the more stringent CISPR 22 Class B (and FCC Class B)

standards in an unshielded environment. Refer to AN-1109 for

PCB related electromagnetic interference (EMI) mitigation

techniques, including board layout and stack up issues.

V

DD1

GND

1

NIC

NIC

V

IA/

V

OA

V

IB

EN

1

NIC

NIC = NOT INTERNALLY CONNECTED.

V

DD2

GND

2

NIC

NIC

V

OA/

V

IA

V

OB

EN

2

NIC

NIC

GND

1

NIC

GND

2

11925-024

Figure 27. Recommended PCB Layout, 20-Lead SSOP (RS-20)

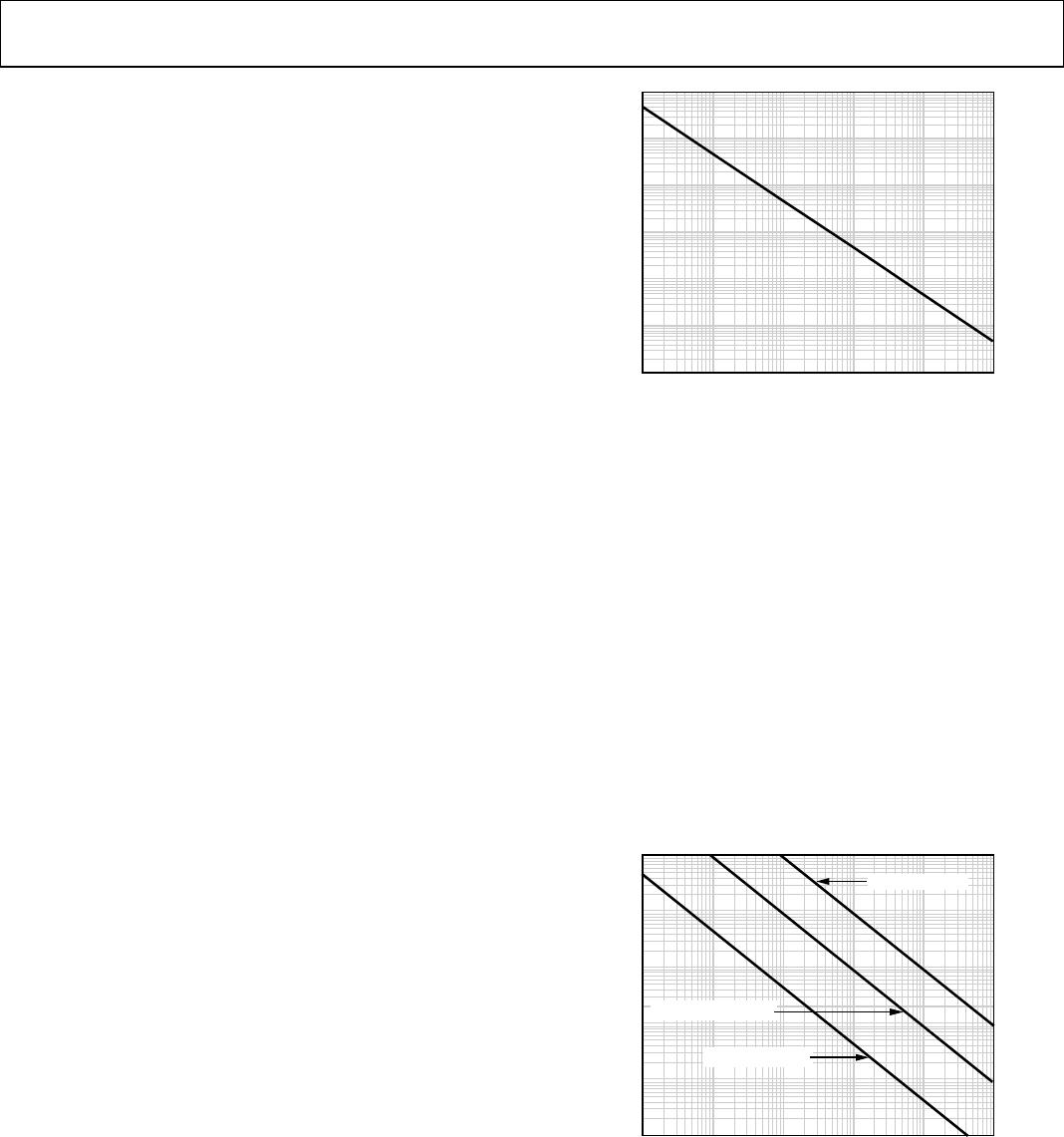

V

DD1

V

IA/

V

OA

V

IB

V

DD2

V

OA/

V

IA

V

OB

GND

1

GND

2

11925-124

Figure 28. Recommended PCB Layout, 8-Lead SOIC (R-8)

For applications involving high common-mode transients, it is

important to minimize board coupling across the isolation barrier.

Furthermore, design the board layout so that any coupling that

does occur equally affects all pins on a given component side.

Failure to ensure this equal capacitive coupling of pins can

cause voltage differentials between pins exceeding the absolute

maximum ratings of the device, thereby leading to latch-up or

permanent damage.

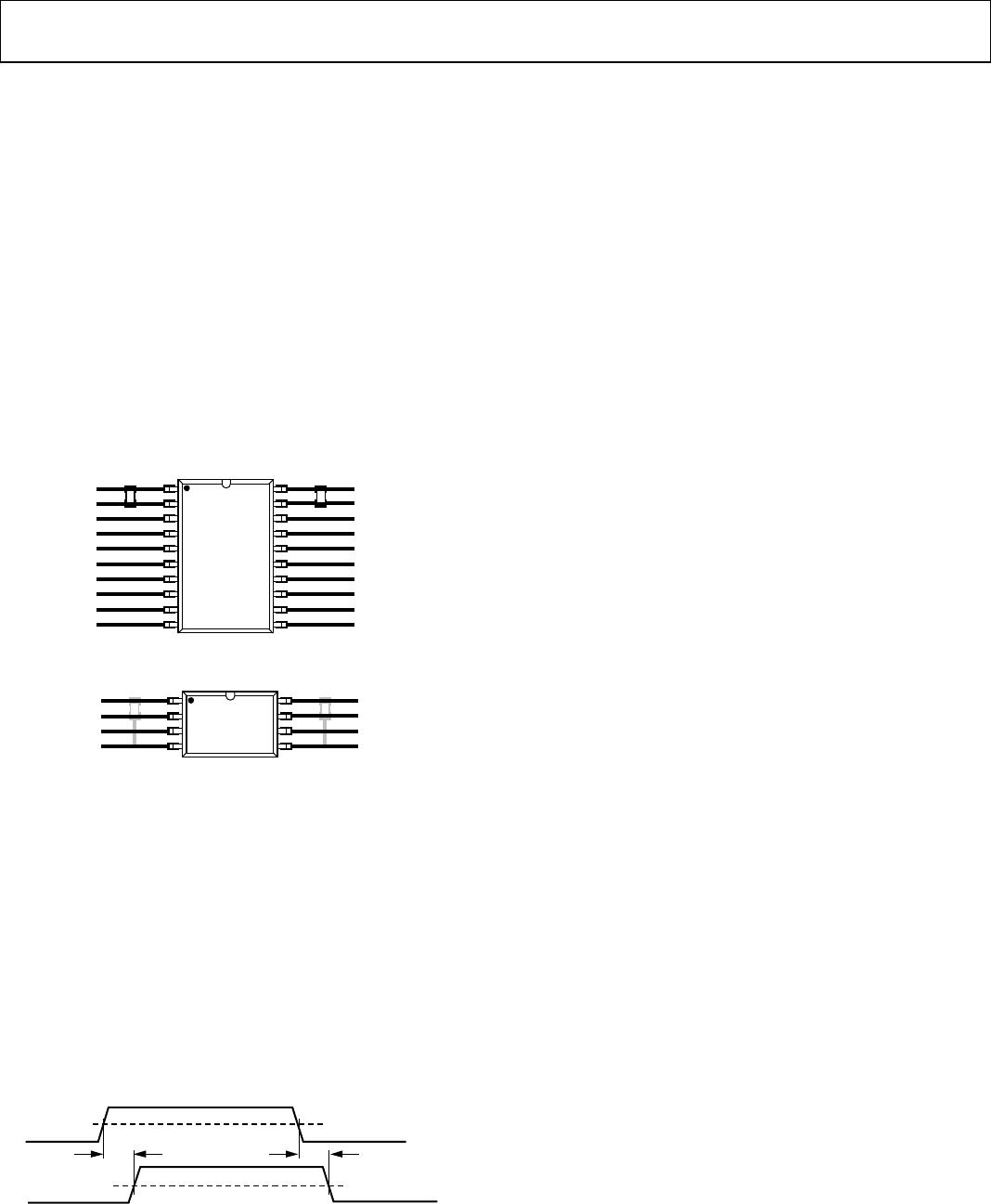

PROPAGATION DELAY RELATED PARAMETERS

Propagation delay is a parameter that describes the time it takes

a logic signal to propagate through a component. The input to

output propagation delay time for a high to low transition can

differ from the propagation delay time of a low to high transition.

INPUT (V

Ix

)

OUTPUT (V

Ox

)

t

PLH

t

PHL

50%

50%

11925-025

Figure 29. Propagation Delay Parameters

Pulse width distortion is the maximum difference between

these two propagation delay values, and an indication of how

accurately the timing of the input signal is preserved.

Channel to channel matching refers to the maximum amount

the propagation delay differs between channels within a single

component of the ADuM1240/ADuM1241/ADuM1245/

ADuM1246.

Propagation delay skew refers to the maximum amount the

propagation delay differs between multiple ADuM1240/

ADuM1241/ADuM1245/ADuM1246 components operating

under the same conditions.

DC CORRECTNESS AND LOW POWER OPERATION

Standard Operating Mode

Positive and negative logic transitions at the isolator input cause

narrow (~1 ns) pulses to be sent to the decoder using the

transformer. The decoder is bistable and is, therefore, either set

or reset by the pulses, indicating input logic transitions. When

refresh and watchdog functions are enabled, by pulling EN

1

and

EN

2

low, in the absence of logic transitions at the input for more

than ~140 μs, a periodic set of refresh pulses, indicative of the

correct input state, is sent to ensure dc correctness at the output. If

the decoder receives no internal pulses of more than approximately

200 μs, the device assumes that the input side is unpowered or

nonfunctional, in which case, the isolator watchdog circuit

forces the output to a default state. The default state is either high,

as in the ADuM1240 and ADuM1241 versions, or low, as in the

ADuM1245 and ADuM1246 versions.

Low Power Operating Mode

For the lowest power consumption, disable the refresh and

watchdog functions of the ADuM1240/ADuM1241/ADuM1245/

ADuM1246 by pulling EN

1

and EN

2

to logic high. These control

pins must be set to the same value on each side of the component

for proper operation.

In this mode, the current consumption of the chip drops to the

microampere range. However, be careful when using this mode,

because dc correctness is no longer guaranteed at startup. For

example, if the following sequence of events occurs:

1. Power is applied to Side 1.

2. A high level is asserted on the V

IA

input.

3. Power is applied to Side 2.

The high on V

IA

is not automatically transferred to the Side 2

V

OA

, and there can be a level mismatch that is not corrected until a

transition occurs at V

IA

. When power is stable on each side, and a

transition occurs on the input of the channel, the input and output

state of that channel is correctly matched. This contingency can

be resolved in several ways, such as sending dummy data, or

toggling refresh on for a short period to force synchronization after

turn on.