ATA Flash Drive 257

AP-FD25C22ExxxxxS-XXT

7

© 2015 Apacer Technology Inc. Rev. 1.3

5. Flash Management

5.1 Advanced wear-leveling algorithms

Flash memory devices differ from Hard Disk Drives (HDDs) in terms of how blocks are utilized. For HDDs,

when a change is made to stored data, like erase or update, the controller mechanism on HDDs will

perform overwrites on blocks. On the other hand, NAND flash storage adopt flash as their primary media.

Unlike HDDs, flash blocks cannot be overwritten and each P/E cycle wears down the lifespan of blocks

gradually. Repeatedly program/erase cycles performed on the same memory cells will eventually cause

some blocks to age faster than others. This would bring flash storages to their end of service term earlier.

Wear leveling is an important mechanism that level out the wearing of blocks so that the wearing-down of

blocks can be almost evenly distributed. This will increase the lifespan of SSDs. Commonly used wear

leveling types are Static and Dynamic.

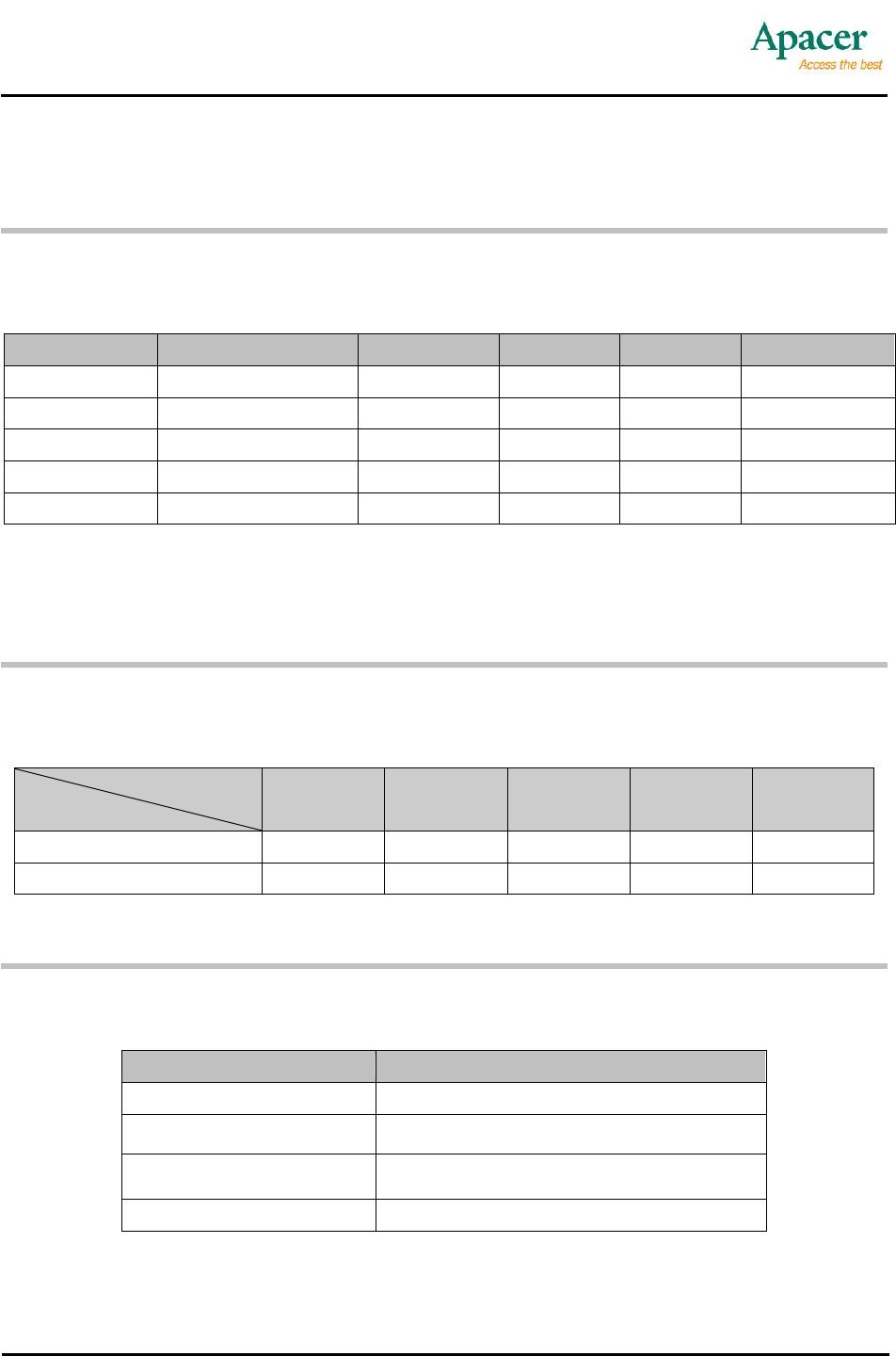

5.2 S.M.A.R.T.

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology, an open standard

allowing disk drives to automatically monitor their own health and report potential problems. It protects the

user from unscheduled downtime by monitoring and storing critical drive performance and attributes

parameters. Ideally, this should allow taking proactive actions to prevent impending drive failure.

Apacer devices use the standard SMART command B0h to read data out from the drive to activate our

SMART feature that complies with the ATA/ATAPI specifications. Based on the SFF-8035i Rev. 2.0

specifications, SMART Attribute IDs shall include Initial bad block count, Bad block count, Spare block

count, Maximum erase count, Average erase count and Power cycle. When the SMART Utility running on

the host, it analyzes and reports the disk status to the host before the device reaches in critical condition.

5.3 Built-in Hardware ECC

The properties of NAND flash memory make it ideal for applications that require high integrity while

operating in challenging environments. The integrity of data to NAND flash memory is generally

maintained through ECC algorithms. This ATA-Flash Drive is programmed with a hardware ECC engine

which correct up to 72 bits per 1KB.

5.4 Flash Block Management

Current process technology is unable to guarantee total reliability of NAND flash memory array. When a

flash memory device leaves factory, it comes with a highly minimal number of initial bad block during

production or out-of-factory as there is no currently known technology that produce flash chips free of bad

blocks. On the other hand, bad blocks may develop during program/erase cycles. When host performs

program/erase command on a block, bad block may appear in Status Register. Since bad blocks are

inevitable, the solution is to keep them in control. Apacer flash devices are programmed with ECC, block

mapping technique and S.M.A.R.T to reduce invalidity or error. Once bad blocks are detected, data in

those blocks will be transferred to free blocks and error will be corrected by designated algorithms.