AD628

Rev. G | Page 17 of 20

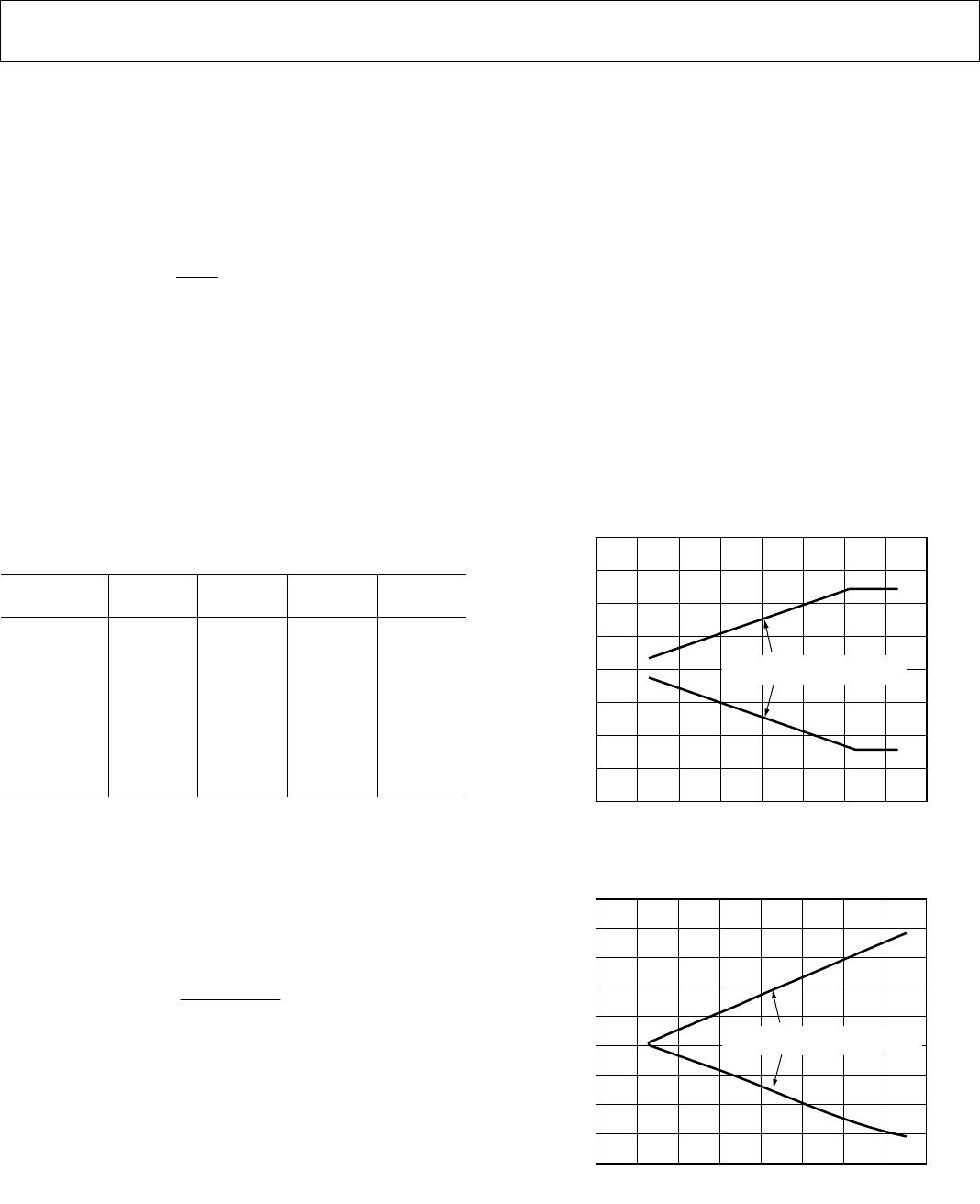

The differential input voltage range is constrained to the linear

operation of the internal amplifiers, A1 and A2. The voltage

applied to the inputs of A1 and A2 should be between

V

S−

+ 1.2 V and V

S+

− 1.2 V. Similarly, the outputs of A1 and A2

should be kept between V

S−

+ 0.9 V and V

S+

− 0.9 V.

VOLTAGE LEVEL CONVERSION

Industrial signal conditioning and control applications typically

require connections between remote sensors or amplifiers and

centrally located control modules. Signal conditioners provide

output voltages of up to ±10 V full scale. However, ADCs or

microprocessors operating on single 3.3 V to 5 V logic supplies

are now the norm. Thus, the controller voltages require further

reduction in amplitude and reference.

Furthermore, voltage potentials between locations are seldom

compatible, and power line peaks and surges can generate

destructive energy between utility grids. The AD628 offers an

ideal solution to both problems. It attenuates otherwise destruc-

tive signal voltage peaks and surges by a factor of 10 and shifts

the differential input signal to the desired output voltage.

Conversion from voltage-driven or current-loop systems is

easily accomplished using the circuit shown in

Figure 32. This

shows a circuit for converting inputs of various polarities and

amplitudes to the input of a single-supply ADC.

To adjust common-mode output voltage, connect Pin 3 (V

REF

)

and the lower end of the 10 kΩ resistor to the desired voltage.

The output common-mode voltage is the same as the reference

voltage.

Designing such an application can be done in a few simple

steps, which includes the following:

• Determine the required gain. For example, if the input

voltage must be changed from ±10 V to +5 V, the gain now

needs to be +5/+20 or +0.25.

• Determine if the circuit common-mode voltage should be

changed. An

AD7940 ADC is illustrated for this example.

When operating from a 5 V supply, the common-mode

voltage of the

AD7940 is half the supply, or 2.5 V. If the

AD628 reference pin and the lower terminal of the 10 kΩ

resistor are connected to a 2.5 V voltage source, the output

common-mode voltage is 2.5 V.

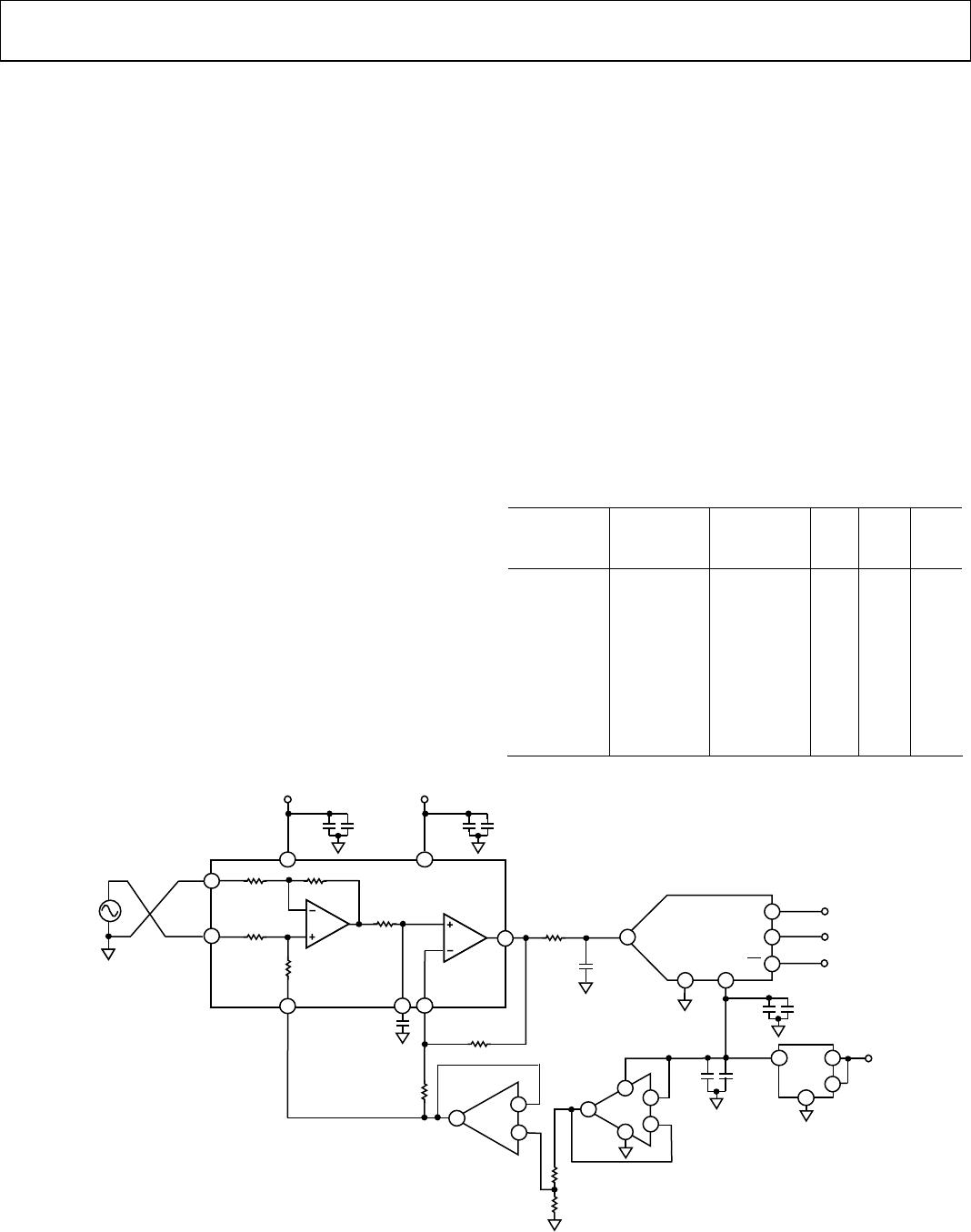

Table 6 shows resistor and reference values for commonly used

single-supply converter voltages. R

EXT3

is included as an option

to balance the source impedance into A2. This is described in

more detail in the

Gain Adjustment section.

Table 6. Nearest 1% Resistor Values for Voltage Level

Conversion Applications

Input

Voltage (V)

ADC

Supply

Voltage (V)

Desired

Output

Voltage (V)

V

REF

(V)

R

EXT1

(kΩ)

R

EXT2

kΩ)

±10 5 2.5 2.5 15 10

±5 5 2.5 2.5 39.7 10

+10 5 2.5 0 39.7 10

+5 5 2.5 0 89.8 10

±10 3 1.25 1.25 2.49 10

±5 3 1.25 1.25 15 10

+10 3 1.25 0 15 10

+5 3 1.25 0 39.7 10

5

1

3 4

8

2

7

+V

S

–V

S

6

–IN

+IN

V

REF

100k

10k

100k

10k

10k

A1

A2

4

5

6

3

1

2

SCLK

SDATA

CS

GND

V

DD

V

IN

AD628

SERIAL DATA

REF195

+12V

V

OUT

V

IN

2

3

4

6

C

FILT

R

G

10F

0.1F

10F

0.1F

10F0.1F 10F0.1F

AD7940

±10V

15nF

2

3

1

AD8606

1/2

49.9

33nF

+12

12

10k

10k

AD628 REFERENCE VO LTAGE

R

EXT2

10k

R

E

X

T

1

1

5

k

AD8606

2/2

5

6

7

4

8

02992-030

OUT

Figure 32. Level Shifter