© Semiconductor Components Industries, LLC, 2016

October, 2017 − Rev. 1

1 Publication Order Number:

ESD7241/D

ESD7241, SZESD7241

ESD Protection Diode

Ultra−Low Capacitance

Micro−Packaged Diodes for ESD Protection

The ESD7241 is designed to protect voltage sensitive components

that require ultra−low capacitance from ESD and transient voltage

events. It has industry leading capacitance linearity over voltage

making it ideal for RF applications. This capacitance linearity

combined with the extremely small package and low insertion loss

makes this part well suited for use in antenna line applications for

wireless handsets and terminals.

Features

• Industry Leading Capacitance Linearity Over Voltage

• Ultra−Low Capacitance: < 1.0 pF Max

• Insertion Loss: 0.15 dB at 1 GHz; 0.60 dB at 3 GHz

• Low Leakage: < 0.5 mA

• Protection for the following IEC Standards:

♦ IEC61000−4−2 (ESD): Level 4 ±28 kV Contact

♦ IEC61000−4−4 (EFT): 40 A −5/50 ns

♦ IEC61000−4−5 (Lightning): 2.5 A (8/20 ms)

• SZ Prefix for Automotive and Other Applications Requiring Unique

Site and Control Change Requirements; AEC−Q101 Qualified and

PPAP Capable

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

Typical Applications

• RF Signal ESD Protection

• Near Field Communications

• USB 3.x Vbus Protection

MAXIMUM RATINGS (T

A

= 25°C unless otherwise noted)

Rating

Symbol Value Unit

IEC 61000−4−2 (ESD) (Note 1) ±28 kV

Total Power Dissipation (Note 2) @ T

A

= 25°C

Thermal Resistance, Junction−to−Ambient

°P

D

°

R

q

JA

300

400

mW

°C/W

Junction and Storage Temperature Range T

J

, T

stg

−55 to

+150

°C

Lead Solder Temperature − Maximum

(10 Second Duration)

T

L

260 °C

Stresses exceeding those listed in the Maximum Ratings table may damage the

device. If any of these limits are exceeded, device functionality should not be

assumed, damage may occur and reliability may be affected.

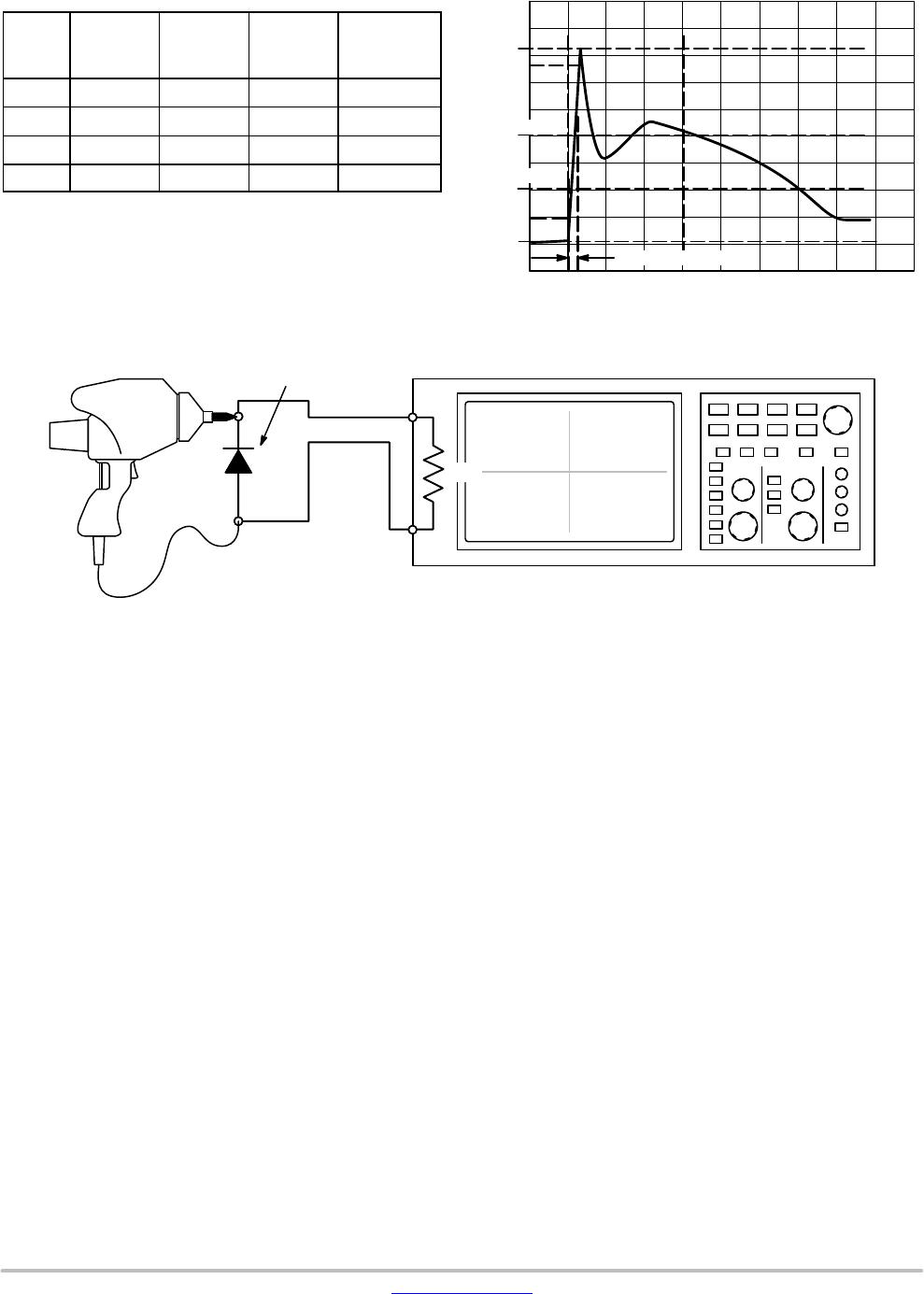

1. Non−repetitive current pulse at T

A

= 25°C, per IEC61000−4−2 waveform.

2. Mounted with recommended minimum pad size, DC board FR−4

Device Package Shipping

†

ORDERING INFORMATION

www.onsemi.com

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

ESD7241N2T5G X2DFN2

(Pb−Free)

8000 / Tape &

Reel

MARKING

DIAGRAM

2 = Specific Device Code

M = Date Code

X2DFN2

CASE 714AB

2 M

G

SZESD7241N2T5G X2DFN2

(Pb−Free)

8000 / Tape &

Reel

8:1