ATF16LV8C

5

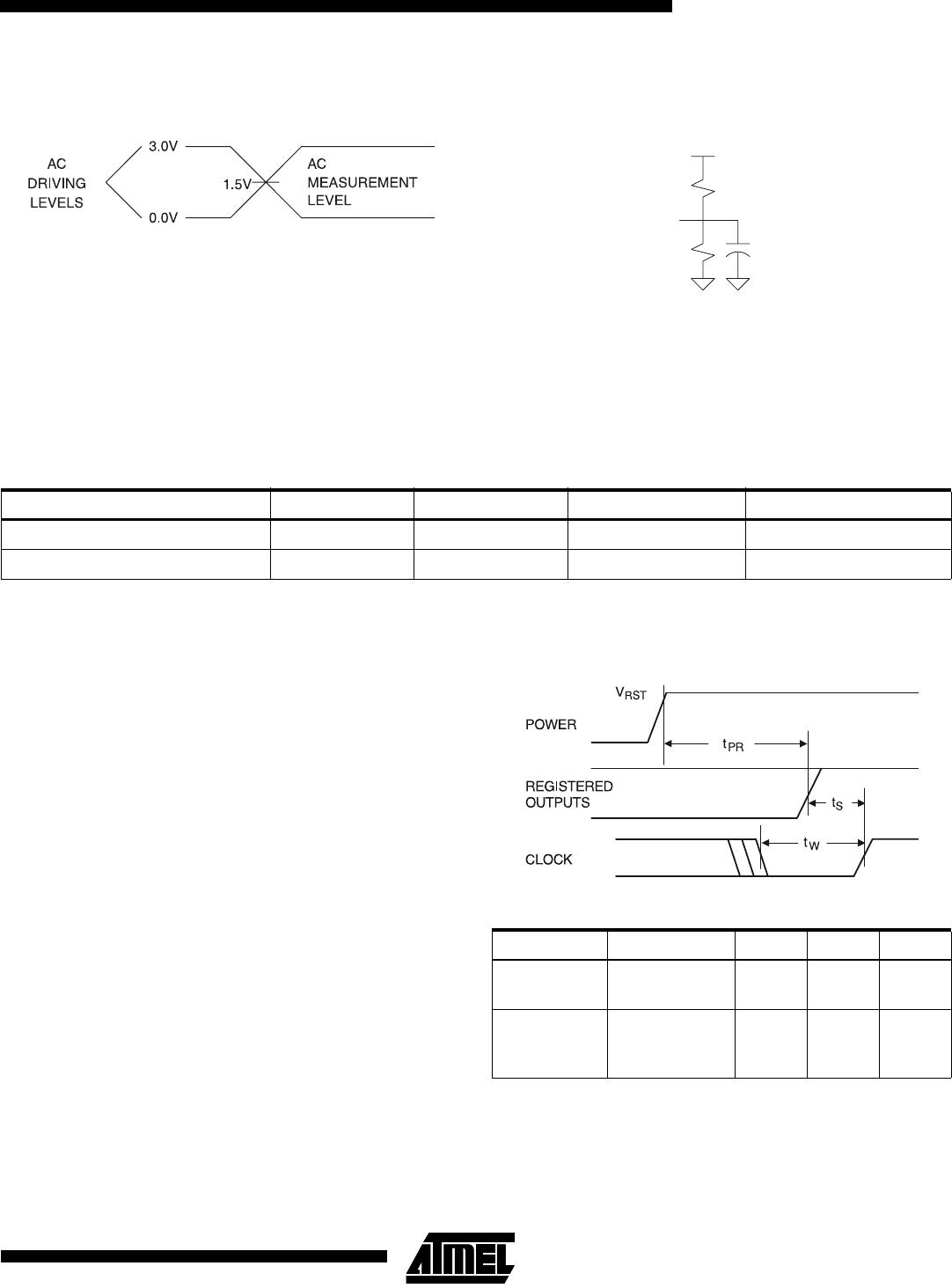

Input Test Waveforms and

Measurement Levels:

t

R

, t

F

< 1.5ns (10% to 90%)

Output Test Loads:

Commercial

Note: Similar devices are tested with slightly different loads.

These load differences may affect output signals’ delay

and slew rate. Atmel devices are tested with sufficient

margins to meet compatible devices.

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

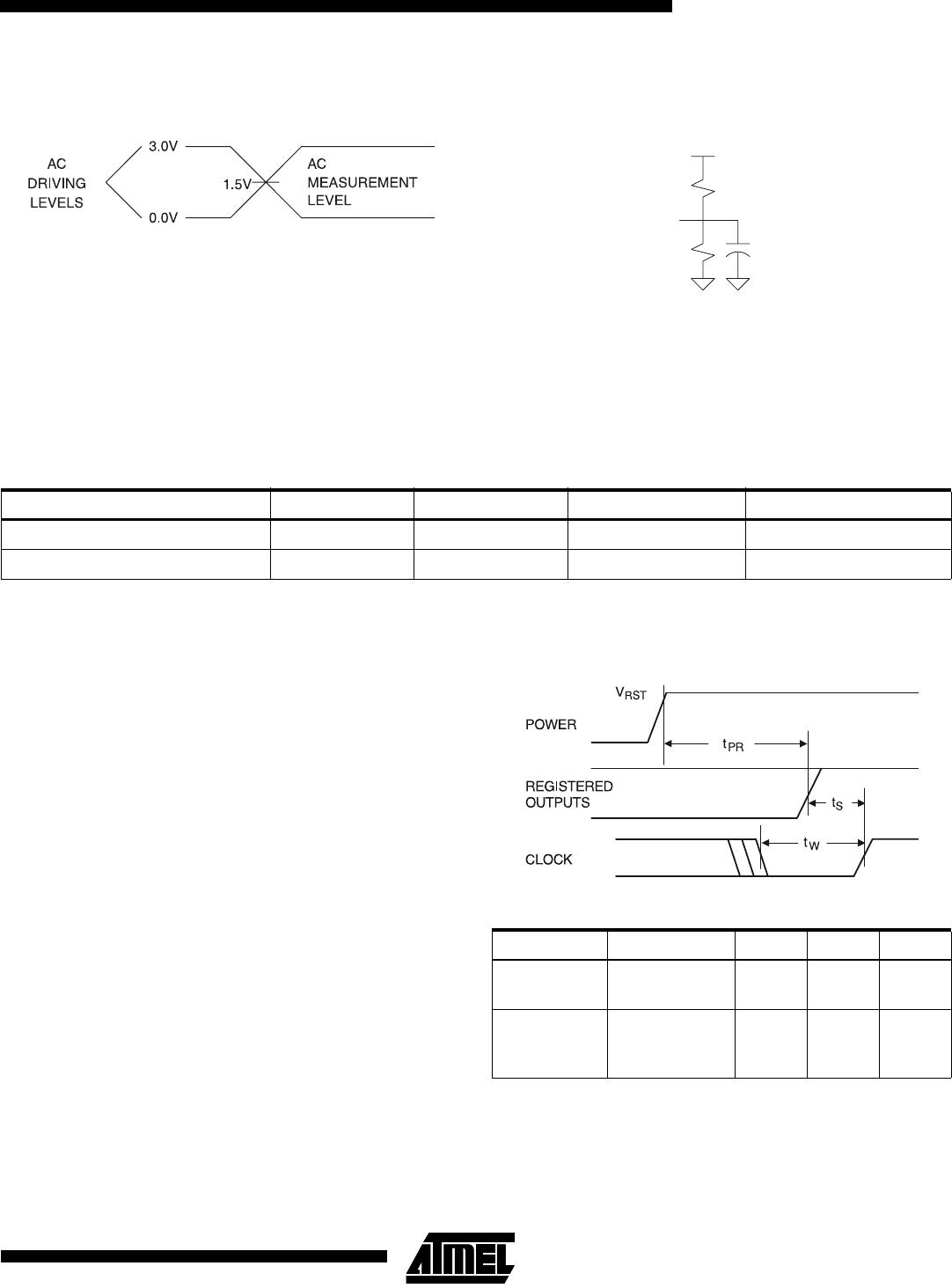

Power-up Reset

The ATF16LV8C’s registers are designed to reset during

power-up. At a point delayed slightly from V

CC

crossing

V

RST

, all registers will be reset to the low state. As a result,

the registered output state will always be high on power-up.

This feature is critical for state machine initialization.

However, due to the asynchronous nature of reset and the

uncertainty of how V

CC

actually rises in the system, the

following conditions are required:

1. The V

CC

rise must be monotonic from below 0.7V.

2. The signals from which the clock is derived must

remain stable during T

PR

.

3. After T

PR

, all input and feedback setup times must

be met before driving the clock term high.

OUTPUT

PIN

3.3V

CL = 35 pF

R1 = 316

R2 = 348

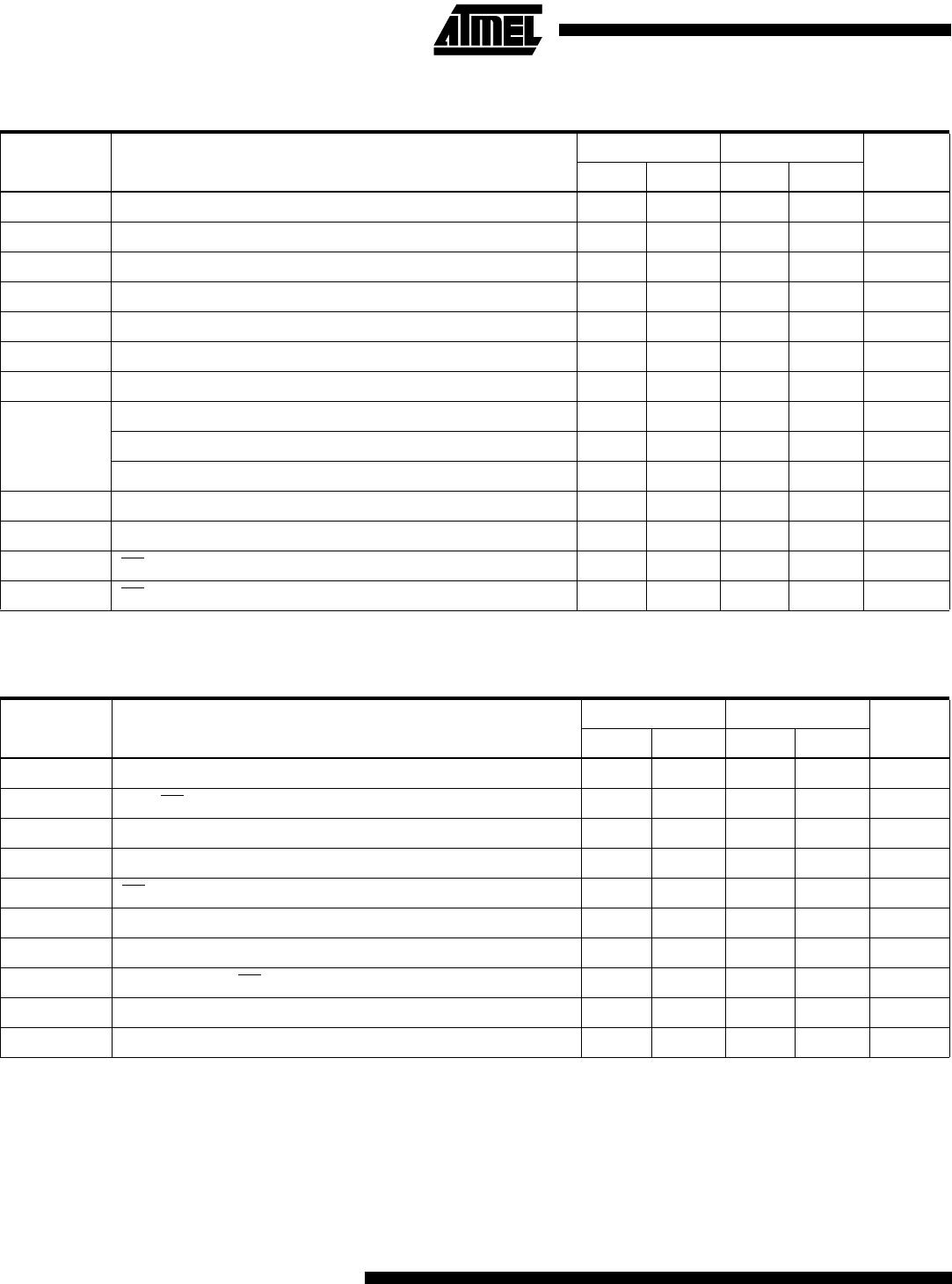

Pin Capacitance

(f = 1 MHz, T = 25°C)

(1)

Typ Max Units Conditions

C

IN

58 pF V

IN

= 0V

C

OUT

68 pF V

OUT

= 0V

Parameter Description Typ Max Units

T

PR

Power-up

Reset Time

600 1,000 ns

V

RST

Power-up

Reset

Voltage

2.5 3.0 V