8

COMMERCIAL TEMPERATURE RANGE

IDT7280/7281/7282/7283/7284/7285 5V ASYNCHRONOUS FIFO

DUAL 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

JUNE 29, 2012

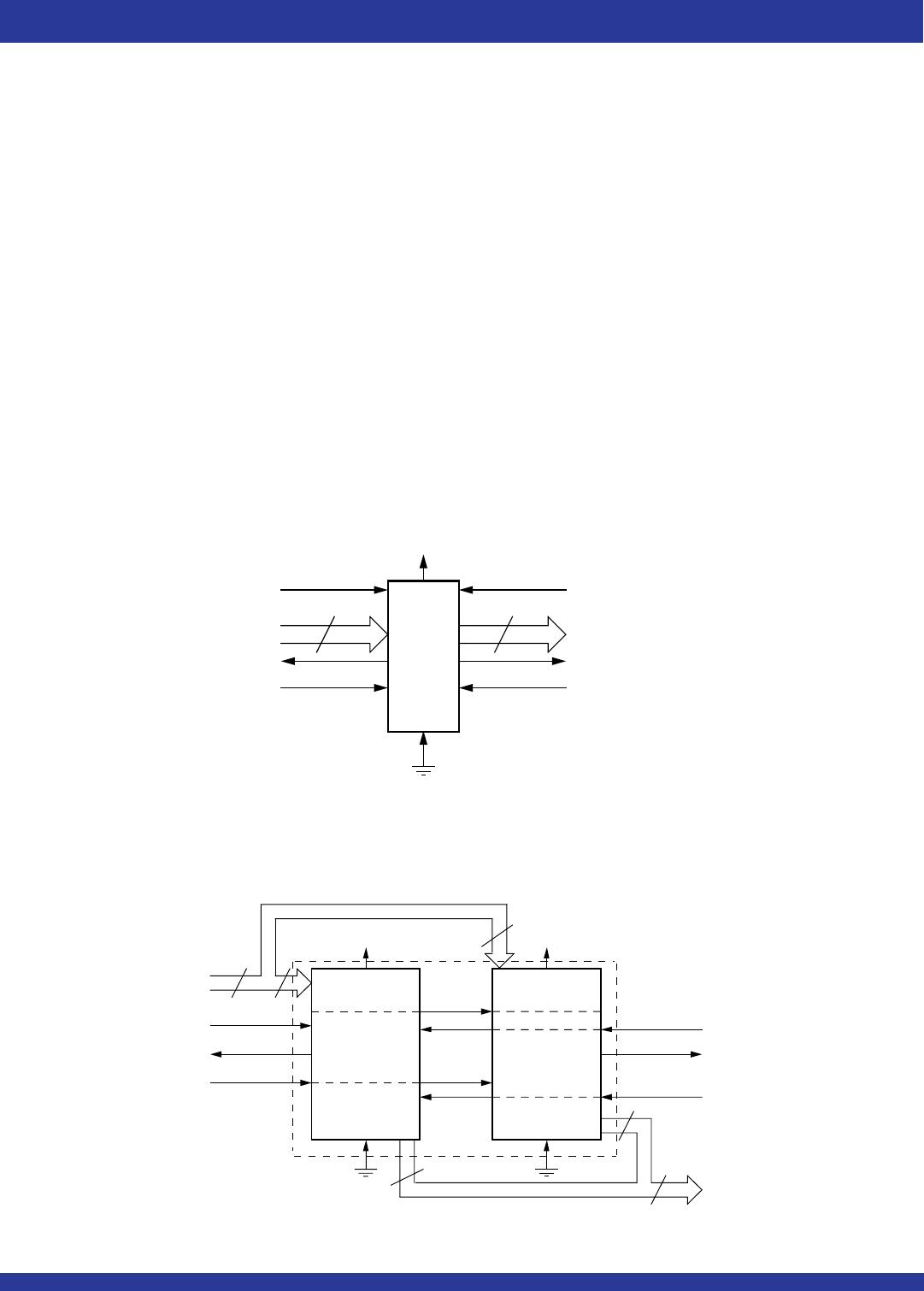

Figure 13. Block Diagram of 256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18, 4,096 x 18, 8,192 x 18 FIFO Memory Used in Width Expansion Mode

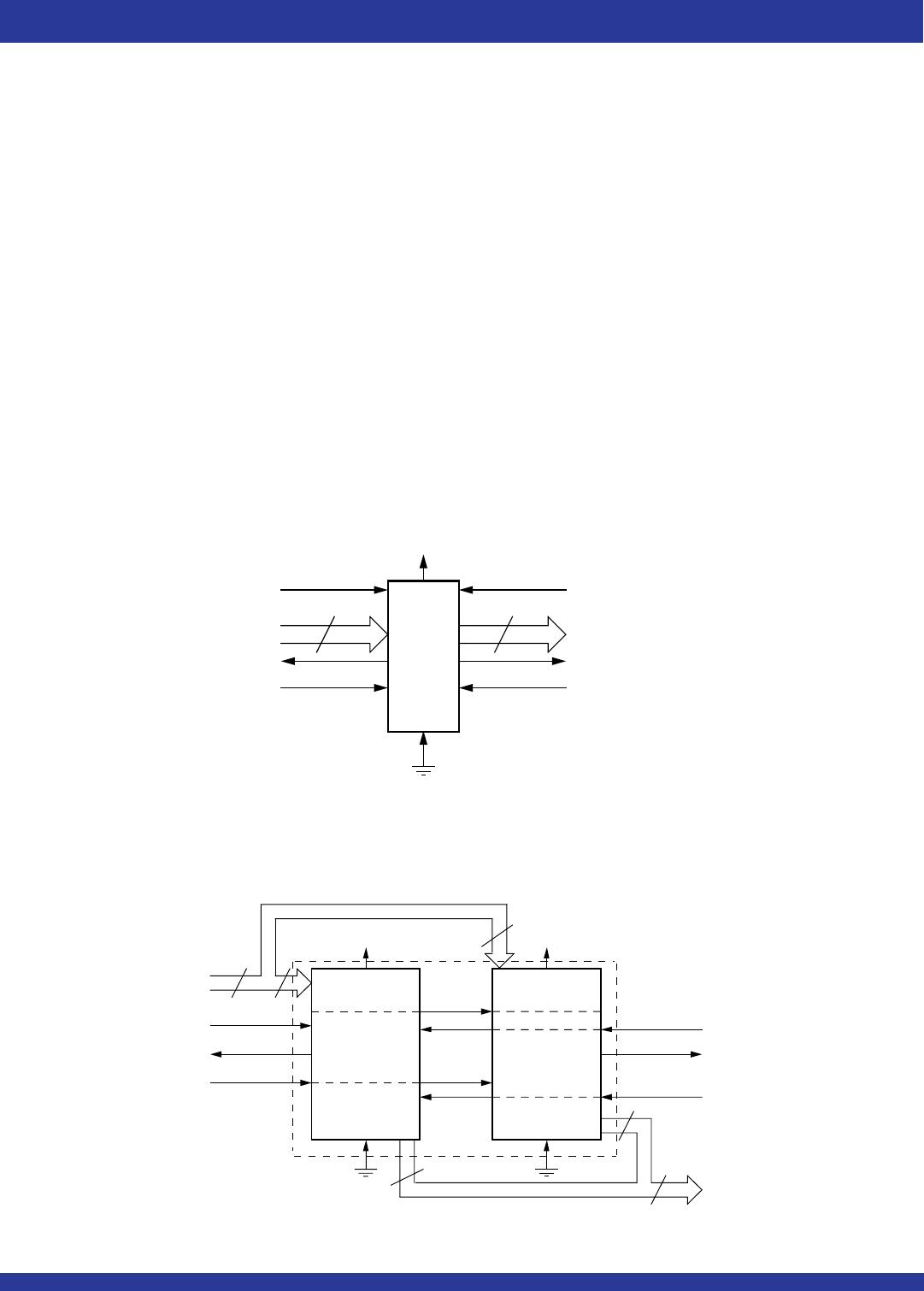

Figure 12. Block Diagram of One 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9, 8,192 x 9 FIFO Used in Single Device Mode

USAGE MODES:

WIDTH EXPANSION

Word width may be increased simply by connecting the corresponding input

control signals of multiple FIFOs. Status flags (EF, FF and HF) can be detected

from any one FIFO. Figure 13 demonstrates an 18-bit word width by using the

two FIFOs contained in the IDT7280/7281/7282/7283/7284/7285s. Any word

width can be attained by adding FIFOs (Figure 13).

BIDIRECTIONAL OPERATION

Applications which require data buffering between two systems (each

system capable of Read and Write operations) can be achieved by pairing

IDT7280/7281/7282/7283/7384/7285s as shown in Figure 16. Both Depth

Expansion and Width Expansion may be used in this mode.

DATA FLOW-THROUGH

Two types of flow-through modes are permitted, a read flow-through

and write flow-through mode. For the read flow-through mode (Figure 17),

the FIFO permits a reading of a single word after writing one word of data into

an empty FIFO. The data is enabled on the bus in (t

WEF + tA) ns after the rising

edge of W, called the first write edge, and it remains on the bus until the R line

is raised from LOW-to-HIGH, after which the bus would go into a three-state

mode after tRHZ ns. The EF line would have a pulse showing temporary

deassertion and then would be asserted.

In the write flow-through mode (Figure 18), the FIFO permits the writing

of a single word of data immediately after reading one word of data from a

full FIFO. The R line causes the FF to be deasserted but the W line being LOW

causes it to be asserted again in anticipation of a new data word. On the rising

edge of W, the new word is loaded in the FIFO. The W line must be toggled when

FF is not asserted to write new data in the FIFO and to increment the write pointer.

COMPOUND EXPANSION

The two expansion techniques described above can be applied together

in a straightforward manner to achieve large FIFO arrays (see Figure 15).

WRITE (W)

DATA IN (D)

FULL FLAG (FF)

RESET (RS)

9

READ (R)

9

DATA OUT (Q)

EMPTY FLAG (EF)

RETRANSMIT (RT)

EXPANSION IN (XI)

(HF)

FIFO

A or B

IDT

7280

7281

7282

7283

7284

7285

(HALF-FULL FLAG)

3208 drw 14

XIA XIB

9

9

18

9

18

HFB

HFA

9

DATA

WRITE (W)

FULL FLAG (FFA)

RESET (RS)

(D)

IN

READ (R)

EMPTY FLAG (EFB)

RETRANSMIT (RT)

DATA

(Q)

OUT

3208 drw 15

FIFO A FIFO B

7280/7281/7282/

7283/7284/7285