LTC2925

11

2925fd

For more information www.linear.com/LTC2925

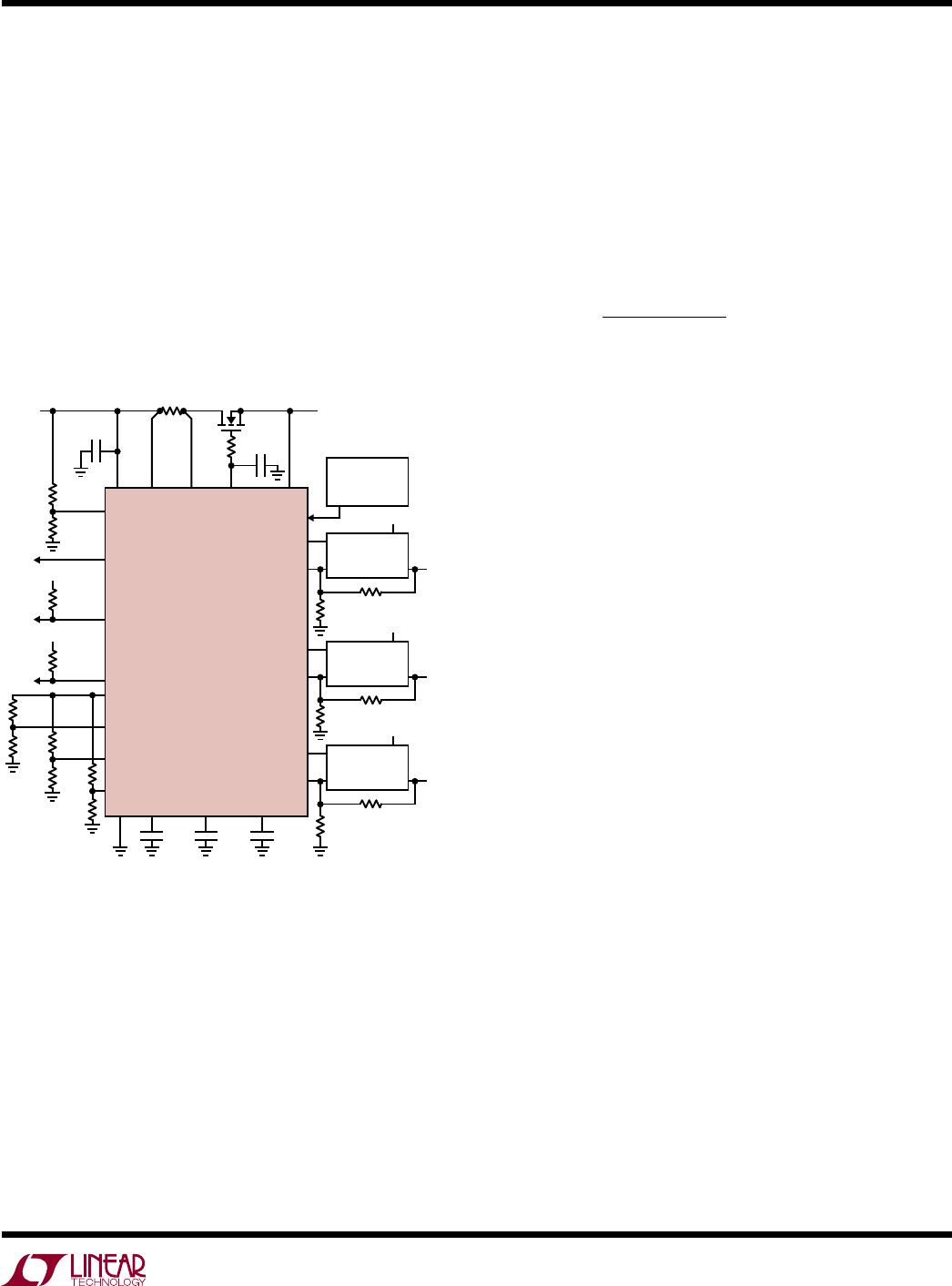

Optional External FET

Figure 7 illustrates how an optional external N-channel

FET can ramp up a single supply that becomes the mas

-

ter signal. When used, the FET’s gate is tied to the GATE

pin and its source is tied to the RAMP pin. Under normal

operation, the GATE pin sources or sinks 10µA to ramp

the FET’s gate up or down at a rate set by the external

capacitor connected to the GATE pin.

The series FET easily controls any supply with an output

voltage between 0V and V

CC

. See the Typical Applications

section for examples.

The short-circuit timer duration is configured by a capaci-

tor tied between SCTMR and GND. SCTMR will pull up

with 50µA when SENSEP

– SENSEN > 50mV. Otherwise,

it pulls down with 2µA. When the voltage at SCTMR

exceeds 1.23V, the GATE will be pulled to ground with

20mA and the FAULT pin will be pulled low. Thus, the

capacitor, C

SCTMR

, required to configure the short-circuit

timer duration, t

SCTMR

is determined from:

C

SCTMR

SCTMR

=

Because the slave supplies track the RAMP pin which

is driven by the external FET, they are pulled low by the

tracking circuit when a short-circuit fault occurs. Following

a short-circuit fault, the FET is latched off and FAULT is

pulled low until the fault is cleared by pulling the ON pin

below 0.4V. Note that the supplies will not be allowed to

ramp up again until SCTMR has been pulled below about

100mV by the 2µA pull-down current source. The electronic

circuit breaker supports any supply voltage between 0V

and V

CC

. Although it is normally used to monitor current

through the optional series FET, it is capable of monitoring

other currents, including the current from a slave supply.

The Typical Applications section shows one such example.

If the electronic circuit breaker is not used, tie SENSEP

and SENSEN to V

CC

and SCTMR to GND.

Power Good Timeout

The power good timeout circuit turns off the supplies if an

external supply monitor, connected to the PGI pin, fails to

indicate that all supplies have entered regulation in time

after power up begins. After power up is complete, it turns

off the supplies if any supply exits regulation.

The power good timer duration is configured by a capacitor

tied between PGTMR and GND. PGTMR will pull up the

CPGTMR capacitor with 10µA starting when the ON pin

is driven above 1.23V. Once the voltage at the PGTMR

exceeds 1.23V, a fault will trip if the PGI pin is low. When

the power good timeout circuit detects a fault, the GATE

applicaTions inForMaTion

SENSE

Q1

0.1µF

C

PGTMR

10k

V

CC

SENSEP SENSEN

3.3V

V

IN

3.3V

R

ONB

V

IN

R

TB1

R

TB2

R

FA2

2.5V

SLAVE2

MASTER

R

FB2

R

TA2

R

TB3

R

TA3

R

TA1

R

ONA

RAMPBUF

TRACK1

TRACK2

TRACK3

FB2

GATE

LTC2925

PGTMR

C

SDTMR

SDTMR

C

SCTMR

SCTMRGND

2925 F07

RAMP

R

FA3

1.5V

SLAVE3

R

FB3

DC/DC

IN

FB = 0.8V OUT

DC/DC

IN

FB = 0.8V

RUN/SS

RUN/SS

OUT

FB3

3.3V

PGI

R

FA1

1.8V

SLAVE1

R

FB1

SUPPLY

MONITOR

DC/DC

IN

FB = 1.235V

RUN/SS

OUT

FB1

FAULT

ON

10k

V

IN

STATUS

REMOTE

RST

SD3

SD2

SD1

C

GATE

10Ω

Figure 7. Typical Application with External FET

Electronic Circuit Breaker

The LTC2925 features an electronic circuit breaker function

that protects the optional series FET against short circuits.

An external sense resistor is used to measure the current

flowing in the FET. If the voltage across the sense resistor

exceeds 50mV for more than a short-circuit timer cycle,

the gate of the FET is pulled low with 20mA, turning it off.