UC3842A, UC3843A, UC2842A, UC2843A

http://onsemi.com

9

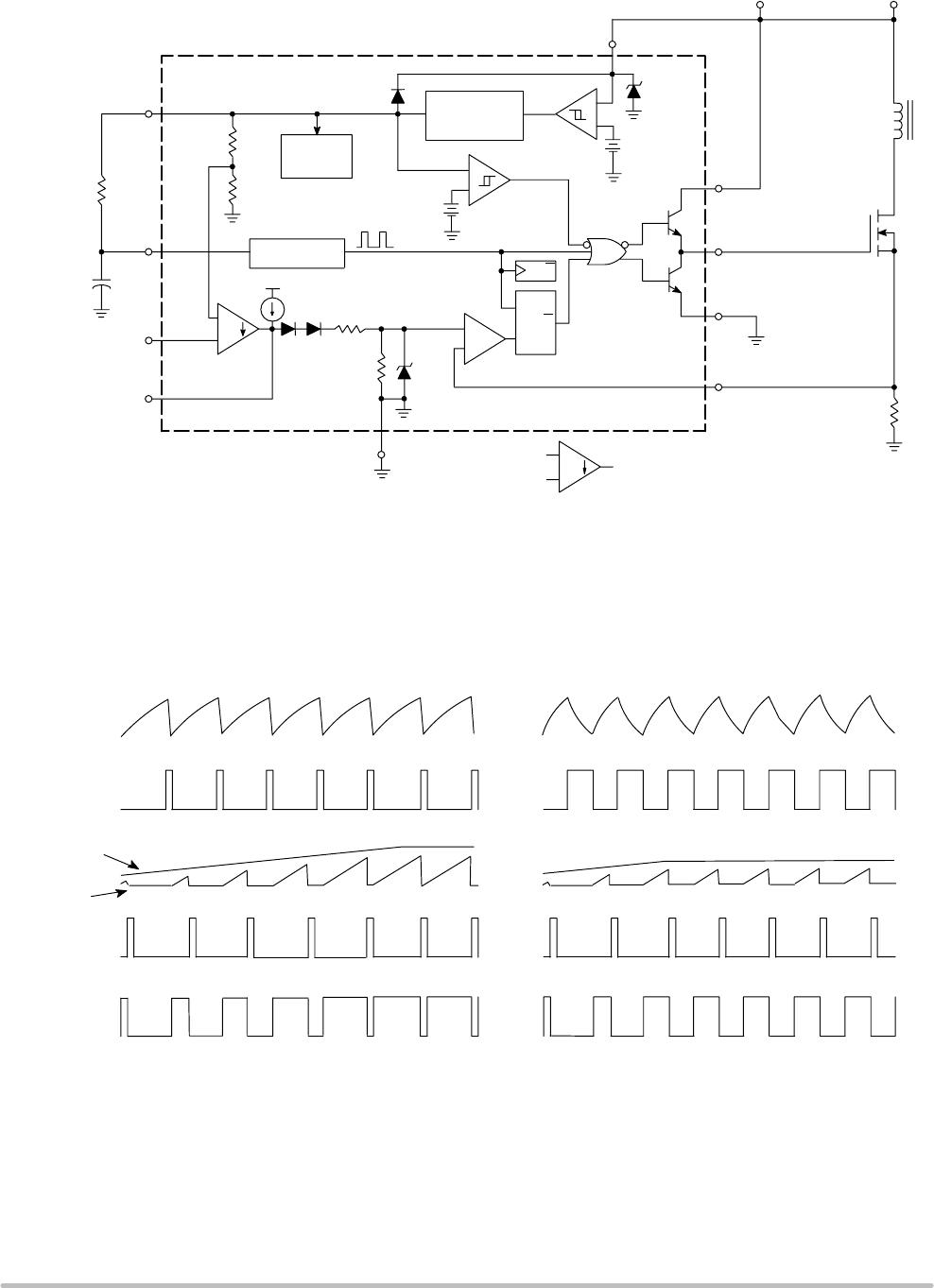

OPERATING DESCRIPTION

The UC3842A, UC3843A series are high performance,

fixed frequency, current mode controllers. They are

specifically designed for Off−Line and DC−to−DC

converter applications offering the designer a cost effective

solution with minimal external components. A

representative block diagram is shown in Figure 18.

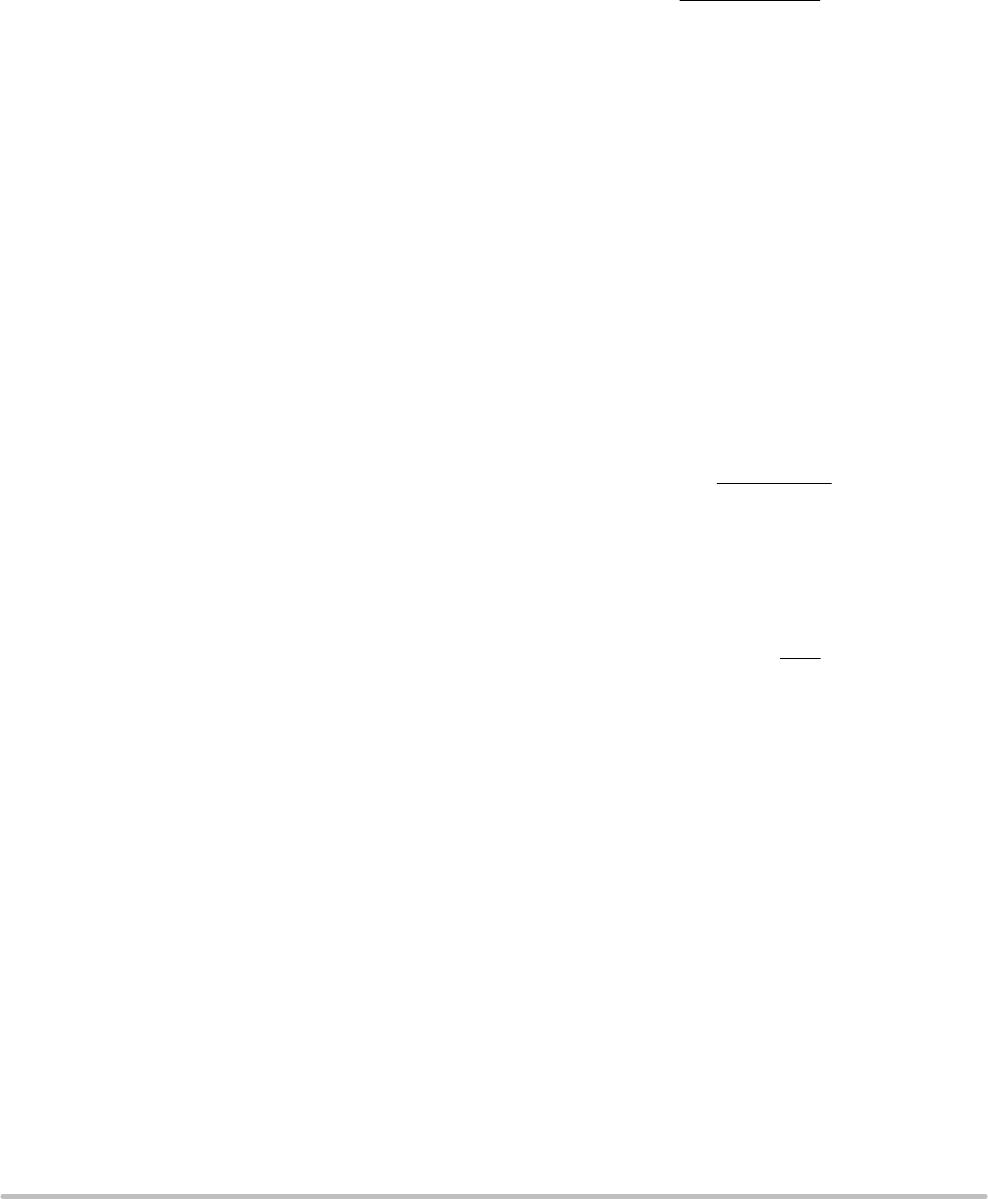

Oscillator

The oscillator frequency is programmed by the values

selected for the timing components R

T

and C

T

. Capacitor C

T

is charged from the 5.0 V reference through resistor R

T

to

approximately 2.8 V and discharged to 1.2 V by an internal

current sink. During the discharge of C

T

, the oscillator

generates and internal blanking pulse that holds the center

input of the NOR gate high. This causes the Output to be in

a low state, thus producing a controlled amount of output

deadtime. Figure 2 shows R

T

versus Oscillator Frequency

and Figure 3, Output Deadtime versus Frequency, both for

given values of C

T

. Note that many values of R

T

and C

T

will

give the same oscillator frequency but only one combination

will yield a specific output deadtime at a given frequency.

The oscillator thresholds are temperature compensated, and

the discharge current is trimmed and guaranteed to within

±10% at T

J

= 25°C. These internal circuit refinements

minimize variations of oscillator frequency and maximum

output duty cycle. The results are shown in Figures 4 and 5.

In many noise sensitive applications it may be desirable to

frequency−lock the converter to an external system clock.

This can be accomplished by applying a clock signal to the

circuit shown in Figure 21. For reliable locking, the

free−running oscillator frequency should be set about 10%

less than the clock frequency. A method for multi unit

synchronization is shown in Figure 22. By tailoring the

clock waveform, accurate Output duty cycle clamping can

be achieved.

Error Amplifier

A fully compensated Error Amplifier with access to the

inverting input and output is provided. It features a typical

dc voltage gain of 90 dB, and a unity gain bandwidth of

1.0 MHz with 57 degrees of phase margin (Figure 8). The

noninverting input is internally biased at 2.5 V and is not

pinned out. The converter output voltage is typically divided

down and monitored by the inverting input. The maximum

input bias current is −2.0 A which can cause an output

voltage error that is equal to the product of the input bias

current and the equivalent input divider source resistance.

The Error Amp Output (Pin 1) is provide for external loop

compensation (Figure 31). The output voltage is offset by

two diode drops (≈ 1.4 V) and divided by three before it

connects to the inverting input of the Current Sense

Comparator. This guarantees that no drive pulses appear at

the Output (Pin 6) when Pin 1 is at its lowest state (V

OL

).

This occurs when the power supply is operating and the load

is removed, or at the beginning of a soft−start interval

(Figures 24, 25). The Error Amp minimum feedback

resistance is limited by the amplifier’s source current

(0.5 mA) and the required output voltage (V

OH

) to reach the

comparator’s 1.0 V clamp level:

R

f(min)

≈

3.0 (1.0 V) + 1.4 V

0.5 mA

= 8800

Current Sense Comparator and PWM Latch

The UC3842A, UC3843A operate as a current mode

controller, whereby output switch conduction is initiated by

the oscillator and terminated when the peak inductor current

reaches the threshold level established by the Error

Amplifier Output/Compensation (Pin 1). Thus the error

signal controls the peak inductor current on a

cycle−by−cycle basis. The current Sense Comparator PWM

Latch configuration used ensures that only a single pulse

appears at the Output during any given oscillator cycle. The

inductor current is converted to a voltage by inserting the

ground referenced sense resistor R

S

in series with the source

of output switch Q1. This voltage is monitored by the

Current Sense Input (Pin 3) and compared a level derived

from the Error Amp Output. The peak inductor current under

normal operating conditions is controlled by the voltage at

pin 1 where:

I

pk

=

V

(Pin

1)

− 1.4 V

3 R

S

Abnormal operating conditions occur when the power

supply output is overloaded or if output voltage sensing is

lost. Under these conditions, the Current Sense Comparator

threshold will be internally clamped to 1.0 V. Therefore the

maximum peak switch current is:

I

pk(max)

=

1.0 V

R

S

When designing a high power switching regulator it

becomes desirable to reduce the internal clamp voltage in

order to keep the power dissipation of R

S

to a reasonable

level. A simple method to adjust this voltage is shown in

Figure 23. The two external diodes are used to compensate

the internal diodes yielding a constant clamp voltage over

temperature. Erratic operation due to noise pickup can result

if there is an excessive reduction of the I

pk(max)

clamp

voltage.

A narrow spike on the leading edge of the current

waveform can usually be observed and may cause the power

supply to exhibit an instability when the output is lightly

loaded. This spike is due to the power transformer

interwinding capacitance and output rectifier recovery time.

The addition of an RC filter on the Current Sense Input with

a time constant that approximates the spike duration will

usually eliminate the instability; refer to Figure 27.