6

FN6463.0

February 26, 2007

Description

Operation

Designed for versatility and speed, the PX3511D MOSFET

driver control both high-side and low-side N-Channel FETs

of a half-bridge power train from one externally provided

PWM signal.

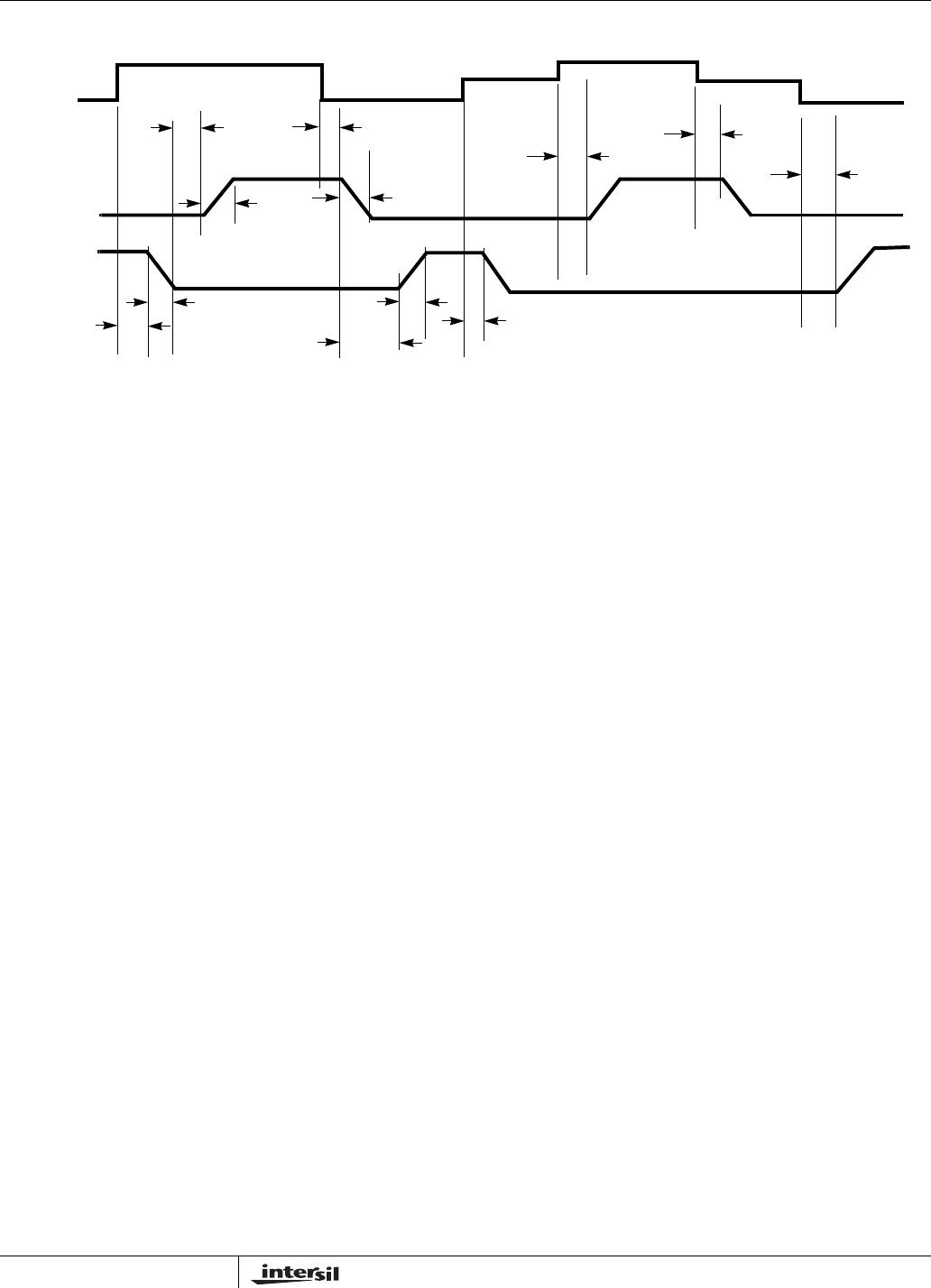

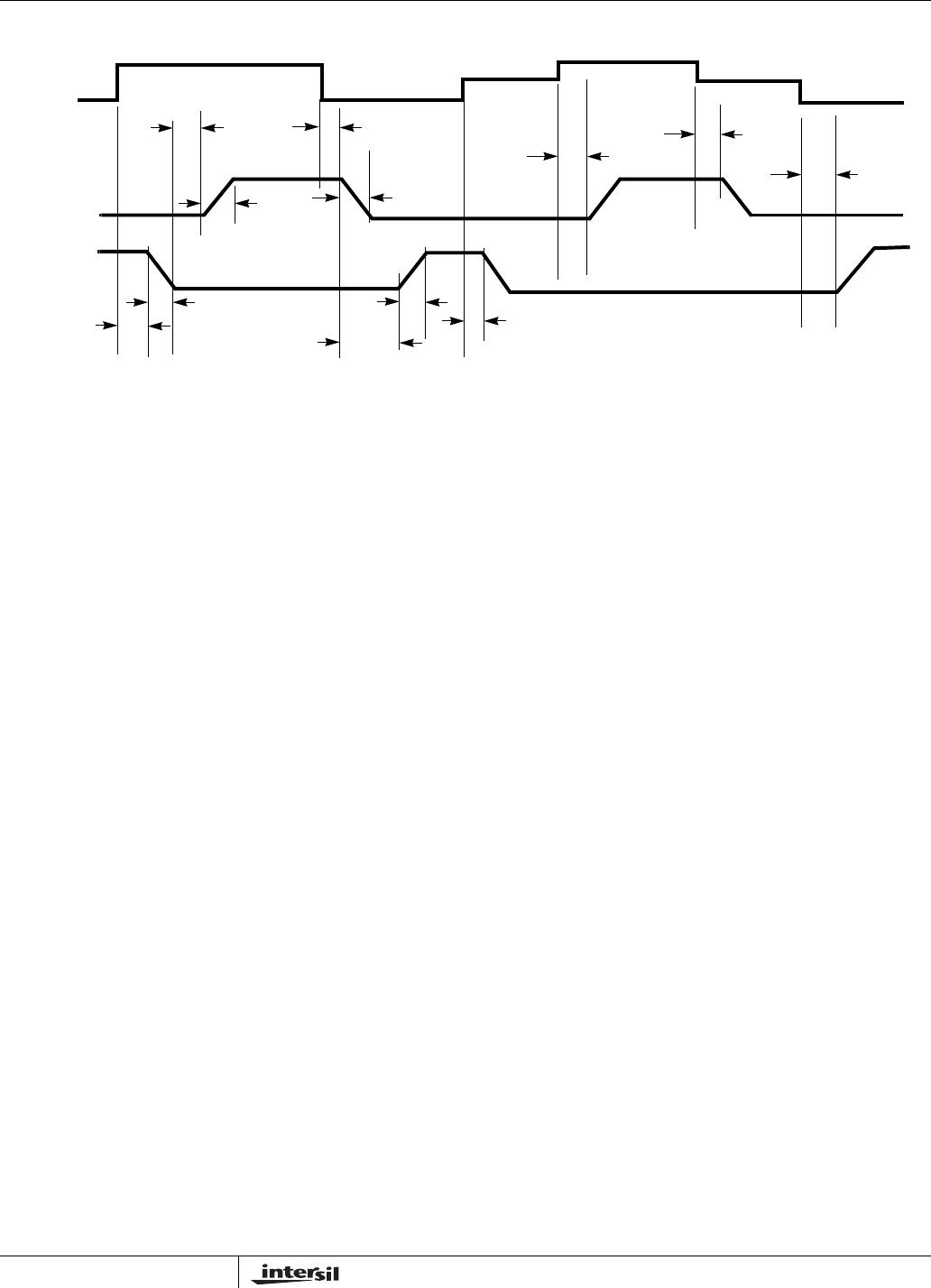

Prior to VCC exceeding its POR level, the Pre-POR

overvoltage protection function is activated during initial

startup; the upper gate (UGATE) is held low and the lower

gate (LGATE), controlled by the Pre-POR overvoltage

protection circuits, is connected to the PHASE. Once the

VCC voltage surpasses the VCC Rising Threshold (See

Electrical Specifications), the PWM signal takes control of

gate transitions. A rising edge on PWM initiates the turn-off

of the lower MOSFET (see Timing Diagram). After a short

propagation delay [t

PDLL

], the lower gate begins to fall.

Typical fall times [t

FL

] are provided in the Electrical

Specifications section. Adaptive shoot-through circuitry

monitors the LGATE voltage and determines the upper gate

delay time [t

PDHU

]. This prevents both the lower and upper

MOSFETs from conducting simultaneously. Once this delay

period is complete, the upper gate drive begins to rise [t

RU

]

and the upper MOSFET turns on.

A falling transition on PWM results in the turn-off of the

upper MOSFET and the turn-on of the lower MOSFET. A

short propagation delay [t

PDLU

] is encountered before the

upper gate begins to fall [t

FU

]. Again, the adaptive shoot-

through circuitry determines the lower gate delay time,

t

PDHL

. The PHASE voltage and the UGATE voltage are

monitored, and the lower gate is allowed to rise after PHASE

drops below a level or the voltage of UGATE to PHASE

reaches a level depending upon the current direction (See

next section for details). The lower gate then rises [t

RL

],

turning on the lower MOSFET.

Advanced Adaptive Zero Shoot-Through Deadtime

Control (Patent Pending)

The PX3511D driver incorporates a unique adaptive

deadtime control technique to minimize deadtime, resulting

in high efficiency from the reduced freewheeling time of the

lower MOSFETs’ body-diode conduction, and to prevent the

upper and lower MOSFETs from conducting simultaneously.

This is accomplished by ensuring either rising gate turns on

its MOSFET with minimum and sufficient delay after the

other has turned off.

During turn-off of the lower MOSFET, the PHASE voltage is

monitored until it reaches a -0.2V/+0.8V trip point within

15ns for a forward/reverse current, at which time the UGATE

turns on after 10ns propagation delay. An auto-zero

comparator is used to correct the r

DS(ON)

drop in the phase

voltage preventing from false detection of the -0.2V phase

level during r

DS(ON

conduction period. In the case of zero

current and/or 15ns phase detect expired, the UGATE turns

on after 10ns propagation delay. During the phase detection,

the disturbance of LGATE’s falling transition on the PHASE

node is blanked out to prevent falsely tripping. Once the

PHASE is high, the advanced adaptive shoot-through

circuitry monitors the PHASE and UGATE voltages during a

PWM falling edge and the subsequent UGATE turn-off. If

either the UGATE falls to less than 1.75V above the PHASE

or the PHASE falls to less than +0.8V, the LGATE is

released to turn on after 10ns propagation delay.

Three-State PWM Input

A unique feature of these drivers and other Intersil drivers is

the addition of a shutdown window to the PWM input. If the

PWM signal enters and remains within the shutdown window

for a set holdoff time, the driver outputs are disabled and

both MOSFET gates are pulled and held low. The shutdown

state is removed when the PWM signal moves outside the

shutdown window. Otherwise, the PWM rising and falling

PWM

UGATE

LGATE

t

FL

t

PDHU

t

PDLL

t

RL

t

TSSHD

t

PDTS

t

PDTS

1.18V<PWM<2.36V

0.76V<PWM<1.96V

t

FU

t

RU

t

PDLU

t

PDHL

t

TSSHD

FIGURE 1. TIMING DIAGRAM

PX3511D