NB3N3002

www.onsemi.com

4

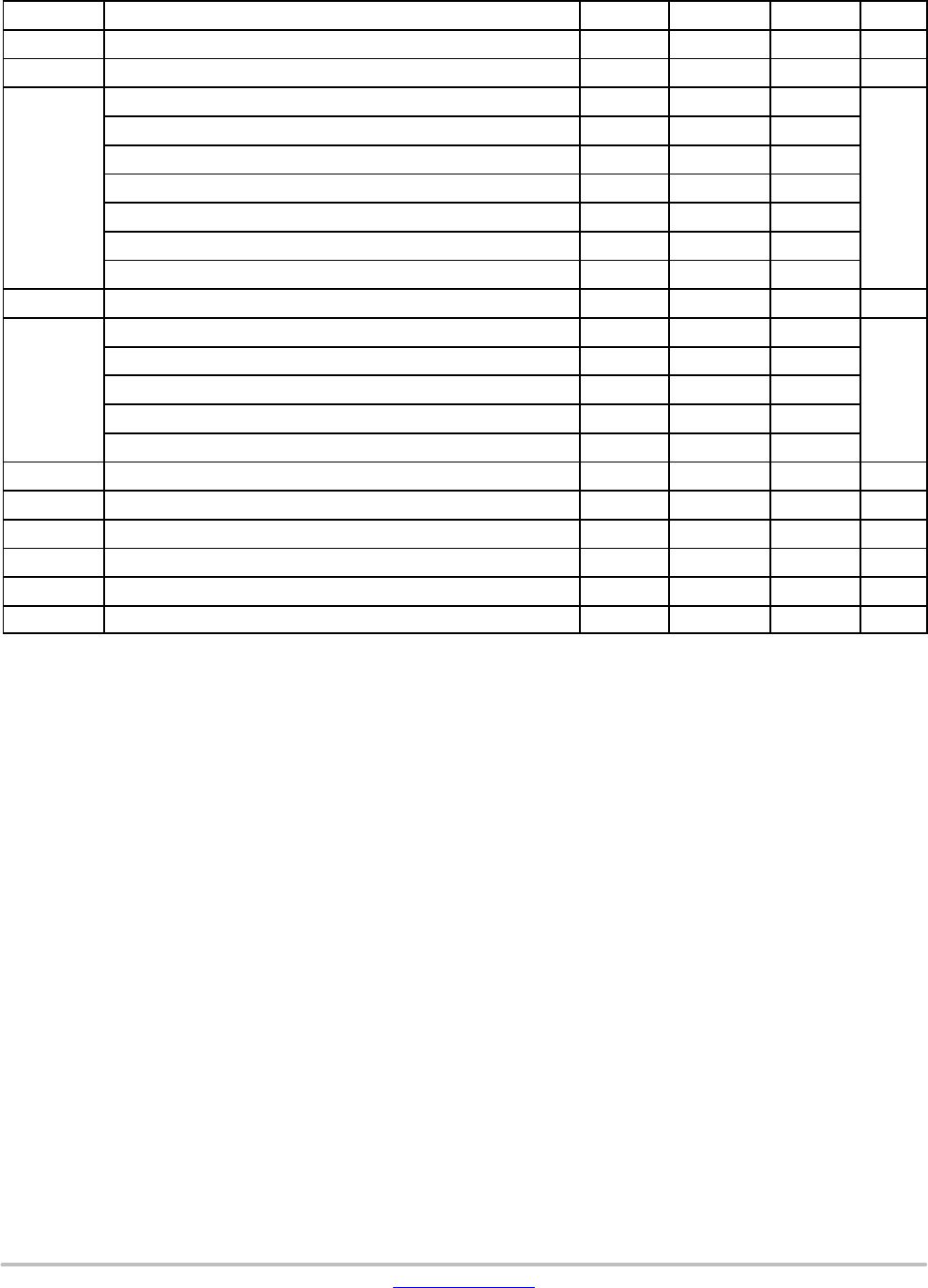

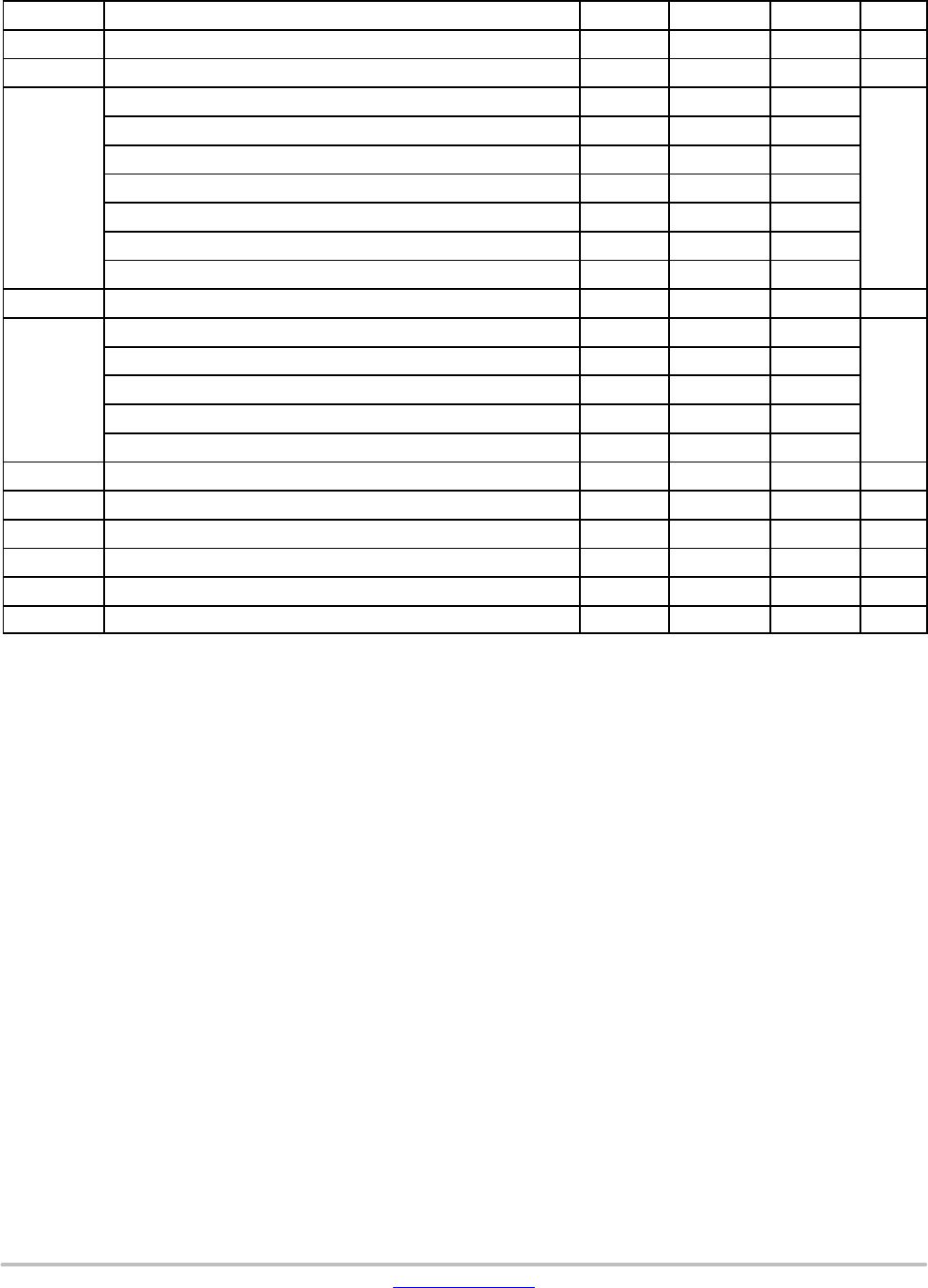

Table 6. AC CHARACTERISTICS (V

DD

= 3.3 V ±5%, GND = 0 V, T

A

= −40°C to +85°C; Note 7)

Symbol

Characteristic Min Typ Max Unit

f

CLKIN

Clock/Crystal Input Frequency 25 MHz

f

CLKOUT

Output Clock Frequency 25 200 MHz

q

NOISE

Phase−Noise Performance f

CLK

= 200 MHz/100 MHz

dBc/Hz

@ 100 Hz offset from carrier −103/−109

@ 1 kHz offset from carrier −118/−127.8

@ 10 kHz offset from carrier −122/−136.2

@ 100 kHz offset from carrier −130/−138.8

@ 1 MHz offset from carrier −138/−138.2

@ 10 MHz offset from carrier −149/−164

t

jit(

f

)

RMS Phase Jitter (at 125 MHz @ 1 MHz − 40 MHz) 0.25 0.50 ps

t

jitter

(TIE)

TIE RMS Jitter (Note 8) f

CLK

= 200 MHz 2.5

ps

Cycle−to−Cycle RMS Jitter (Note 9) f

CLK

= 200 MHz 2 5

Cycle−to−Cycle Peak to Peak Jitter (Note 9) f

CLK

= 200 MHz 20 35

Period RMS Jitter (Note 9) f

CLK

= 200 MHz 1.5 3

Period Peak−to−Peak Jitter (Note 9) f

CLK

= 200 MHz 10 20

OE Output Enable/Disable Time 1.0

ms

t

DUTY_CYCLE

Output Clock Duty Cycle (Measured at cross point) 45 50 55 %

t

R

Output Risetime (Measured from 175 mV to 525 mV, Figure 4) 175 340 700 ps

t

F

Output Falltime (Measured from 525 mV to 175 mV, Figure 4) 175 340 700 ps

Dt

R

Output Risetime Variation (Single−Ended) 125 ps

Dt

F

Output Falltime Variation (Single−Ended) 125 ps

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

6. NB3N circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit

is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.

7. Measurement taken from differential output on single−ended channel terminated with R

S

= 33.2 W, R

L

= 49.9 W, with load capacitance of

2 pF and current biasing resistor, R

REF

, from I

REF

(Pin 9) to GND of 475 W. See Figures 3 and 4.

8. Sampled with 20000 cycles to capture jitter component down to 100 kHz.

9. Sampled with 20000 cycles.