MC74HC589A

http://onsemi.com

4

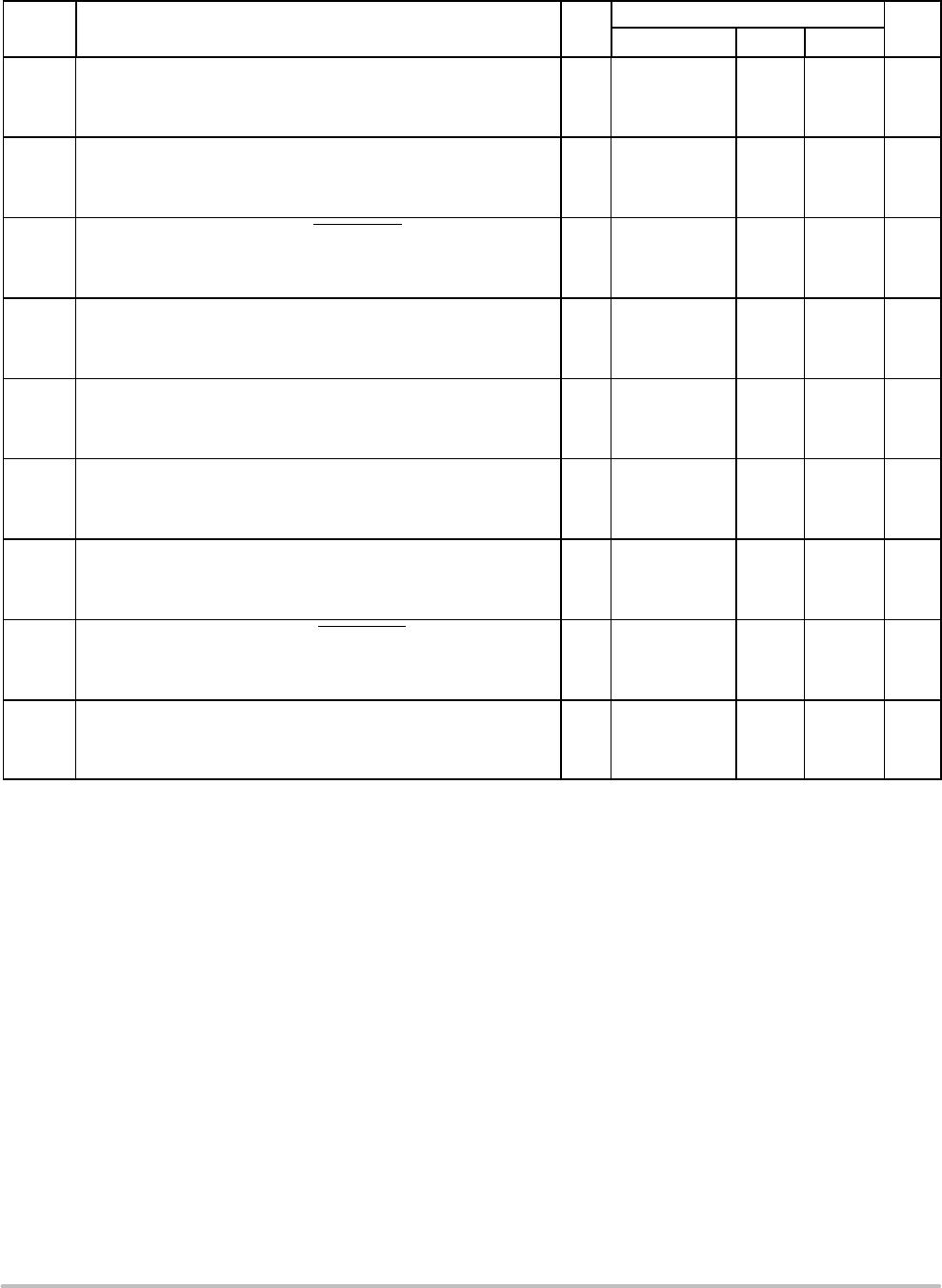

AC ELECTRICAL CHARACTERISTICS (C

L

= 50 pF, Input t

r

= t

f

= 6 ns)

V

CC

Guaranteed Limit

Symbol Parameter V

−55_C to 25_C ≤ 85_C ≤ 125_C

Unit

f

max

Maximum Clock Frequency (50% Duty Cycle)

(Figures 3 and9)

2.0

3.0

4.5

6.0

6.0

15

30

35

4.8

10

24

28

4.0

8.0

20

24

MHz

t

PLH

,

t

PHL

Maximum Propagation Delay, Latch Clock to Q

H

(Figures 2 and 9)

2.0

3.0

4.5

6.0

175

100

40

30

225

110

50

40

275

125

60

50

ns

t

PLH

,

t

PHL

Maximum Propagation Delay, Shift Clock to Q

H

(Figures 3 and 9)

2.0

3.0

4.5

6.0

160

90

30

25

200

130

40

30

240

160

48

40

ns

t

PLH

,

t

PHL

Maximum Propagation Delay, Serial Shift/Parallel Load to Q

H

(Figures 5 and 9)

2.0

3.0

4.5

6.0

160

90

30

25

200

130

40

30

240

160

48

40

ns

t

PLZ

,

t

PHZ

Maximum Propagation Delay, Output Enable to Q

H

(Figures 4 and 10)

2.0

3.0

4.5

6.0

150

80

27

23

170

100

30

25

200

130

40

30

ns

t

PZL

,

t

PZH

Maximum Propagation Delay, Output Enable to Q

H

(Figures 4 and 10)

2.0

3.0

4.5

6.0

150

80

27

23

170

100

30

25

200

130

40

30

ns

t

TLH

,

t

THL

Maximum Output Transition Time, Any Output

(Figures 2 and 9)

2.0

3.0

4.5

6.0

60

23

12

10

75

27

15

13

90

31

18

15

ns

C

in

Maximum Input Capacitance − 10 10 10 pF

C

out

Maximum Three−State Output Capacitance

(Output in High−Impedance State)

− 15 15 15 pF

Typical @ 25_C, V

CC

= 5.0 V

C

PD

Power Dissipation Capacitance (per Package)* 50 pF

*Used to determine the no−load dynamic power consumption: P

D

= C

PD

V

CC

2

f + I

CC

V

CC

.